# INSTITUT FÜR INFORMATIK UND PRAKTISCHE MATHEMATIK

WCRT Algebra and Scheduling Interfaces for Esterel-Style Synchronous Multithreading *Preliminary Report*

> Reinhard von Hanxleden Michael Mendler Claus Traulsen Bericht Nr. 0807 July 8, 2008

# CHRISTIAN-ALBRECHTS-UNIVERSITÄT

# KIEL

Institut für Informatik und Praktische Mathematik der Christian-Albrechts-Universität zu Kiel Olshausenstr. 40 D – 24098 Kiel

### WCRT Algebra and Scheduling Interfaces for Esterel-Style Synchronous Multithreading *Preliminary Report*

Reinhard von Hanxleden Michael Mendler Claus Traulsen

> Bericht Nr. 0807 July 8, 2008

E-mail: rvh@informatik.uni-kiel.de, michael.mendler@uni-bamberg.de, ctr@informatik.uni-kiel.de **Abstract.** The abstractions used in system design typically limit themselves to encapsulate and guarantee functionality, not timing. Hence, it is very difficult to transfer results on timing behavior across layers, *e. g.*, from the application level through the operating system level to the hardware level. The choice of the model of computation plays a big role in facilitating this transfer. In the realm of reactive systems, the synchronous model of computation has some appeal here, as it inherently limits the number of operations per reaction, and addresses concurrency and preemptive behavior at the language level.

Recently, reactive processing architectures have been proposed as execution platform for synchronous languages, notably Esterel. Initially, these architectures were driven by the desire for high performance with low resource usage, including low power consumption. However, by now they have also demonstrated their benefits in terms of predictability. Preliminary work on worst case reaction time (WCRT) analysis has been promising—fairly simple heuristics already achieve an accuracy typically in the 30–40% range. However, these methods so far lack formal grounding, and do not exploit knowledge about signal consistency etc. To provide a formal basis for WCRT analysis, we here propose a type-theoretic, algebraic approach. This approach not only allows to verify the correctness of WCRT analyses methods, but also opens the door for more exact analyses, as it allows to capture functionality and timing precisely and to trade off precision against analysis effort.

This approach is still under development; this report presents first results on suitable interface types and the proper characterization of instantaneous nodes, delay nodes and concurrency. As a concrete application, it builds on a multi-threaded Esterel processor, the Kiel Esterel Processor (KEP).

Key words: Worst Case Reaction Time analysis, Interface Algebra, Synchronous Languages, Esterel, Multithreading, Reactive Processing, Kiel Esterel Processor

### Table of Contents

| 1 | Introduction                                            |    |  |  |  |

|---|---------------------------------------------------------|----|--|--|--|

| 2 | Synchronicity and Timing Predictability                 |    |  |  |  |

|   | 2.1 Reactive Processing                                 |    |  |  |  |

| 3 | A Type-Theoretic Approach to WCRT Analysis              |    |  |  |  |

| 4 | Example of Esterel-style Multi-threading, KEP Assembler |    |  |  |  |

| 5 | WCRT Interfaces at Work                                 |    |  |  |  |

|   | 5.1 Introducing Interface Types                         |    |  |  |  |

|   | 5.2 Instantaneous Behavior: Transient Nodes             | 13 |  |  |  |

|   | Weaving Paths                                           | 14 |  |  |  |

|   | Weaving Nets                                            | 15 |  |  |  |

|   | Bundling Abstractions                                   | 16 |  |  |  |

|   | Data Dependency and Degrees of Precision                | 17 |  |  |  |

|   | 5.3 Sequential Behavior: Delay Nodes                    | 18 |  |  |  |

|   | 5.4 Concurrent Behavior: Fork and Join                  | 21 |  |  |  |

| 6 | Conclusion                                              |    |  |  |  |

| Α | WCRT Interface Types                                    |    |  |  |  |

| В | Multi-threading Composition                             |    |  |  |  |

|   | Multi-threading of Surface Interfaces                   | 32 |  |  |  |

|   | Multi-threading of Depth Interfaces       33            |    |  |  |  |

|   | Putting it Together: Adding Fork and Join               |    |  |  |  |

#### 1 Introduction

Reconciling performance and predictability in embedded systems is a challenge that spans all layers of hard- and software development. The use of abstraction layers, for example distinguishing the operating system (OS) layer from an application software layer above and a hardware layer below, is fundamental to computer science. However, as observed by Edwards and Lee [1], these abstractions typically limit themselves to encapsulate and guarantee functionality, not timing. Hence, even though there is a significant body of work that addresses predictability at different abstraction layers, considering for example schedulability, worst case execution times (WCET), or circuit timing, it is very difficult to transfer results across layers. However, end users are not interested in results that apply only to one layer—they care about timing guarantees for complete systems.

The choice of the model of computation—and its model of time—has a profound influence on how easy or difficult it is to provide timing guarantees across abstraction layers. From the predictability point of view, a very appealing candidate in the embedded systems domain is the synchronous model of computation [2]. This model supports deterministic timing in several ways, as further argued in Section 2. Furthermore, languages built on that model generally have a wellestablished formal semantics that allows reasoning about functional as well as timing properties from the ground up. In this paper, we first give an overview on how the synchronous model together with a suitable execution platform can provide system-level timing predictability, and we illustrate this with the case of multi-threaded execution of Esterel-style synchronous programs. The main contribution of this paper then is the introduction if an algebraic framework for precisely capturing WCRT characteristics for this execution approach.

#### 2 Synchronicity and Timing Predictability

The synchronous model of computation divides physical time into a sequence of discrete ticks. or *instants*. The abstraction is that at each tick, outputs are synchronous with the inputs. In other words, computations take place instantaneously, interspersed with durations of inactivity between ticks. Synchronous languages generally do not permit unbounded computations within a tick. For example, the language Esterel provides a loop construct [3], but each loop iteration must include at least one tick-delimiting instruction, and the compiler must be able to verify this. This simplifies the problem of determining the maximal number of instructions per tick, which leads to the worst case reaction time (WCRT). The situation is quite different for classical imperative languages such as Java or C, which permit unbounded loops and unbounded recursion, and thus only language subsets (e. g., with statically bounded loop iterations) are amenable to WCET analyses. Another helpful characteristic of (strict) synchrony is that the statuses of signals, which are basic communication means in synchronous programs, evolve monotonically. In other words, there can be no oscillations between signal presence and absence, thus guaranteeing convergence after a finite number of computations. This contrasts, for example, with Harel's original Statecharts dialect [4], which assumes a weaker (non-strict) form of synchrony in which computations are also assumed to not consume any time, but signal statuses are allowed to oscillate and computations within a tick are unbounded. Finally, the synchronous paradigm also supports concurrent and preemptive control flow, with a deterministic semantics regarding both functionality and timing characteristics. This again contrasts with classical imperative languages, which either do not support non-sequential control flow at all (e. g., C relegates this to the OS level, subject to run-time scheduling decisions), or support it only in a rather haphazard fashion (e. q., Java threads [5]).

#### 2.1 Reactive Processing

Synchronous programs may be compiled into hardware or software. The traditional software design flow is to first compile the synchronous program into a classical imperative language, such as C, and to compile and run the resulting program on a standard micro processor [6]. This approach preserves the nice semantical properties of synchronous programs at a functional level. The timing properties, however, are only partially preserved with this approach. Computations are still finite per tick, and the synthesized C-code should not have unbounded loops, for example. However, depending on the synthesis approach used, the control flow may still be rather complex and difficult to analyze (for example, computed gotos). Furthermore, standard processors typically employ various techniques that improve average execution time, at the expense of worst case execution time and predictability [7].

An alternative, more recent approach for executing synchronous programs is to run them on processors that directly support reactive control flow. This *reactive processing* approach builds on instruction set architectures (ISAs) that can express concurrency and preemption and preserve functional determinism [8]. There have been various proposals on how to support concurrency in reactive processing, including sequentialization [9], parallel execution [10], and, most recently, multi-threading [11, 12]. The latter one appears to be the most effective at this point, and significantly outperforms classical software-based execution strategies while using minimal resources.

In the multi-threaded reactive processing approach, a combination of static scheduling, hardwaresupported context switching, and fixed machine instruction execution times assures timing determinism. This has been exploited in a compiler which translates Esterel programs into multithreaded assembler code, and as part of the compilation process analyzes the WCRT in terms of instruction cycles [13]. The assembler code is then annotated with this WCRT, which at run time configures a hardware unit, the TickManager, which provides timing stability at the logical tick level [14]. This decouples physical system reaction times from the tick-specific computation requirements, which is for example desirable for control loop stability. Note that, as an alternative, one may still choose not to make use of the TickManager and instead let the processor run freely, *i. e.*, start the next tick as soon as the current tick finishes. This can improve average case performance, at the expense of reaction time jitter and possibly higher power requirements. Furthermore, our experiments indicate that there is no dramatic difference between WCRT and average case reaction time (ACRT)—typically a factor of around 1.5 [13].

The WCRT analysis technique developed so far does already provide fairly promising results. A relatively simple heuristics provides an accuracy typically in the 30–40% range [13]. However, this heuristics still makes conservative and simplifying assumptions, and is not grounded in a formal timing model. We believe that such a formal model will be instrumental in the further development of these techniques to cover different processing platforms and several levels of abstraction between hardware and software layers. A semantically grounded notion of WCRT interface types will be crucial to make our techniques scale up to industrial-sized systems without losing tight control of correctness and exactness of WCRT analysis. In this paper we take first steps towards such an interface model.

#### 3 A Type-Theoretic Approach to WCRT Analysis

Imperative synchronous programming as exemplified in Esterel, Statecharts provide predictability in terms of determinism and bounded reaction in the face of powerful language constructs for concurrency, state hierarchy, priorities, strong and weak preemption. These constructs induce sophisticated control dependencies so that WCRT analysis for such languages and processors that directly support them is non-trivial. The risk of over- and under-approximations jeopardizes the quality of WCRT analysis and thus creates a conflict between performance and predictability.

Combining performance with predictability involves a trade-off between analysis time and execution time. Optimizations in the efficiency of timing analysis are paid for by compromising the quality of timing results. Under-approximations may result in a loss of coverage and over-approximations in a loss of exactness. Thus, the system under analysis (SUA) becomes less predictable or runs at slower (virtual) clock speed. Optimizations in speed and predictability of the SUA, on the other hand, require sophisticated data-dependent analysis which are computationally expensive. This creates a direct conflict with the performance and predictability of the WCRT algorithms themselves. To strike this trade-off a scalable and modular approach towards timing analysis is called for in which precision and efficiency can be adjusted systematically in wide margins. The existing WCRT algorithms such as [13] are neither compositional nor scalable in terms of precision. They are global analyses on the complete control-flow graph of a monolithic program. Also they run at the ground level of atomic program statements rather than hierarchical subsystems. In this paper we propose a theory of WCRT interfaces for synchronous programming and show how it can be employed to obtain type-directed and modular WCRT analyses which

- give precise statements about exactness and coverage of timing values, supporting a variety

of timing abstractions;

- are dedicated to express the implicit control flow of imperative synchronous programming languages;

- are scalable across component hierarchies and the software-hardware abstraction boundary.

As an interface theory our WCRT algebra operates on matrices of delay values characterizing whole sub-systems rather than individual nodes like existing graph-theoretic WCRT algorithms do. It combines max-plus algebra  $(\mathbb{N}, max, +, 0, -\infty)$ , see e.g. [15], with Boolean logic<sup>1</sup> to reason about implicit control-flow.

The key element of WCRT analysis is the interchange (distribution) of max and +. In its simplest form, the WCRT is the maximum of all sums of paths delays, an expression of the form  $max(\sum_{i \in p_1} d_{i1}, \sum_{i \in p_2} d_{i2}, \dots, \sum_{i \in p_n} d_{in})$  where  $p_j$  are execution paths of the system and  $d_{ij}$  the delay of path segment *i* in path  $p_j$ . However, the number *n* of paths is exponential in the number of elementary nodes of a system. Practicable WCRT analyses therefore reduce the maxof-sums to the polynomial complexity of sum-of-maxs employing various forms of dependency abstraction. Unfortunately, the obvious distribution of  $max(d_1 + e_1, d_1 + e_2, d_2 + e_1, d_2 + e_2) =$  $max(d_1, d_2) + max(e_1, e_2)$  is exact only if we have a full set of path combinations. In general, there will be dependencies ruling out certain paths, in which case we only get conservative over-approximations, e.g.,  $max(d_1, d_2) + max(e_1, e_2) \ge max(d_1 + e_1, d_2 + e_1, d_2 + e_2)$ . On the other hand,  $max(d_1 + e_1, d_2 + max(e_1, e_2)) = max(d_1 + e_1, d_2 + e_1, d_2 + e_2)$  which eliminates one addition operation, does work in this case. The art of WCRT analysis consists in finding a judicious trade-off between forming the maximum operation early in order to aggregate data and refining dependency paths for the sake of exactness. A practicable WCRT algebra must be able to express and control this trade-off. In Sec. 5.1 we sketch a type theory which achieves this by coupling timing delays d with logic formulas  $\phi$ . A pair d :  $\phi$  specifies the semantical meaning of d within the control-flow of a program. Logical operations on the formulas then go hand-in-hand with arithmetic operations on timing. E.g., suppose a schedule activates control points X and Ywith a delay of  $d_1$  and  $d_2$  instruction cycles. If they are independent then both control points are jointly active within the maximum of both delays, i.e.,  $(d_1:X) \wedge (d_2:Y) \cong (max(d_1, d_2):X \wedge Y)$ . On the other hand, if reaching Y is causally dependent on having reached X first then we must take addition, i.e.,  $(d_1: X) \land (X \supset (d_2: Y)) \cong (d_1 + d_2: X \land Y)$  where  $\land, \supset$  are logical conjunction and implication, respectively. Thus, in general, the computation of paths involves functional analysis of implicit control-flow using logic reasoning rather than just following pointers in a graph (of explicit dependencies). We will illustrate this in Secs. 5.2–5.4 below by way of an extended example.

The idea of modularizing embedded systems programming and specifically synchronous programming using interfaces is not new. Mostly these interface models focus on causality issues, which amounts to dependency analysis without quantitative time. On the other hand, there exist numerous approaches to classical WCET analysis [16] but only few on WCRT analysis [14].

Logothetis, Schneider and Metzler [17, 18] have employed model checking to perform a precise timing analysis for the synchronous language Quartz, which is similar to Esterel. However, their problem is WCET since they are interested in computing the number of logical ticks required to perform a certain transformational computation, such as a primality test. Instead, in reactive system WCRT one considers how long it may take to compute a single logical tick. WCRT is an orthogonal issue to WCET and has been rarely investigated in the literature so far.

André *et al.* [19] employ a causally simple notion of module in the sense that no instantaneous interaction between modules is permitted. Such a model is not suitable for WCRT. Hainque et

<sup>&</sup>lt;sup>1</sup> To be more precise, we use a finite-valued Heyting algebra in which  $A \vee \neg A$  is not a tautology. This difference, however, is not essential for this paper.

al. [20] use a topological abstraction of the underlying circuit graphs (or syntactic structure of Boolean equations) to derive a fairly rigid component dependency model. A component is assumed executable iff all of its inputs are available; after component execution all of its outputs become defined. The former restriction means that single-threaded execution cannot be modeled compositionally. The interface model also does not cover data dependency and thus cannot deal with dynamic schedules and does not support WCRT, either.

The causality interfaces of Lee *et al.* [21] are more flexible. These are functions  $\delta: P_i \times P_o \to D$ associating with every pair  $(i, o) \in P_i \times P_o$  of input and output ports an element  $\delta(i, o) \in D$  of a *dependency domain* D, which expresses if and how an output o depends on input i. The domain D is a linearly ordered dioid structure  $(D, 0, 1, \otimes, \oplus, <)$ , where  $\otimes$  models *sequential composition* and  $\oplus$  is the *parallel* composition of dependencies, with neutral elements 0 and 1, respectively. Causality analysis is then performed by multiplication on the global system matrix describing the dependencies between any two signals. Using an appropriate dioid structure D, one can perform the analyses of [20] as well as restricted forms of WCRT. However, Lee's interfaces cannot express the difference between an output depending on the joint presence of several values as opposed to depending on each input individually. In other words, they do not support full AND- and OR-type synchronization dependencies and hence cannot represent neither multi-threading nor multi-processing. The work reported here can be seen as an extension of Lee's to address these deficiencies.

Similar restrictions apply to recent work [22, 23] combining network calculus [15, 24] with real-time interfaces in which sequential connection and concurrent composition operators play an analogous role to Lee's sequential and parallel composition, respectively. On top of that, these works are concerned with the compositional modeling of regular execution patterns rather than stabilization processes that make up the components inside each execution cycle of a synchronous program. Existing interface theories [21-23], which aim at the verification of resource constraints for real-time scheduling, handle rather delicate timing properties such as task execution latency, arrival rates, resource utilization, throughput, accumulated cost of context switches, and so on. On the other hand, in those works, the dependency on data and control flow is largely abstracted. For instance, since the task sequences of Henzinger and Matic [23] are independent of each other, their interfaces do not model concurrent forking and joining of threads. The causality expressible there is even more restricted than that by Lee *et al.* [21] in that it permits only one-to-one associations of inputs with outputs. The interfaces of Wandeler and Thiele [22] for modular performance analysis in real-time calculus are like those of Henzinger and Matic [23] but without sequential composition of tasks and thus do not model control flow.

AND- and OR-type synchronization dependencies are important for WCRT in synchronous programming since reachability of control nodes in general depends both conjunctively and disjunctively on the presence of data. Moreover, execution may depend on the absence of data (negative triggering conditions), which makes compositional modeling rather a delicate matter in the presence of logical feedback loops. This severely limits the applicability of existing interface models. The assume-guarantee style specification [22, 23] does not address causality issues arising from feedback and negative triggering conditions. The interface automata of Alfaro, Henzinger, Lee, Xiong [25, 26] model synchronous macro-states and assume that all stabilization processes (sequences of micro-states) can be abstracted into atomic interaction labels. The introduction of transient states [27] alleviates this to some extent, but the focus is still on regular (scheduling) behavior. The situation is different, however, for cyclic systems, in which causality information is needed. The interface problem in WCRT for stabilization processes is quite a different game—it is simpler and more complex at the same time. It is simpler since we do not need sophisticated resource and timing models; in a stabilization process the only resource is time—here instruction cycles—which is only consumed once rather than in a regular pattern. It is more complex since we need to model more sophisticated synchronization effects and solve causality and full-abstraction problems due to feedback and negative dependencies. Because of the complications arising from causality issues, there is currently no robust component model for imperative synchronous programming.

Before we move on introducing our approach in the next section let us add a couple of general remarks on our philosophy. Our approach to WCRT is specification-oriented and type-theoretic. The idea we wish to stress is that timing does not have any meaning without at the same time specifying the functional behavior to which the timing information is attached. Without function, timing are just numbers signifying nothing. Working with (matrices of) numbers alone makes is easy to lose track of semantical correctness and exactness and thus the connection between performance and predictability. For illustration consider the following analogy: Imagine we are given a full blueprint of all layers (metal, poly-silicon, etc.) of a VLSI solid-state circuit. We know all its physical parameters and could simulate and fabricate the circuit. Yet, we would not be able to sensibly tell what its timing is without knowing what the inputs and outputs are and what function the circuit is supposed to execute. So just as correct functionality depends on timing, correct timing depends on functionality. By using the type-theoretic structure f:  $\phi$  we bring out both the separation and the intimate coupling of scheduling bounds f and scheduling types  $\phi$ . The scheduling shape  $\phi$  acts as a type specification for timing matrix f making clear the semantical meaning of f and the scheduling bound f in turn acts as a quantitative implementation of the schedule  $\phi$ . We believe that type theory seen as an extension of algebra provides a powerful framework for coupling functional and non-functional specifications that has not yet been exploited to its full potential.

#### 4 Example of Esterel-style Multi-threading, KEP Assembler

Esterel [3] programs communicate with the environment and internally via signals, which are either present or absent during one instant. Signals are set present by the emit statement and tested with the present test. They are reset at the start of each instant. Esterel statements can be either combined in sequence (;) or in parallel (||). The loop statement simply restarts its body when it terminates. All Esterel statements are considered instantaneous, except for the pause statement, which pauses for one instant, and derived statements like halt=loop pause, which stops forever. Esterel supports multiple forms of preemption, *e. g.*, via the abort statement, which simply terminates its body when some trigger signal is present. Abortion can be either weak or strong. Weak abortion permits the execution of its body in the instant the trigger signal becomes active, strong abortion does not. Both kinds of abortions can be either immediate or delayed. The immediate version already senses for the trigger signal in the instant its body is entered, while the delayed version ignores it during the first instant in which the abort body is started.

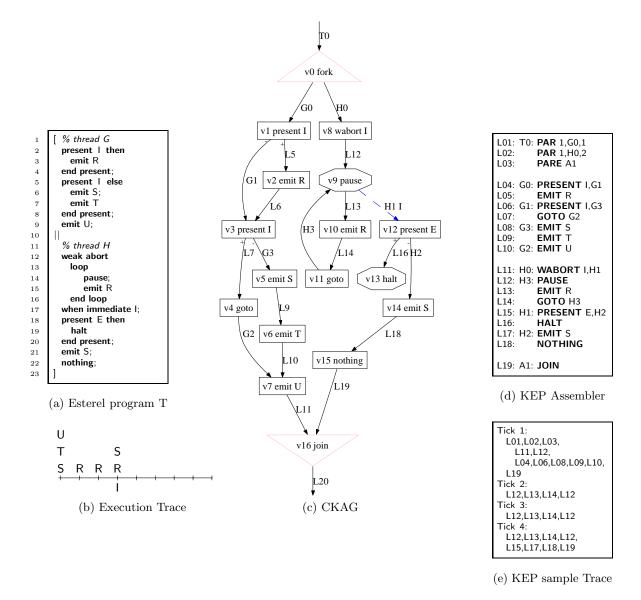

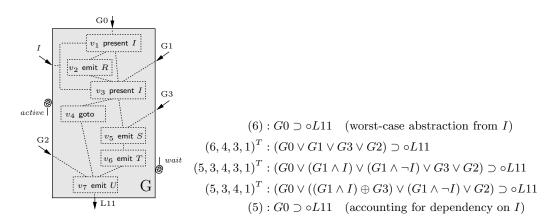

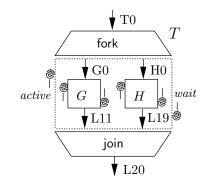

Consider the Esterel fragment in Figure 1a. It consists of two threads. The first thread (G) emits signals R, S, T depending on some input signal I. In any case, it emits signal U and terminates instantaneously. The thread (H) continuously emits signal R, until signal I occurs. Thereafter, it either halts, when E is present, or emits S and terminates otherwise.

The main problems when executing Esterel on standard processors are the handling of preemption and synchronous parallelism. The Kiel Esterel Processor (KEP) [11] handles abortion by watchers, which are executed in parallel with their body and simply set the program-counter when the trigger signal becomes present. Synchronous parallelism is executed by multi-threading. The KEP manages multiple threads, each with their own program counter and a priority. In each instruction cycle, the processors determines the active instruction from the thread with the highest priority and executes it. New (sub-)threads are initialized by the PAR instruction. The PARE instruction ends the initialization of parallel threads and sets the program counter of the current thread to the corresponding join. By changing the priorities of the threads, arbitrary interleavings can be specified; the compiler has to ensure that the priorities respect all signal dependencies, *i. e.*, all possible emits of a signal are performed before any testings of the signal. The specific interleavings are not relevant for the WCRT analysis under multi-threading. Therefore, priority changing instructions may be treated like the padding statement nothing which has no effect on the system state other than adding a time delay. Additionally, for all parallel threads one join instruction is executed, which checks whether all threads have terminated in the current instant. If this is the case, the whole parallel terminates and the join transforms the control to the next instruction. Otherwise the join blocks. Instructions pause and halt end the execution for the current instant, the execution is resumed from the same point in the next instant.

Most instructions, like emit or entering an abort block, are executed in exactly one instruction cycle. The pause instruction is executed both in the instant it is entered, and in the instant it is resumed, to check for weak and strong abortions, respectively. Note that the halt instruction

Fig. 1: A simple Esterel program T with its corresponding control-flow graph and the resulting KEP Assembler

is executed in one cycle. While halt and loop pause are functionally equivalent, their execution times differ. The latter has a worst case reaction time (WCRT) of 3 instruction cycles (ics) while the former only needs 1 ic.

The concurrent KEP assembler graph (CKAG, see Fig. 1c) captures the control flow, both standard control and abortions, of an Esterel program. We distinguish two kinds of edges, instantaneous and non-instantaneous. Instantaneous edges can be taken immediately when the source node is entered, they reflect control flow starting from instantaneous statements or weak abortions of delayed statements. Non-instantaneous edges can only be taken in an instant where the control started in its source node, like control flow from **pause** statements or strong abortions. The CKAG can be derived from the Esterel program by structural translation. For a given CKAG, the generation of KEP Assembler is straight-forward (see Fig. 1c). Most nodes are translated into one instruction, only fork nodes are expanded to multiple instructions to initialize the threads. In our example, the fork v0 is transformed into three instructions (L01 - L03).

#### 5 WCRT Interfaces at Work

The WCRT of an Esterel program is the maximal number of instructions that are executed during one instant. WCRT differs from WCET fundamentally in that it deals with the timing of *stabilization* rather than *iteration* processes. WCRT assumes that all dependencies in the control flow are acyclic and the propagation of control is a monotonic process in which each atomic control point is only ever executed at most once. On the other hand, WCRT for Esterel-style synchronous processing must handle *non-atomic control flow* including features such as hierarchical and concurrent threads, priorities and preemption. In the following we sketch the basic elements of WCRT for synchronous processing and develop an algebra for modular timing analyses. This algebra is an extension and adaptation of the *intuitionistic propositional stabilization theory* presented in [28].

#### 5.1 Introducing Interface Types

An execution  $\sigma$  is a finite and monotonically increasing sequence  $\sigma = \emptyset \subseteq \sigma(0) \subseteq \sigma(1) \subseteq \sigma(2) \subseteq \cdots \subseteq \sigma(n-1)$  of sets of control signals  $\sigma(i) \subseteq \mathbb{S}$   $(0 \leq i < |\sigma| = n)$  called events. This includes the special case n = 0 of the empty execution  $\sigma = \emptyset$ . For all executions, empty or not, we refer to the initial  $\emptyset$  as  $\sigma(-\infty)$ . Signals  $\mathbb{S}$  contain the control-flow labels as well as input and output signals of the program. E.g. for the program in Fig. 1c  $\{L0 - L20, G0 - G3, H0 - H3, I, E, R, S, T, U\} \subseteq \mathbb{S}$ . We will also need activation controls  $active(v) \in \mathbb{S}$  for nodes v in the hierarchical decomposition of the program. An execution  $\sigma$  models the micro-sequence of instruction cycles (ic) which are executed within a single synchronous instant. Each step  $\sigma(i) \mapsto \sigma(i+1)$  records the change of controls between two successive activations of the thread. Accordingly, the number of instructions executed by  $\sigma$  is the number of changes or steps  $|\sigma| - 1$  rather than the number of events.

Example 1. One possible execution of the program T in Fig. 1c would be as follows. Initially, control signal T0 is set, so  $\sigma(0) = \{T0\}$ . Then the PAR and PARE instructions making up the fork node  $v_0$  are executed in line numbers L01, L02, L03 each taking one ic. The two PAR instructions set up internal counters for thread control, which does not change the set of events in the signals of Fig. 1c, which are the signals that we are interested in. Hence,  $\sigma(1) = \sigma(2) = \{T0\}$ . However, after the PARE both control signals G0, H0 become present bringing threads G and H to life. This means  $\sigma(3) = \{T0, G0, H0\}$ . The next instruction could be any of the two first instructions of G or H. As it happens, the KEP Assembler Fig. 1d assigns higher priority to H so that our execution continues with wabort (node  $v_8$ ), i.e.,  $\sigma(4) = \{T0, G0, H0, L12\}$ . This brings up the pause instruction  $v_9$ . Now, depending on whether signal I is present or not the execution of pause either moves to  $v_{12}$  (weak immediate abort) or terminates. Let us assume the latter, i.e.,  $\sigma(5) = \{T0, G0, H0, L12\}$  which is the same set as  $\sigma(4)$  but now thread H is finished up for the instant and has entered an implicitly wait state. The execution continues with the first instruction of G, the present node  $v_1$  at label G0. Since I is assumed absent, its execution effects a jump to label G1, i.e.,  $\sigma(6) = \{T0, G0, H0, L12, G1\}$ . Thereafter, we run sequentially through nodes  $v_3, v_5, v_6, v_7$  giving  $\sigma(7) = \{T0, G0, H0, L12, G1, G3\}, \sigma(8) = \{T0, G0, H0, L12, G1, G3, L9\}, \sigma(8) = \{T0, G0, H0, L12, G1, G3, L9\}, \sigma(8) = \{T0, G0, H0, L12, G1, G3, L9\}, \sigma(8) = \{T0, G0, H0, L12, G1, G3, L9\}, \sigma(8) = \{T0, G0, H0, L12, G1, G3, L9\}, \sigma(8) = \{T0, G0, H0, L12, G1, G3, L9\}, \sigma(8) = \{T0, G0, H0, L12, G1, G3, L9\}, \sigma(8) = \{T0, G0, H0, L12, G1, G3, L9\}, \sigma(8) = \{T0, G0, H0, L12, G1, G3, L9\}, \sigma(8) = \{T0, G0, H0, L12, G1, G3, L9\}, \sigma(8) = \{T0, G0, H0, L12, G1, G3, L9\}, \sigma(8) = \{T0, G0, H0, L12, G1, G3, L9\}, \sigma(8) = \{T0, G0, H0, L12, G1, G3, L9\}, \sigma(8) = \{T0, G0, H0, L12, G1, G3, L9\}, \sigma(8) = \{T0, G0, H0, L12, G1, G3, L9\}, \sigma(8) = \{T0, G0, H0, L12, G1, G3, L9\}, \sigma(8) = \{T0, G0, H0, L12, G1, G3, L9\}, \sigma(8) = \{T0, G0, H0, L12, G1, G3, L9\}, \sigma(8) = \{T0, G0, H0, L12, G1, G3, L9\}, \sigma(8) = \{T0, G0, H0, L12, G1, G3, L9\}, \sigma(8) = \{T0, G0, H0, L12, G1, G3, L9\}, \sigma(8) = \{T0, G0, H0, L12, G1, G3, L9\}, \sigma(8) = \{T0, G0, H0, L12, G1, H0, L12, H1, H1, H1, H1, H1, H1, H1, H1, H1, H$  $\sigma(9) = \{T0, G0, H0, L12, G1, G3, L9, L10\}$ . Executing the final emit instruction  $v_7$  hits the join at entry L11, so that  $\sigma(10) = \{T0, G0, H0, L12, G1, G3, L9, L10, L11\}$ . Now both threads G and H are finished. It takes one execution step of the join node  $v_{16}$  to detect this and to terminate the synchronous instant of T with the final event  $\sigma(11) = \{T0, G0, H0, L12, G1, G3, L9, L10, L11\}$ . Overall, we get an execution  $\sigma = \sigma(0)\sigma(1)\cdots\sigma(11)$  of the outer-most main thread of T from T0 consisting of 11 instruction cycles.

Note that signal L19 is not included in the last event  $\sigma(11)$  because control remains inside the pause node  $v_9$  of T. Only in the next logical instant when T is resumed in  $v_9$  and thread Heventually comes out at control point L19 (if signal I is present and E absent), then executing the join  $v_{16}$  will bring us to control point L19 and out of T instantaneously.

Note further that the difference  $\Delta_i = \sigma(i+1) \setminus \sigma(i)$  may be an arbitrary subset of S. It may be empty as with  $i \in \{1, 4, 10\}$ , contain exactly one control as for  $i \in \{3, 5, 6, 7, 8, 9\}$  or more as in i = 2. In general,  $\Delta_i$  will encompass more than one signal when a thread forks into concurrent sub-threads or if other concurrent threads get executed between the two activations i and i + 1of the thread represented by  $\sigma$ . A set of executions S defines a schedule. The possible schedules of a program will be specified by a scheduling type  $\phi$  generated by the language

$\phi ::= A \mid true \mid false \mid \phi \land \phi \mid \neg \phi \mid \phi \supset \phi \mid \phi \lor \phi \mid \phi \oplus \phi \mid \phi \parallel \phi \mid \circ \phi.$

We write  $S \models \phi$  ( $\sigma \models \phi$ ) to say that schedule S (execution  $\sigma$ ) validates the type  $\phi$ . As a type, each signal  $A \in \mathbb{S}$  represents statement that "A is active (is present, has been traversed, is scheduled) in all executions of the schedule". The constant true is validated by all schedules and false only by the empty schedule or the schedule which contains only the empty execution. The type operators  $\neg$ ,  $\supset$  are (intuitionistic) negation and implication. The two operators  $\lor$  and  $\oplus$  are two forms of logical disjunction to encode internal and external non-determinism and  $\land$ ,  $\parallel$  are two forms of logical conjunction related to true concurrency (multi-processing) and interleaving concurrency (multi-threading), respectively. Finally,  $\circ$  is the operator to express execution delays.

We will keep matters brief and present only some essential constructions in this theory. In fact, a fragment of the language will suffice to define interface types for KEP programs as far as they are treated in this paper. To begin with, define a

- *basic control type* to be an expression  $\zeta$  built from literals A,  $\neg A$  ( $A \in \mathbb{S}$ ) and constants *true*, *false* using conjunction  $\land$  and disjunction  $\oplus$ .

Basic control types satisfy  $S \models \zeta$  iff  $\sigma \models \zeta$  for all  $\sigma \in S$ , i.e., they express properties of individual executions. On executions,  $\zeta$  behaves like a standard Boolean combination of the atomic statements A (A present throughout  $\sigma$ ) and  $\neg A$  (A absent throughout  $\sigma$ ). For instance,  $\sigma \models A \oplus \neg A$  says that signal A is constant in  $\sigma$ , i.e., it is either present from the start,  $A \in \sigma(0)$ or never becomes active,  $A \notin \sigma(|\sigma| - 1)$ . Since signals which are not active initially may occur in the course of an execution the type  $A \oplus \neg A$  is not a tautology, i.e.,  $A \oplus \neg A \ncong$  true. This reveals the intuitionistic nature of negation which is crucial to handle the semantics of synchronous languages in a compositional and fully abstract way [29, 30]. For special signals like activation of nodes active(v) it is safe to assume  $active(v) \oplus \neg active(v) \cong true$  since these are state signals and decided at the start of every instant. Every basic control has an equivalent disjunctive normal form  $\zeta = \bigoplus_i \bigwedge_i l_{ij}$  over literals  $l_{ij}$ .

Basic controls  $\zeta$  are used to specify scheduling interaction at the input and output side of a program block. When used as an output we need to express that  $\zeta$  occurs delayed after some maximal number of ics, d say. We write  $\sigma, d \models \zeta$  or  $\sigma \models d : \zeta$  for this as an abbreviation of  $\sigma' \models \zeta$  where  $\sigma' = \sigma(d)\sigma(d+1)\cdots\sigma(|\sigma|-1)$  is the suffix of  $\sigma$  starting after d ics. Note that if the delay is larger than the length of the execution,  $d > |\sigma| - 1$  then this suffix is empty  $\sigma' = \emptyset$  and thus  $\sigma \models d : \zeta$  for all  $\zeta$ , even  $\zeta = false$  is validated. This is natural since by stepping beyond the final event within a thread's instant an inconsistent state is reached. We will see that this may be exploited for optimizations in WCRT analysis. The limit cases are  $+\infty$ : false  $\cong$  true and  $-\infty$ : false  $\cong$  false. The specification wait  $=_{df} 1 : false$  is of particular interest. It says that an execution has at most one event, i.e.,  $\sigma \models wait$  iff  $|\sigma| \leq 1$ . If non-empty such an execution has reached the end of the scheduling instant and is pausing in a final event  $\sigma(0) \subseteq S$ . We permit wait to be used as a third constant besides true and false inside basic controls. The reaction time of an execution  $\sigma$  may then either be specified as  $\sigma \models d : wait$  or  $\sigma \models d + 1 : false$  depending on whether we are interested in the number of steps or the number of events in  $\sigma$ .

- An output control is an expression  $\psi = \circ \zeta_1 \oplus \circ \zeta_2 \oplus \cdots \oplus \circ \zeta_n$  with basic controls  $\zeta_i$ .  $S \models \psi$ specifies that schedule S reaches at least one of the controls  $\zeta_j$  after a bounded number of ics. The selection of which  $\zeta_j$  is activated is expressed by  $\oplus$  since it is an internal choice which is dynamically resolved during each execution. Each operator  $\circ$  stands for a possibly different delay depending on which output  $\zeta_j$  is taken. In contrast to this, an output control such as  $\psi = \circ(\zeta_1 \oplus \zeta_2 \oplus \cdots \oplus \zeta_n)$  only specifies one bound for all exits  $\zeta_j$ .

- An *input control* is an expressions  $\phi = \zeta_1 \vee \zeta_2 \vee \cdots \vee \zeta_m$  where the disjunction  $\vee$  refers to the external non-determinism resolved by the environment which determines how a program block is started. There is also no delay involved which is why we do not need operator  $\circ$ . Formally,  $S \models \phi$  if there is at least one  $\zeta_i$  such that  $S \models \zeta_i$ .

Notice the change of quantifiers between input and output regarding executions:  $S \models \zeta_1 \lor \zeta_2$ requires  $\exists i \in \{1, 2\}$ .  $\forall \sigma \in S$ .  $\sigma \models \zeta_i$  and is an external choice whereas  $S \models \zeta_1 \oplus \zeta_2$  is  $\forall \sigma \in S$ .  $\exists i \in \{1, 2\}$ .  $\sigma \models \zeta_i$  which expresses an internal choice.

Finally, we build (input-output) interface types for KEP program fragments as implications  $\phi \supset \psi$  between input controls  $\phi = \bigvee_{i=1}^{m} \zeta_i$  and output controls  $\psi = \bigoplus_{j=1}^{n} \circ \xi_j$ . The input controls  $\phi$  capture all the possible ways in which the program fragment can be started within an instant and the output controls sum up the ways in which it can be exited during the instant. In other words, the  $\zeta_i$  and  $\xi_j$  represent logical input and output lines of the program. Intuitively,  $S \models \phi \supset \psi$  says that whenever any set of executions from schedule S enters the program through one of the input controls  $\zeta_i$  then within some bounded number  $d_{ij}$  of ics all these executions are guaranteed to exit through one of the output controls  $\xi_j$ . The bounds  $d_{ij}$  may depend on the choice of input and output control, in general. To capture the bounds we associate with each interface type a delay matrix of shape  $n \times m$ . Our type specifications then become logical expressions of the form  $D : \phi \supset \psi$  consisting of an interface type  $\phi$  together with a timing matrix D. The former describes the qualitative aspect of scheduling, the latter captures the quantitative part of the interface. Formally,  $\phi \supset \psi$  is a type specification for schedules S and the instrumented  $D : \phi \supset \psi$  specifies a set of executions.

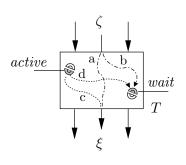

Let us look at how interface types are used. Figure 2 depicts a program fragment T abstracted into a reactive box with input and output controls. The paths inside T seen in Figure 2 illustrate the four ways in which a reactive block Tmay participate in the execution of a logical tick: Threads may (a) pass straight through the block entering at some input control  $\zeta$  and exiting at output control  $\xi$ ; (b) enter through  $\zeta$  but pausing inside, waiting there for the next instant; (c) start the tick inside the block and eventually (instantaneously) leave through some exit control  $\xi$ , or (d) start inside the block and never leave it during the current instant. These paths or rather sections of a path are called *through paths*, *sink paths*, *source paths* and *internal paths*, respectively.

The canonical interface type for such a block T (considering only one input control  $\zeta$  and one output control  $\xi$ ) separates these different paths and associated WCRT values:

$$T = \begin{pmatrix} d_{thr} \ d_{src} \\ d_{snk} \ d_{int} \end{pmatrix} : (\zeta \lor active) \supset (\circ \xi \oplus \circ wait)$$

If one of the paths does not exist its associated delay is set to  $-\infty$ . A block T can be classified according to the paths that are executable in it, i.e., that have  $d_{type} \ge 0$  (rather than  $d_{type} = -\infty$ ) for  $type \in \{thr, src, snk, int\}$ . Specifically, we call T a

- through node, if  $d_{thr} \ge 0$ , and  $N_{thr}$  the set of all through nodes

- source node, if  $d_{src} \ge 0$ , and  $N_{src}$  the set of all source nodes

- sink node, if  $d_{snk} \ge 0$ , and  $N_{snk}$  the set of all sink nodes

- *internal* node, if  $d_{int} \ge 0$ , and  $N_{int}$  the set of all internal nodes.

A delay node is a node with at least one non-instantaneous path, *i. e.*,  $N_{del} = N_{src} \cup N_{snk} \cup N_{int}$ . A strong delay node is a delay node without any through path, hence  $N_{sdel} = N_{del} \setminus N_{thr}$ . A transient node is a through node that contains only through paths, i.e.,  $d_{src} = d_{snk} = d_{int} = -\infty$ . Thus  $N_{trans} = N_{thr} \setminus N_{del}$ . We assume that each cyclic dependency loop in the program is broken by at least one strong delay node.

It is useful to classify the exits of a node T according to the type of path on which they can appear. We call an exit *instantaneous* if it can *only* be activated on through paths (type a) and *non-instantaneous* if it can be reached *only* by source paths (type c). The successor nodes reached by them are referred to accordingly as *instantaneous successors* and *non-instantaneous successors* of T. In the KEP assembler graphs of [13] two other types of successor nodes are

nal path (d).

Fig. 2: The four types of thread

paths: through path (a), sink

path (b), source path (c), inter-

#### 5. WCRT INTERFACES AT WORK

distinguished, the *control successors* and *exit successors*. Since control successors are activated either by through paths (type a) or source paths (type c) they constitute the general case from the WCRT scheduling point of view. The exit successors, which are introduced by exit-trap blocks, are activated exclusively as part of through paths. Thus, they are instantaneous successors in our terminology.

Often we split the interface T into its two parts  $T = [T_{srf}, T_{dpt}]$ , the surface interface and the depth interface

$$T_{srf} = \begin{pmatrix} d_{thr} \\ d_{snk} \end{pmatrix} : \zeta \supset (\circ \xi \oplus \circ wait) \qquad T_{dpt} = \begin{pmatrix} d_{src} \\ d_{int} \end{pmatrix} : active \supset (\circ \xi \oplus \circ wait).$$

By logical transformations of interfaces various optimizations can be achieved. For instance, for transient nodes we reduce  $T_{srf}$  as follows:

$$T_{srf} \cong (d_{thr}, -\infty)^T : \zeta \supset (\circ \xi \oplus \circ wait) \cong \zeta \supset ((d_{thr} : \xi) \oplus (-\infty : wait))$$

$$\cong \zeta \supset (d_{thr} : \xi \oplus ((-\infty + 1) : false)) \cong \zeta \supset (d_{thr} : \xi \oplus (-\infty : false))$$

$$\cong \zeta \supset (d_{thr} : \xi \oplus false) \cong \zeta \supset (d_{thr} : \xi)$$

$$\cong (d_{thr}) : \zeta \supset \circ \xi,$$

while  $T_{dpt} = (-\infty, -\infty)^T$ : active  $\supset (\circ \xi \oplus \circ wait) \cong true$  is simply dropped. Moreover, without loss of generality we may suppose that  $T_{srf}$  is normalized so it satisfies  $d_{thr} \leq d_{snk}$  for all sink nodes T. Otherwise, if  $d_{snk} < d_{thr}$  we would have

$$(d_{thr}:\xi) \oplus (d_{snk}:wait) \cong (d_{thr}:\xi) \oplus (d_{snk}+1:false)$$

$$\preceq (d_{thr}:\xi) \oplus (d_{snk}+1:\xi)$$

$$\cong max(d_{thr},d_{snk}+1):\xi$$

$$\cong d_{thr}:\xi,$$

where  $\phi \leq \psi$  means that all executions satisfying  $\phi$  also satisfy  $\psi$ . In the other direction, it trivially holds that  $d_{thr}: \xi \leq (d_{thr}: \xi) \oplus (d_{snk}: wait)$ . Hence, whenever  $d_{snk} < d_{thr}$  the two types  $(d_{thr}: \xi) \oplus (d_{snk}: wait)$  and  $(d_{thr}: \xi)$  are equivalent which means essentially that the sink paths are redundant and thus could be pruned. Operationally, if  $d_{snk} < d_{thr}$  then the through path  $(d_{thr}): \zeta \supset \circ \xi$  of T dominates the WCRT while the sink path  $(d_{snk}): \zeta \supset \circ wait$  in T cannot contribute to the longest execution. In this case we might as well assume  $d_{snk} = -\infty$ , i.e., that T is not a sink node at all. The same arguments apply to the depth interfaces  $T_{dpt}$ , for which we may thus assume  $d_{src} \leq d_{int}$  or otherwise  $d_{int} = -\infty$ .

In general, the interface type of a program T will mention a number of controls  $\zeta_1, \zeta_2, \ldots, \zeta_m$ and  $\xi_1, \xi_2, \ldots, \xi_n$  on the input and output side for which the type would be

$$T = D : (\zeta_1 \lor \zeta_2 \cdots \lor \zeta_m) \supset (\circ\xi_1 \oplus \circ\xi_2 \oplus \cdots \oplus \circ\xi_n)$$

(1)

with a WCRT matrix D of shape  $n \times m$ . The terminology above can be applied, mutatis mutandis, to such general controls. A composite program will be made up of a number of program fragments  $T_i$  each with its interface  $D_i : \phi_i \supset \psi_i$ . The total specification is the logical conjunction  $\bigwedge_i D_i : \phi_i \supset \psi_i$  in WCRT type theory. The basic controls appearing in  $\phi_i, \psi_i$  describe the causal dependencies between the blocks  $T_i$ . In its general form, WCRT analysis amounts to a transformation

$$\bigwedge_{i} D_{i} : \phi_{i} \supset \psi_{i} \quad \preceq \quad D : \phi \supset \psi \tag{2}$$

in which the individual timing interfaces are combined into a total delay matrix D for an external interface  $\phi \supset \psi$  such that D is the smallest (component-wise) matrix of values such that (2) holds. The external interface  $\phi \supset \psi$  determines the functional precision with which we are computing the WCRT of the composite system. For instance, instead of an interface like (1) which distinguishes m input and n output controls a less discriminative type  $\zeta \supset \circ \xi$  with  $\zeta =_{df} \bigoplus_{i \in I} \zeta_i$

and  $\xi =_{df} \circ \bigoplus_{j \in J} \xi_j$  might consider merely subsets  $I \subseteq \{1, \ldots, m\}$  and  $J \subseteq \{1, \ldots, n\}$  of inputs and outputs bundled into a single control. Such an interface  $\zeta \supset \circ \xi$  which specifies only one delay value is more abstract than (1). We can trade off precision and efficiency of the WCRT analysis within wide margins by choosing different types  $\phi_i \supset \psi_i$  for the components and  $\phi \supset \psi$  for the composite program in (2).

Of course, we do not expect to get an equivalence  $\cong$  but only an inclusion  $\preceq$  in (2) if the calculation of D involves timing abstractions. In general, the right-hand side of (2) will include more executions than the left-hand side. E.g., this occurs naturally whenever the composite type  $\phi \supset \psi$  does not include all internal signals mentioned in the types  $\phi_i \supset \psi_i$ . Then the right-hand side of (2) does not constrain the executions on those internal signals while the left-hand side still restricts them. Many other types of abstractions are possible as we shall see.

How is the composition (2) performed? In general, we can use any sound and complete logical calculus for WCRT type theory as described, e.g., in [28]. For our special interface types this calculus reduces to matrix multiplication in maxplus algebra  $(\mathbb{N}, +, max, 0, -\infty)$  [15] combined with logical reasoning on basic controls  $\zeta$ , which is a slight generalization of Boolean algebra. We will explain this in the following sections by way of our running example from Fig. 1. More details on the semantic theory of WCRT algebra can be found in the appendix, Sec. A.

#### 5.2 Instantaneous Behavior: Transient Nodes

Let us begin by illustrating the role of type specifications for WCRT in the single-threaded execution of transient nodes. Although in this case WCRT analysis is equivalent to computing longest paths and straight-forward even without timing interfaces, it will give a first idea of the power of types for modularization and abstraction. This will lay out the playground in which we can later deal with Esterel-style pausing, preemption, multithreading, etc. General synchronous flow

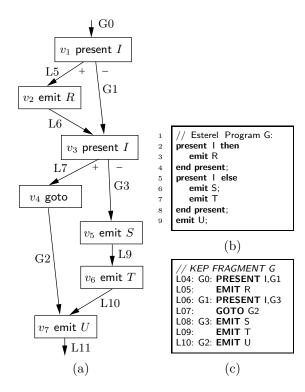

Fig. 3: Control Flow G (a), Esterel (b), KEP Assembler (c).

graphs live at a higher level of abstraction in which control dependencies are more implicit and thus WCRT analysis no longer identical to the longest path problem.

Our example is the sequential program G of Fig. 3 which is the fragment of Fig. 1c consisting of nodes  $v_1-v_7$ . Each of them is a KEP assembler instruction which is entered either sequentially through its instruction number L4–L10 or through an explicit jump to a control flow label such as G0–G3. For instance, node  $v_3$  is accessed both through its linear instruction number L6 as well as by jump to its label G1. In contrast, node  $v_4$  is only accessed through its line number L7 while node  $v_5$  only by jumping to its label G3. The present nodes  $v_1$  and  $v_3$  are tests which branch to their two successor instructions depending on the status of signal I. If I is present then  $v_1$  moves to instruction  $v_2$  which immediately follows it and if I is absent then  $v_1$  passes control to instruction  $v_3$  by jumping to label G1. Let us assume that each of the basic instructions present, emit, goto take 1 processor cycle regardless how it is entered or exited. Their timing interfaces are then specified as follows:

$$v_1 = \begin{pmatrix} 1 \\ 1 \end{pmatrix} : G0 \supset \circ L5 \oplus \circ G1 \qquad v_2 = (1) : L5 \supset \circ L6 \qquad v_3 = \begin{pmatrix} 1 & 1 \\ 1 & 1 \end{pmatrix} : (L6 \lor G1) \supset \circ L7 \oplus \circ G3$$

$$v_4 = (1) : L7 \supset \circ G2 \qquad v_5 = (1) : G3 \supset \circ L9 \qquad v_6 = (1) : L9 \supset \circ L10$$

$$v_7 = (1 \ 1) : (G2 \lor L10) \supset \circ L11.$$

Logically speaking, the problem of WCRT for G amounts to obtaining the tightest bound d such that  $d: G0 \supset \circ L11$  is semantically entailed by this theory, i.e., by  $\bigwedge_{i=1}^7 v_i$ .

Weaving Paths The naive strategy would be to enumerate all paths from G0 to L11, sum up the delays on each path and then take the maximum. There are four paths  $p_1 = G0 L5 L6 L7 G2 L11$ ,  $p_2 = G0 G1 L7 G2 L11$ ,  $p_3 = G0 L5 L6 G3 L9 L10 L11$  and  $p_4 = G0 G1 G3 L9 L10 L11$ . Each of these paths defines a sub-graph of G with specific sideinputs and side-outputs. For instance,  $p_1$  as indicated in Fig. 4 has the side-outputs G1, G3 and side-inputs G1, L10 so that its full scheduling type is  $G0 \vee L10 \vee G1 \supset \circ G1 \oplus \circ G3 \oplus \circ L11$ . This type says that if  $p_1$  gets activated through control edges G0, L10 or G1 then it must be terminated through one of the exits G1, G3 or L11. The timing matrix associated with this type is

$$D_1: G0 \lor L10 \lor G1 \supset \circ G1 \oplus \circ G3 \oplus \circ L11$$

where

$$D_1 = \begin{pmatrix} 1 - \infty - \infty \\ 3 - \infty & 1 \\ 5 & 1 & 3 \end{pmatrix}.$$

The entries  $-\infty$  in  $D_1$  mean that there is no causal control flow from the corresponding input to the corresponding output line.  $D_1$  can be obtained by successively multiplying (in max-plus algebra) the timing matrices of the individual nodes traversed by  $p_1$ . We explain below in Sec. 5.2 how this is done. At this point note that for WCRT of G we are not actually interested in the exact timing of the side-inputs, i.e., the fact

Fig. 4: The path  $p_1$  in G.

that  $p_1$  can also be executed from L10 and G1. One way to suppress this information is by pre-composing  $D_1$  with the timing map  $(0, -\infty, -\infty)^T : G0 \supset \circ G0 \oplus \circ L10 \oplus \circ G1$  giving

$$p_1' = D_1' : G0 \supset \circ G1 \oplus \circ G3 \oplus \circ L11 \tag{3}$$

where

$$D_1' = D_1 \cdot \begin{pmatrix} 0 \\ -\infty \\ -\infty \end{pmatrix} = \begin{pmatrix} 1 - \infty - \infty \\ 3 - \infty & 1 \\ 5 & 1 & 3 \end{pmatrix} \cdot \begin{pmatrix} 0 \\ -\infty \\ -\infty \end{pmatrix} = \begin{pmatrix} 1 \\ 3 \\ 5 \end{pmatrix}.$$

The type (3) stipulates that every execution which enters path  $p'_1$  through input G0 either leaves  $p_1$  through exit G1 in at most 1 ic, through exit G3 in at most 3 ic or through L11 within no more than 5 ics.  $D'_1$  in contrast to  $D_1$  no longer records the exact delay between particular combinations of inputs and outputs of  $p_1$ . For instance, the fact that L11 is reached in  $p_1$  from L10 in only 1 ic of time and from G1 in at most 3 ics instead of 5, is lost. Similarly, the information that from input L10 we cannot reach output G3 at all, indicated by the entry  $-\infty$  in  $D_1$  is not present in  $D'_1$  any more.

In talking about executions along  $p_1$  we also assume that the path is not exited through G1 or G3. Can we suppress the references to side-outputs G1 and G3 on the right of  $\supset$  of the

scheduling type (3)? Well, not directly, because if we simply drop them the resulting scheduling type  $G0 \supset \circ L11$  would guarantee that *all* executions entering  $p_1$  through G0 eventually come out at L11. This is obviously false. However, we can fix this using negations and conjunctions. The right type is  $(G0 \land \neg G1 \land \neg G3) \supset \circ L11$  which strengthens the assumption G0 by  $\neg G1 \land \neg G3$  to the effect that only executions starting in G0 not involving G1 or G3 are considered. Indeed we can construct a timing for this type and justify its semantic correctness as follows: First, by purely logical reasoning on types (not involving any matrix calculations) we argue that  $D'_1$  which has type  $G0 \supset \circ G1 \oplus \circ G3 \oplus \circ L11$  also must have type  $(G0 \land \neg G1 \land \neg G3) \supset \circ false \oplus \circ false \oplus \circ L11$  and then compose with the sound schedule  $(-\infty, -\infty, 0) : (false \lor false \lor L11) \supset \circ L11$  to obtain

$$p_1 = D_1'' : (G0 \land \neg G1 \land \neg G3) \supset \circ L11 \quad \text{where} \quad D_1'' = (-\infty - \infty \ 0) \cdot \begin{pmatrix} 1\\3\\5 \end{pmatrix} = (5). \tag{4}$$

which is the proper type specification of path  $p_1$  without side-inputs and side-outputs. For the other paths we get in a similar fashion

$$p_2 = D_2'' : (G0 \land \neg L5 \land \neg G3) \supset \circ L11 \qquad \qquad D_2'' = (4) \tag{5}$$

$$p_3 = D_3'' : (G0 \land \neg G1 \land \neg L7) \supset \circ L11 \qquad \qquad D_3'' = (6) \tag{6}$$

$$p_4 = D_4'' : (G0 \land \neg L5 \land \neg L7) \supset \circ L11 \qquad \qquad D_4'' = (5). \tag{7}$$

The path schedules (4)–(7) can now be woven together to obtain the final result G = (6):  $G0 \supset \circ L11$ . First, recall that  $[D_1, D_2] : (\phi_1 \lor \phi_2) \supset \circ L11$  is the sum of  $D_1 : \phi_1 \supset \circ L11$  and  $D_2 : \phi_2 \supset \circ L11$ . So we can combine (3)–(7) as  $D'' =_{df} [(5), (4), (6), (5)] = (5, 4, 6, 5)$  with the type

$$D'': ((G0 \land \phi_1) \lor (G0 \land \phi_2) \lor (G0 \land \phi_3) \lor (G0 \land \phi_4)) \supset \circ L11$$

(8)

in which  $\phi_1 =_{df} \neg G1 \land \neg G3$ ,  $\phi_2 =_{df} \neg L5 \land \neg G3$ ,  $\phi_3 =_{df} \neg G1 \land \neg L7$  and  $\phi_4 =_{df} \neg L5 \land \neg L7$ . We pre-compose (8) with the timing  $(0,0,0,0)^T : \bigoplus_{i=1}^4 (G0 \land \phi_i) \supset \bigoplus_{i=1}^4 \circ (G0 \land \phi_i)$ :

$$(5,4,6,5) \cdot (0,0,0,0)^T = (6) : ((G0 \land \phi_1) \oplus (G0 \land \phi_2) \oplus (G0 \land \phi_3) \oplus (G0 \land \phi_4)) \supset \circ L11.$$

(9)

Then consider that by distributivity  $\bigoplus_{i=1}^{4} (G0 \land \phi_i)$  is logically equivalent to  $G0 \land \bigoplus_{i=1}^{4} \phi_i$ . Moreover, under single-threaded execution (and only then<sup>2</sup>) the type equivalence

$$\oplus_{i=1}^{4}\phi_{i} = (\neg G1 \land \neg G3) \oplus (\neg L5 \land \neg G3) \oplus (\neg G1 \land \neg L7) \oplus (\neg L5 \land \neg L7) \equiv true$$

holds in G since every execution thread must make a split decision for either exit L5 or G1 at node  $v_1$  and for either L7 or G3 at node  $v_3$ . Hence, every thread satisfies one of the summands  $\neg G1 \land \neg G3, \neg L5 \land \neg G3, \neg G1 \land \neg L7$  or  $\neg L5 \land \neg L7$ . Taking all together gives  $\bigoplus_{i=1}^{4} (G0 \land \phi_i) \equiv$  $G0 \land \bigoplus_{i=1}^{4} \phi_i \equiv G0 \land true \equiv G0$  and thus (9) turns into (6) :  $G0 \supset \circ L11$  which finally is the WCRT of graph G.

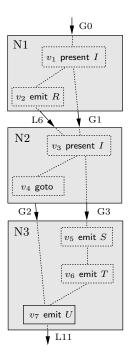

Weaving Nets WCRT analysis by enumeration of paths, though sound, is of worst-case exponential complexity. A more efficient way of going about is to exploit dynamic programming techniques. In the following we illustrate this process in terms of the decomposition of G seen in Fig. 5. The strategy is to propagate WCRT information forward through G describing and composing (in this case) sub-nets N1, N2, N3 rather than paths. In doing so we extend the scheduling interfaces appropriately in order to make the matrices match up:

<sup>&</sup>lt;sup>2</sup> For multi-threaded execution several exits may be taken in one and the same run by different threads. Also observe that, in contrast to  $\oplus$ , the disjunction  $\phi_1 \lor \phi_2 \lor \phi_3 \lor \phi_4$  is not equivalent to *true*! This would hold under *static* and *deterministic* scheduling in which *all* executions are in one of the schedules  $\phi_i$ . Since the exits from statements  $v_1$  and  $v_3$  are data-dependent, different executions may choose different paths.

1. We obtain the scheduling type of N1 by combining  $v_1$  of type  $G0 \supset \circ L5 \oplus \circ G1$  with  $v_2$  of type  $L5 \supset \circ L6$ . To compose them we first lift  $v_2$  to type  $L5 \lor G1 \supset \circ L6 \oplus \circ G1$  by pre-multiplying it with the embedding  $(0, -\infty)^T : L6 \supset \circ L6 \oplus \circ G1$  giving

$$v_2' = \begin{pmatrix} 0 \\ -\infty \end{pmatrix} \cdot v_2 = \begin{pmatrix} 0 \\ -\infty \end{pmatrix} \cdot (1) = \begin{pmatrix} 1 \\ -\infty \end{pmatrix} : L5 \supset \circ L6 \oplus \circ G1.$$

Next we combine  $v'_2$  with  $(-\infty, 0)^T : G1 \supset \circ L6 \oplus \circ G1$  to give

$$v_2'' = \left[ \begin{pmatrix} 1 \\ -\infty \end{pmatrix}, \begin{pmatrix} -\infty \\ 0 \end{pmatrix} \right] = \begin{pmatrix} 1 & -\infty \\ -\infty & 0 \end{pmatrix} : L5 \lor G1 \supset \circ L6 \oplus \circ G1,$$

where as before  $[D_1, D_2] : (\phi_1 \lor \phi_2) \supset \psi$  is the sum of  $D_1 : \phi_1 \supset \psi$ and  $D_2 : \phi_2 \supset \psi$ . The shapes of matrices  $v_1$  and  $v''_2$  now connect up and we get  $N1 = v''_2 \cdot v_1$ :

$$N1 = \begin{pmatrix} 1 & -\infty \\ -\infty & 0 \end{pmatrix} \cdot \begin{pmatrix} 1 \\ 1 \end{pmatrix} = \begin{pmatrix} 2 \\ 1 \end{pmatrix} : G0 \supset \circ L6 \oplus \circ G1.$$

2. Next we construct the WCRT of block  $N2 : (L6 \lor G1) \supset \circ G2 \oplus \circ G3$  by composing  $v_3 : (L6 \lor G1) \supset \circ L7 \oplus \circ G3$  with  $v4 : L7 \supset \circ G2$ . With the help of  $(0, -\infty)^T : G2 \supset \circ G2 \oplus \circ G3$  and  $(-\infty, 0)^T : G3 \supset \circ G2 \oplus \circ G3$  we extend the schedule of  $v_4$  to become of type  $(L7 \lor G3) \supset \circ G2 \oplus \circ G3$  which can then be composed with  $v_3$  as follows:

Fig. 5: Decomposition of G.

$$N2 = \begin{bmatrix} \begin{pmatrix} 0 \\ -\infty \end{pmatrix} \cdot v_4, \begin{pmatrix} -\infty \\ 0 \end{bmatrix} \end{bmatrix} \cdot v_3 = \begin{bmatrix} \begin{pmatrix} 0 \\ -\infty \end{pmatrix} \cdot (1), \begin{pmatrix} -\infty \\ 0 \end{bmatrix} \end{bmatrix} \cdot \begin{pmatrix} 1 & 1 \\ 1 & 1 \end{pmatrix}$$

$$= \begin{pmatrix} 1 & -\infty \\ -\infty & 0 \end{pmatrix} \cdot \begin{pmatrix} 1 & 1 \\ 1 & 1 \end{pmatrix} = \begin{pmatrix} 2 & 2 \\ 1 & 1 \end{pmatrix} : (L6 \lor G1) \supset \circ G2 \oplus \circ G3.$$

3. The third step is to build  $N3: (G2 \vee G3) \supset \circ L11$  from  $v_5: G3 \supset \circ L9$ ,  $v_6: L9 \supset \circ L10$  and  $v_7: (G2 \vee L10) \supset \circ L11$ .  $v_5$  and  $v_6$  can be directly multiplied:  $v_6 \cdot v_5 = (1) \cdot (1) = (2): G3 \supset \circ L10$ . Then we lift  $v_6 \cdot v_5$  to type  $(G2 \vee G3) \supset \circ G2 \oplus \circ L10$  and pre-multiply with  $v_7$ :

$$N3 = v_7 \cdot \left[ \begin{pmatrix} 0 \\ -\infty \end{pmatrix}, \begin{pmatrix} -\infty \\ 0 \end{pmatrix} \cdot v_6 \cdot v_5 \right] = v_7 \cdot \begin{pmatrix} 0 & -\infty \\ -\infty & 2 \end{pmatrix}$$

$$= (1 \ 1) \cdot \begin{pmatrix} 0 & -\infty \\ -\infty & 2 \end{pmatrix} = (1 \ 3) : (G2 \lor G3) \supset \circ L11.$$

4. If we compose the three sub-nets N1, N2, N3 in sequence, our schedule of G all the way from entry point G0 to exit L11 is complete:

$$G = N3 \cdot N2 \cdot N1 = (1\ 3) \cdot \binom{2\ 2}{1\ 1} \cdot \binom{2}{1} = (1\ 3) \cdot \binom{4}{3} = (6) : G0 \supset \circ L11.$$

This is indeed the weight of the longest path  $p_3$ .

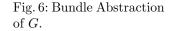

**Bundling Abstractions** There are of course other ways of arriving at (an approximation of) the WCRT, corresponding to different network decompositions of G. It is also possible to condense the timing information by *bundling* the inputs and outputs of N1, N2, N3 before they are composed. For instance, one might decide to compress the scheduling type of N1 into a single entry-exit delay  $N1' : G0 \supset \circ(L6 \oplus G1)$  which specifies the worst-case delay for an execution entering through G0 to come out at L6 or G1, without distinguishing between threads exiting on L6 and those exiting on G1. This is applied also to N2 and N3 as indicated in Fig.6.

This compression is done algebraically by pre-composing N1 with  $(0,0): (L7 \vee G1) \supset \circ (L7 \oplus G1)$  which yields  $N1' = (0,0) \cdot N1 = (0,0) \cdot (2,1)^T = (2): G0 \supset \circ (L6 \oplus G1)$ . In the same way, we could compress N2 and N3 to

$$N2' = \begin{pmatrix} 0 & 0 \end{pmatrix} \cdot \begin{pmatrix} 2 & 2 \\ 1 & 1 \end{pmatrix} \cdot \begin{pmatrix} 0 \\ 0 \end{pmatrix} = (2) : (L6 \oplus G1) \supset \circ(G2 \oplus G3)$$

$$N3' = \begin{pmatrix} 1 & 3 \end{pmatrix} \cdot \begin{pmatrix} 0 \\ 0 \end{pmatrix} = (3) : (G2 \oplus G3) \supset \circL11.$$

Each of the scheduling types  $N'_i$  is a max-abstraction of the original interface  $N_i$ . This is seen from the fact that semantically  $N_i \subseteq N'_i$ , i.e., each execution satisfying  $N_i$  is also an execution under schedule  $N'_i$ . Thus, the timing value associated with  $N'_i$  is an upper bound of all schedules in  $N_i$ . Yet, it is not exact because  $N'_i$  is properly larger than  $N_i$ . For instance,  $N'_1$  contains an execution of duration 2 which exits on G1 while  $N_1$  (exactly) states that all threads leaving through G1 consume no more than 1 ic. The same is true of the other sub-nets  $N'_2$  and  $N'_3$ . As a result of this imprecision the composition  $N3' \cdot N2' \cdot N1' = (2) \cdot (2) \cdot (3) = (7)$  yields an over-approximation of G's WCRT.

Why would we want to abstract the sub-nets in this way and lose exactness? The answer is that composing N1', N2', N3' is more efficient since it involves only scalars rather than matrices.

G0 N1'  $v_1$  present I  $v_2$  emit R  $L6 \oplus G1$ N2'  $v_3$  present I  $v_4$  goto  $G2 \oplus G3$ N3'  $v_5$  emit S  $v_6$  emit T  $v_7$  emit U L11

**Data Dependency and Degrees of Precision** A full and exact WCRT specification encapsulating program G as a component would require mention of program labels G1, G3, G2 which are accessible from outside for jump statements. Therefore, the interface type for single-threaded scheduling of G would be

$$G = (6, 4, 3, 1) : (G0 \lor G1 \lor G3 \lor G2) \supset \circ L11.$$

This is still not the exact description of G since it does not express the dependency of the WCRT on signal I. If I is present then all threads must take control edges L5 and L7 rather than G1 or G3 which are blocked. If I is absent then both G1 and G3 must be taken instead. As a result the longest path  $p_3 = G0L5L6G3L9L10L11$  with delay 6 is not executable. To capture this we consider signal I as just another control input and refine the WCRT scheduling type of G as follows:

$$G = (5, 5, 3, 4, 3, 1) : ((G0 \land I) \lor (G0 \land \neg I) \lor (G1 \land I) \lor (G1 \land \neg I) \lor G3 \lor G2) \supset \circ L11.$$

(10)

The inclusion of signal I in the interface has now resulted in the distinction of two different delay values 3 and 4 for  $G1 \supset \circ L11$  depending on whether I is present or absent during the reaction. On the other hand, G0 split into controls  $G0 \land I$  and  $G0 \land \neg I$  produces the same delay of 5 ics in both cases, which is a decrease of WCRT compared to  $6: G0 \supset \circ L11$  from above. Assuming that input signal I is causally stable, i.e.,  $I \oplus \neg I \cong true$  it is possible to optimize the interface without losing precision: since  $(G0 \land I) \oplus (G0 \land \neg I) \cong G0 \land (I \oplus \neg I) \cong G0 \land true \cong G0$  the map  $(0, 0)^T: G0 \supset \circ(G0 \land I) \oplus \circ(G0 \land \neg I)$  is sound and can be used to compress the two entries of value 5 in (10) into a single value 5 = max(5, 5) giving

$$G = (5, 3, 4, 3, 1) : (G0 \lor (G1 \land I) \lor (G1 \land \neg I) \lor G3 \lor G2) \supset \circ L11.$$

In the same vein, but this time without referring to stability, we could further bundle  $G1 \wedge I$ and G3 into a single control with the single delay  $(3) : ((G1 \wedge I) \oplus G3) \supset \circ L11$  at the same level precision. Still, if we only ever intend to use G as a composite transient node  $G0 \supset \circ L11$  the typing  $G = (5) : G0 \supset \circ L11$  might be sufficient. The different WCRT type specifications of G are summarized in Fig. 7. Considering that G is a transient block, i.e., it does not have any delay nodes, the depth interface of G is trivial  $G_{dpt} = (-\infty, -\infty)^T : active \supset \circ L11 \oplus \circ wait$ . Though trivial it will be useful when we integrate G in a fork-join block uniformly as described in the next section.

Fig. 7: Component G and some of its WCRT Types with varying precision and conciseness.

All the operations performed above are supported by semantically sound proof rules in WCRT type theory. The logical manipulation of types often can be also done implicitly and hard-coded into the graph-theoretic search strategies that make up the cleverness of a particular WCRT algorithm. Where interface types are not used directly in the calculations they provide for a highly compositional fine-analysis which allows us to validate our WCRT algorithms in terms of precise statements about correctness and exactness. Due to their logical-symbolic nature WCRT interfaces can be applied in rather general situations which involve data and higher control-flow constructs as used in synchronous programming. Some aspects of the latter will be expounded in the following sections.

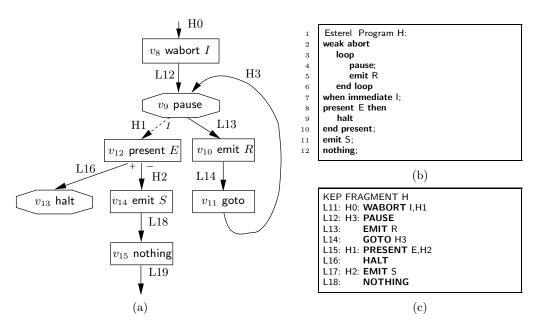

#### 5.3 Sequential Behavior: Delay Nodes

Now we take a look at sequential control flow which initiates and terminates in pause and halt nodes. We illustrate how these are related to the scheduling types *active* and *wait*. We use the example seen in Fig. 8 which is the fragment of nodes  $v_8-v_{15}$  from our running example in Fig. 1a. Nodes wabort, emit, goto, present, nothing are transient and specified as before in Sec. 5.2. But now the instantaneous paths are broken by the delay nodes  $v_9$  and  $v_{13}$ .

Consider the **pause** node  $v_9$ . It can be entered by two controls, the line number L12 and program label H3 and left via two kinds of exits, a non-instantaneous edge L13 and a instantaneous exit H1 (weak abortion). When a control thread enters  $v_9$  then either it terminates the current instant inside the node or leaves through the weak abort H1 (data-dependent, if signal *I* is present) continuing the current instant, instantaneously. A thread entering  $v_9$  never exits through L13 in the same instant. On the other hand, if a thread is started (resumed) from inside the **pause** node  $v_9$  then control can only exit through L13. This suggests to specify the **pause** node by the following pair of scheduling types:

$$\begin{pmatrix} 1 & 1 \\ 1 & 1 \end{pmatrix} : (H3 \lor L12) \supset \circ H1 \oplus \circ wait$$

(11)

$$(1): active(v_9) \supset \circ L13 \tag{12}$$

The specification (11) says that if pause is entered through H3 or L12 it can be left through H1 or terminate (*wait*) inside the pause. In both cases execution takes 1 instruction cycle, either

Fig. 8: Sequential Control Flow H (a), Esterel program (b) and KEP Assembler (c).

to move the program counter forward to H1 or to reach an internal wait state. Since there are no differences in the delays we could bundle the inputs H3, L12 and compress the matrix as  $(1,1)^T : (H3 \oplus L12) \supset \circ H1 \oplus \circ wait$  or even  $(1) : (H3 \oplus L12) \supset \circ (H1 \oplus wait)$  without losing information over (11). Still, we could do even better and record the dependency of control on signal I, with the more precise type

$$\begin{pmatrix} 1 & -\infty \\ -\infty & 1 \end{pmatrix} : ((H3 \oplus L12) \land I) \lor ((H3 \oplus L12) \land \neg I) \supset \circ H1 \oplus \circ wait.$$

This separates the threads which must stop inside the pause from those which must leave via H1 due to a weak immediate abort on signal I.

The specification (12) accounts for threads starting in the **pause** which must necessarily pass control to L13 within one instruction cycle. This is why (12) does not include a source path of type  $active(v_9) \supset \circ H1$ . In a similar way we can model strong or non-immediate aborts. For delayed (non-immediate) weak abort, there is no path from L12 to H1. For strong abort, the abortion can not be taken in the instant when  $v_9$  is entered, thus there is no path from H3 or L12 to H1.

The halt node  $v_{13}$  in Fig. 8 (equivalent to an infinitely pausing loop pause, but faster) is not only a sink for control threads entering through L16 but it also has an internal path of length 1 (which is repeated at every instant). It is a strong delay node and specified by

$$(1,1): (active(v_{13}) \lor L16) \supset \circ wait.$$

$$(13)$$

Now let us determine the WCRT of G, essentially refining the strategy informally described in [13]. First, generalizing the notion of surface interfaces we define the *surface reaction time* of a control edge A of graph H as the (component-wise) smallest vector A.srf such that A.srf:  $A \supset \circ L19 \oplus \circ wait$  is derivable from the H's WCRT theory.<sup>3</sup> Obviously, the value H0.srf is the surface interface  $H_{srf}$  of program H in Fig. 8 seen as a reactive box with (sole) input H0. Following the strategy of the WCRT algorithm of [13] the computation of H0.srf proceeds by depth-first search forward from H0: We compose node  $v_8$  of type (1) :  $H0 \supset \circ L12$  with the

<sup>&</sup>lt;sup>3</sup> In [13] this number is denoted *A.inst* and computed for *complete* programs in which all paths are terminated by **pause** or **halt** nodes. Dangling exits like L19 of Fig. 8 are not considered. Also, the WCRT is defined for nodes rather than edges as we do here. These are minor differences, however.

through part  $(1,1)^T : L12 \supset \circ H1 \oplus \circ wait$  of  $v_9$ 's interface given in (11) to get  $(1,1)^T \cdot (1) = (2,2)^T : H0 \supset \circ H1 \oplus \circ wait$ . This reduces the computation of H0.srf to that of computing  $H1.srf : H1 \supset \circ L19 \oplus \circ wait$  via  $H0.srf = [H1.srf, (-\infty, 0)^T] \cdot (2, 2)^T$ , where  $[H1.srf, (-\infty, 0)^T]$  is the lifting of  $H1.srf : H1 \supset \circ L19 \oplus \circ wait$  to type  $(H1 \lor wait) \supset \circ L19 \oplus \circ wait$  so it can be composed with  $(2,2)^T$ . As shown below we eventually get  $H1.srf = (3,2)^T$  and thus

$$H_{srf} = H0.srf = [H1.srf, (-\infty, 0)^T] \cdot (3, 2)^T$$

$$= \begin{pmatrix} 2 & -\infty \\ 2 & 0 \end{pmatrix} \cdot \begin{pmatrix} 2 \\ 2 \end{pmatrix} = \begin{pmatrix} 5 \\ 4 \end{pmatrix} : H0 \supset \circ L19 \oplus \circ wait$$

(14)

which tells us that the longest through path (H0 L12 H1 H2 L18 L19) has 5 ics and the longest sink path (H0 L12 H1 L16) consumes 4 ics.

Like the surface interfaces, the depth interfaces, too, may be generalized: Each node v has a depth reaction time<sup>4</sup> in H, v.dpt, which is the smallest vector m derivable such that m:  $active(v) \supset \circ L19 \oplus \circ wait$ . It characterizes the maximal duration of an instant which starts inside v either leaving at exit L19 or terminating in the pause or halt nodes of H. It only needs to be computed for source nodes and internal nodes. For all others we have  $v.d_{src} = v.d_{int} = -\infty$ which implies  $v.dpt = -\infty$ , too. In graph H of Fig. 8 only the pause node  $v_9$  and the halt node  $v_{13}$  have a source or internal WCRT.

For instance, the depth interface of (13) gives delay 1 :  $active(v_{13}) \supset \circ wait$  for the halt. Since this internal path is the only way to start in  $v_{13}$  and eventually terminate or exit H, the depth reaction time of  $v_{13}$  is

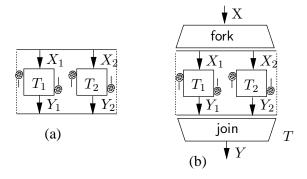

$$v_{13}.dpt = (-\infty, 1): active(v_{13}) \supset \circ L19 \oplus \circ wait.$$