(will be inserted by the editor)

## **Denotational Fixed-Point Semantics for Constructive Scheduling of Synchronous Concurrency**

Joaquín Aguado Michael Mendler Reinhard von Hanxleden Insa Fuhrmann

Received: date / Accepted: date

**Abstract** The synchronous model of concurrent computation (SMoCC) is well established for programming languages in the domain of safety-critical reactive and embedded systems. Translated into mainstream C/Java programming, the SMoCC corresponds to a cyclic execution model in which concurrent threads are synchronised on a *logical clock* that cuts system computation into a sequence of *macro-steps*. A *causality analysis* verifies the existence of a schedule on memory accesses to ensure each macro-step is deadlock-free and determinate.

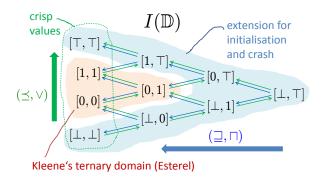

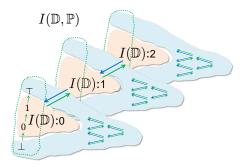

We introduce an abstract semantic domain  $I(\mathbb{D},\mathbb{P})$  and an associated denotational fixed point semantics for reasoning about concurrent and sequential variable accesses within a synchronous cycle-based model of computation. We use this domain for a new and extended behavioural definition of Berry's causality analysis in terms of approximation intervals. The domain  $I(\mathbb{D},\mathbb{P})$  extends the domain  $I(\mathbb{D})$  from our previous work and fixes a mistake in the treatment of initialisations.

Based on this fixed point semantics we propose the notion of *Input Berry-constructiveness* (IBC) for synchronous programs. This new IBC class lies properly between *strong* (SBC) and *normal Berry-constructiveness* (BC) defined in previous work. SBC and BC are two ways to interpret the standard constructive semantics of synchronous programming, as exemplified by imperative SMoCC languages such as Esterel or Quartz. SBC is often too restrictive as it requires all variables to be initialised by the program. BC is too permissive because it initialises all variables to a fixed value, by default. Where the initialisation happens through the memory, *e.g.*, when carrying values from one synchronous tick to the next, then IBC is more appropriate.

IBC links two levels of execution, the macro-step level and the micro-step level. We prove that the denotational fixed point analysis for IBC, and hence Berry's causality analysis, is sound with respect to operational micro-level scheduling. The denotational model can thus be viewed as a compositional presentation of a synchronous scheduling strategy that ensures reactiveness and determinacy for imperative concurrent programming.

Joaquín Aguado · Michael Mendler

Faculty of Information Systems and Applied Computer Sciences, Bamberg University, Germany

E-mail: {joaquin.aguado,michael.mendler}@uni-bamberg.de

Reinhard von Hanxleden  $\cdot$  Insa Fuhrmann

Department of Computer Science, Kiel University, Germany

E-mail: {rvh, ima}@informatik.uni-kiel.de

**Keywords** Denotational semantics  $\cdot$  concurrency  $\cdot$  determinism  $\cdot$  constructiveness  $\cdot$  Mealy reactive systems  $\cdot$  synchronous programming  $\cdot$  Esterel

#### 1 Introduction

#### 1.1 Motivation

Arguably the mathematically most satisfactory way to define a compositional programming language semantics is the denotational approach which defines the semantics of a program through a system of structurally-recursive equations involving continuous functions on abstract semantic domains. Compositionality is built into a denotational model at the outset, in the sense that the functional defining of the fixed-point semantics of a composite program entirely depends on the abstract functional denotation of its components rather than their syntax. As a consequence, algebraic axiomatisations for program verification and program transformations can be derived from the properties of these functions in the abstract domains.

Unfortunately, denotational fixed point models for computationally rich programming languages are notoriously hard to come by. A famous case in point is the long search for a fully-abstract denotational model of the functional language PCF [13,1,45]. It is the tight interaction of program components, in particular for non-deterministic concurrent systems, that makes it hard to decouple a composite program into a system of continuous functions in a simple way. It is often easier to understand the interaction behaviour of a concurrent program operationally in terms of inductive relations rather than recursive functions. Hence, many concurrent programming models or process algebras, for that matter, are based on Plotkin-style structural operational semantics. Such models are then turned into an algebra through notions of behavioural congruences and pre-congruences. Thereby abstracting from behaviourally unobservable information carried by the operational rule system one achieves the desired algebraic compositionality, see, *e.g.*, [66, 10]. However, denotational semantics generated in this fashion are essentially syntactic. Recursion is not explained by denotational fixed points but by syntactic unfolding.

One can do better if the inductive operational rules satisfy certain structural constraints, such as the GSOS or tyft/tyxt format. In these cases, general techniques are known to derive independent denotational semantics based on the approximation of a process by finite synchronization trees, see *e.g.* [2,46,29] for full-abstraction results for bisimulation-style semantics. Still, these approximation-based denotational models have their own problems. They are algebraically rather involved and depend on infinitary proof rules which fall outside the scope of normal (Horn-style) equational reasoning. One classical instance of this problem is the observation that, *e.g.*, bisimulation equivalence for process algebras with the empty process 0, non-deterministic choice p+q, action prefix a. p and recursion  $\mu x$ . p(x), does not admit a finitary denotational semantics based on complete partial orderings. Specifically, the Park induction principle,  $p(y) = y \Rightarrow \mu x$ .  $p(x) \le y$ , expressing that  $\mu x$ . p(x) is the least fixed point is inconsistent with monotonicity of the choice operator +. It is unclear if bisimulation-style semantics can be finitely axiomatised in equational Horn logic, see *e.g.* [64]. Denotational fixed point semantics with Park induction seem to exist only in special cases, such as acceptance testing, trace equivalence or simulation preorder [41,50,28].

While it is now clear that complex algebraic machinery is needed to reconcile genuinely independent denotational and operational semantics for general non-deterministic process

calculi, attention should turn once again to more special concurrent programming models. An early and successful starting point is the data-flow semantics of Kahn networks [47] which is fully-abstract for coroutine-style operational execution [48]. Kahn process nodes are sequential and deterministic and thus fairly restricted in modelling distributed systems. Yet, as discovered by Kok [49], non-determinism can be added to the Kahn model without losing full-abstraction using (*local*) *clocks* for the synchronisation of streams. This remarkable result brings into view an important special class of concurrent programming languages where denotational and operational approaches may go well together, known as the synchronous programming paradigm [33,9].

The Synchronous Model of Concurrent Computation (SMoCC) started in the 1980s with languages such as Statecharts [39,70], Lustre [19,34], Signal [32], Esterel [14,11] and Argos [62,63]. Developing concurrently with the emerging theory of process algebras, the SMoCC, from its beginning, has taken a practical programming perspective and targeted embedded and safety-critical systems in the automotive and avionics industries. The SMoCC languages have been very successful in these highly-demanding and complex domains. Part of this is due to their solid mathematical underpinning which inherits its robust logic from the design of digital synchronous circuits. Over the years, the quality-software assurance of the SMoCC paradigm has received attention in a wider range of applications. These include simulation Stateflow [35], web-orchestration [15], and music accompaniment [7] to mention a few. The SMoCC approach also has spread into functional programming [61] and mainstream imperative languages like C [16,52,36] or Java [67].

The SMoCC paradigm is based on a globally synchronous, locally asynchronous model of concurrent computation<sup>1</sup>, which employs logical clocks to force asynchronous processes into a globally deterministic sequence of execution steps, called *macro steps* or *logical instants*. The SMoCC computations relate to classical automata in the sense that macro-steps correspond to automata transitions and configurations are discrete time points (automata states) on which system and environment can communicate (synchronise) with each other. At this level of modelling—under the Synchrony Hypothesis [9]—macro-steps appear as deterministic and functional input/output interactions. If this were all, synchronous programs could be analysed by the standard compositional techniques of the theory of synchronous automata, which fits both the denotational and the operational viewpoint equally well. Not much concurrency theory is needed for that.

However, there is a catch: The soundness of the automata model depends on the compiler verifying that the Synchrony Hypothesis is valid. Yet, the Synchrony Hypothesis is not compositional. The difficulty is that the SMoCC programs exhibit Mealy as opposed to Moore-style interaction. Since Mealy outputs depend instantaneously on the inputs and (in a typical SMoCC language) are also broadcast, the atomicity assumption creates a tangled causality cycle when the SMoCC automata are composed. Since each program acts as the environment of the other, the Synchrony Hypothesis expects each system to react faster than the other, and hence faster than itself! This is aggravated by the fact that in some SMoCC languages, such as Esterel or some version of Statecharts, the reaction of one component can depend on the absence of a reaction from another component. To resolve the paradoxes, *i.e.*, to prevent deadlock and non-determinism, the synchronous interaction must satisfy stringent causality requirements. Consequently, causality analyses have been a key component in the SMoCC compilers. Typically, these analyses correspond to the derivation of clock schedules

<sup>&</sup>lt;sup>1</sup> This is sometimes referred to as the 'LAGS' model and not to be confused with the well-known but orthogonal 'GALS' model which features globally asynchronous and locally synchronous computations.

("clock calculus") for the activation of program statements [20,8,22,80] or 3-valued circuit simulation ("ternary analysis") [12,26,76]. Edwards [25] and Potop-Butucaru et al. [71] provide good overviews of compilation challenges and approaches for concurrent languages, including synchronous languages. In this article we focus on causality in control-flow oriented SMoCCs such as Esterel or Quartz rather than data-flow oriented SMoCCs such as Lustre or Signal.

The techniques for causality analysis range from checking simple static criteria on control-dependencies to full-fledged data-dependent control-flow analysis. Proving the soundness of causality analyses necessarily requires maintaining some form of refinement ("constructiveness" or "dependency") information about a lower-level asynchronous *micro-step* semantics. The first to observe this were Huizing, Gerth and de Roever [44] who showed that combining compositionality, causality and the Synchrony Hypothesis cannot be done within a single-levelled semantics (see also [73]). In other words, causality analysis establishes consistency of a *synchronous* macro-step with respect to an *asynchronous* micro-step execution model. This makes causality analyses and their soundness properties interesting from a concurrency theoretical point of view.

Different distributed execution platforms and memory models induce different degrees of uncontrollable non-determinism. They give thus rise to different notions of causality. A conservative, and thus robust, notion of causality among all the SMoCCs is the so-called constructive semantics of Esterel [14,11] introduced by Berry in [12]. This is a pure macrostep semantics combining a structural operational semantics for macro-state transitions with a denotational fixed-point construction, also known as the "must-cannot" analysis, for computing causal reactions from every state. However, there do not seem to be soundness proofs for the causality analyses of Esterel relative to a micro-level scheduling in normal, i.e., unsynchronised memory.<sup>2</sup> The only available result on the lower-level operational soundness of the fixed-point construction is indirect, has never formally been proven and applies to the hardware translation given in [12]. At the hardware level it is known that constructiveness implies delay-insensitivity under non-inertial delays [59,78,65]. While this highlights the universal nature of the constructive semantics, it does not provide insights into the nature of constructiveness for software implementations of SMoCC languages. This question is now starting to be addressed in the literature. An interesting example is the more recent SMoCC language Quartz [74]. It has been given both macro-step operational semantics and a fixed-point semantics implementing an Esterel-style causality analysis [74, 31]. Talpin et. al. in [79] consider a combination of Signal and Quartz and prove that the constructive fixed-point semantics is sound for an operational micro-step semantics. In this article we proceed along similar ideas as [79] for Esterel-style imperative languages.

#### 1.2 Contributions

In this article we prove the soundness of the denotational fixed point semantics for imperative SMoCC programs, commonly termed "constructive", with respect to their micro-step operational behaviour when compiled into multi-threaded shared memory code. To the best of our knowledge this is the first result of its kind for Esterel-style imperative programming.

<sup>&</sup>lt;sup>2</sup> There is an informal sketch of a micro-step semantics in [12][Sec. 4.3] which is not developed further or formally related with the fixed point semantics for macro-steps.

The recent constructive semantics that integrates Quartz and Signal [79] is based on a similar approach than the one proposed here in the sense that both are developed around similar mathematical structures, i.e., fixed point on a lattice for representing signal statuses and Boolean values. The semantics framework of [79] unifies the behaviour of polychronous multi-clocked Signal networks and synchronous Quartz modules where synchronous Boolean variables are always present. In contrast, our approach significantly extends the standard 3-valued "must-cannot" semantics [12,26,76] with the effect that (i) it is able to handle explicit initialisation of signals, and (ii) it operates in a more structured domain of information intervals rather than flat ternary Kleene algebra. In the enriched domain we prove soundness of the fixed-point with respect to the micro-step operational execution. By "micro-step operational semantics" we mean a small-step semantics in which the reaction of a parallel composition for a single clock tick (rather than sequences of clocks) is (1) implemented by thread interleaving and (2) the execution does not use the must/cannot enriched statuses. E.g., the SOS reaction rules for Quartz in [74,31] do not satisfy criterion (1). They give big-step semantics for full reaction instants. On the other hand, the operational semantics sketched by Berry in [12][Chap. 4.3] or by Talpin et.al. in [79] do not satisfy criterion (2).

Our main Theorem 1 strengthens the results presented in [4] where a similar fixed point semantics was introduced to prove that the sequentially constructive model of synchronous concurrent computation [37,38] conservatively extends Berry's notion of constructiveness for Esterel. Specifically, we extend the work of [4] in three ways: Firstly, we correct a mistake preventing the denotational semantics of [4] from detecting deadlocks that can arise from concurrent initialisations (see our Ex. 19). Secondly, the results presented here imply that the fixed point analysis is not only sound for sequential constructiveness targeted in [4] but also for Esterel's more restrictive operational model of causality, characterised by B-reactiveness (Def. 4) and SC-read-determinacy (Def. 5). The combination of these two properties is a proper strengthening of the notion of  $\Delta_*$ -constructiveness in the sense of [4], which corresponds to the notion of sequential constructiveness introduced in [37]. Thirdly, we introduce a new definition of constructiveness, called *IB-constructiveness* (Def. 9), to permit implicit initialisations through memory. It is more generous than the notions of constructiveness considered in [4] where all variables must be reinitialised, by the program or the environment, at every macro step. In other words, compared to [4] our semantics guarantees a stronger form of operational robustness for a wider class of programs.

### 1.3 Overview

Section 2 gives an abstract account of the SMoCC principle for imperative programs based on the consolidated language model pSCL and the operational notion of free scheduling. It also offers the definitions of important terms that will be used in the following sections, particularly of B-Admissibility and SC-Admissibility, which are both scheduling protocols restricting the free scheduling with different degrees of strength. The related terms of B-Reactiveness and SC-Reactiveness are also defined as well as the notion of X-Determinacy, parametric in X-Admissibility and its special case X-read-determinacy.

Section 3 is dedicated to the definition of the abstract domains and environments on which our denotational fixed point semantics is based. This includes the definition of the domain  $\mathbb{D}$ , whose four elements represent possible signal statuses and comprise representations needed for the handling of explicit initialization of signals. The semantics operates on closed intervals over  $\mathbb{D}$  which represent predictions of variable statuses combined with a domain  $\mathbb{P}$  that is

capturing initialization statuses, yielding  $I(\mathbb{D},\mathbb{P})$  as working domain. Finally, the section introduces a domain  $I(\mathbb{C})$  of program completion statuses.

Section 4 is the core of the article, where we put the introduced technical apparatus to form our denotational fixed point semantics for pSCL. The semantics induces three notions of constructiveness increasing in strength, Berry-constructive (BC), Input Berry-constructive (IBC) and Strong Berry constructive (SBC). This section finally contains our main Soundness Theorem 1 that states that IBC programs are B-reactive and SC-read-determinate.

Section 5 concludes this article and positions our work in reference to related work.

### 2 Operational Semantics of Synchronous Programs

### 2.1 Language Model

For our elaborations, we employ a language that focuses on the micro-step computations of a system. This language, referred to as pSCL<sup>3</sup> contains the necessary control structures for capturing multiple variable accesses as they occur inside macro-steps. pSCL abstracts syntactic and control particularities of existing synchronous languages not directly related to our analysis. This not only provides generality to the results but also avoids over-complicating our formal treatment. pSCL is *pure* in the sense that it manipulates Boolean *variables* from a finite set V, which carry information over time by changing value in  $\mathbb{B} = \{0,1\}$ . A variable  $s \in V$  with value  $\gamma \in \mathbb{B}$  is denoted by  $s^{\gamma}$ . Here, 0,1 are used to code, respectively, the logical statuses *False* (absent, initialised) and *True* (present, updated) of a synchronous signal. The syntax of pSCL is given by the following BNF of operators:

```

P := \varepsilon

nothing

pause

s = false

(implicit unemit s in Esterel)

s = true

(emit s in Esterel)

| s ? P : P

if s then P else P (present s then P else P in Esterel)

|P|P

fork P par P join

rec p. P

p:P

declare program label (implicit in Esterel loop)

jump to label (generalises Esterel iteration)

goto p

```

Since our syntax is abstract in the style of process algebras we also indicate the more concrete syntax as used in control-flow languages SCL [37] and Esterel on the right of each operator.

Intuitively, the *empty* statement  $\varepsilon$  indicates that a given program has been completed. That is,  $\varepsilon$  corresponds to the termination situation in which there are no further tasks to be performed in this or any subsequent macro-step. The *pause* control  $\pi$  forces a program to yield and wait for a global tick. This means that the execution cannot not proceed any further during the current macro-step but it will be resumed in the next instant. The *reset* (init) |s| and *set* (update) |s| constructs modify the value of  $s \in V$  to  $s^0$  or  $s^1$ , respectively. The *conditional* control s ? P : Q has the usual interpretation in the sense that depending on the status 1 or 0 of the guard variable s either P or Q are executed accordingly. *Parallel*

<sup>&</sup>lt;sup>3</sup> This stands here for "pure Synchronous Constructive Language" indicating not only that signal variables in pSCL carry Boolean status but also that pSCL is a minimalistic version of control-flow synchronous languages in an abstract algebraic syntax.

composition  $P \parallel Q$  forks P and Q, so the statements of both are executed concurrently. This composition terminates (joins) when both components terminate, *i.e.*, both are completed in the sense of  $\varepsilon$ , not waiting in a pause  $\pi$ . When just one of the two components in  $P \parallel Q$  terminates while the other pauses, then  $P \parallel Q$  pauses. Otherwise, if one component terminates and the other does not pause or terminate then the computation continues from the statements of the other component until it terminates, too, or pauses. In the *sequential* composition P; Q, the statements of P are first completely executed. Then, the control is transferred to Q which, in turn, determines the behaviour of the composition thereafter. The operator  $rec \ p.P$  introduces a recursion *label* or *process name* P that can be used in its body P to reiterate the process using P as a jump label. The semantics is so that  $rec \ p.P$  is equivalent to its unfolding  $P\{rec \ p.P/P\}$ , where  $P\{Q/P\}$  denotes syntactic substitution. As done in process algebras we can use rec to fold up recursive equation systems modelling arbitrary forward and backward jumps in control-flow graphs.

By default, a conditional binds tighter than sequential composition, which in turn binds tighter than parallel composition; the loop prefix rec p has weakest binding power. As usual, brackets can be used for grouping statements to override the default associations. For instance, in the expression  $rec p.x ? \varepsilon : p$ ; !y the scope of the loop extends to the end of the expression as in  $rec p. ((x ? \varepsilon : p); !y)$  whereas  $(rec p.x ? \varepsilon : p)$ ; !y limits the scope and leave !y outside the loop. Similarly, brackets are needed, as in  $rec p.x ? \varepsilon : (p; !y)$ , to include !y into the else branch of the conditional.

Recursion without restrictions is too powerful for our purposes. We impose the following three *well-formedness* conditions on pSCL expressions which suffices to model the static structure of many standard synchronous programming languages:

- No jumps out of an enclosing parallel composition. This does not limit the power of the language, as for example aborts, traps and general gotos as proposed for/provided by Esterel or SHIM [81,82] can still be implemented by "chaining" jumps up the thread hierarchy, but has the advantage of a simple parallel/sequential control flow structure. Formally, in every loop  $rec\ p$ . P the label p must not lie within the scope of a parallel operator  $\|$ . For instance,  $rec\ q$ .  $P\|(!x;q)$  is not permitted while  $P\|(rec\ q$ . !x;q) is accepted. This makes sure that the static control structure of a program is a series-parallel graph (see [24]) and the number of concurrently running threads is statically bounded by this graph. In particular any given static thread cannot be concurrently instantiated more than once; A fresh thread instance only runs sequentially after all previous instances of the same static thread.

- Every loop  $rec\ p.P$  is  $clock\ guarded,\ i.e.$ , every free occurrence of label p in P lies within the sequential scope of a pause  $\pi$ . For instance,  $rec\ p.\pi$ ; p; is is clock guarded whereas  $rec\ p.!s$ ; p; is in not. Clock guarded processes are guaranteed to generate finite, terminating macro-steps. This corresponds to the standard requirement in Esterel to not have instantaneous loops.

- No loop label occurs both *free* and *bound* in an expression, where the notion of a free and bound label is as usual. This a standard restriction in process calculi, see e.g., [10]. For instance, rec p. ¡s ; (rec q. p ; q) ; q) is not allowed, whereas rec p. ¡s ; (rec r. p ; r) ; q) is accepted. This restriction avoids capturing of any free variable of rec p. P by a loop recursion in P in the syntactic unfolding P{rec p. P/p}.

Henceforth, *programs* are assumed to be expressions satisfying these conditions. Programs without the *rec* construct will be called *finite* programs, or *fprogs* for short.

The imperative statements of a pSCL program describe discrete changes of state at the level of micro-steps. An execution instance of a micro-step is called an *action*. The computation of a concurrent program gets described by a collection of *threads* (concurrent program fragments), each one performing actions independently and interacting with each other through shared memory. Generally, a computation depends on a distinction of actions happening sequentially after each other or concurrently. The sequential order is instantiated from sequential composition P;Q. Parallel composition  $P \parallel Q$  is the construct that provides the thread topology for achieving concurrency. The resulting tree-like structure of the parallel construct determines statically which actions belong to which individual thread. At run-time, these static threads get instantiated and executed. Every one of such instantiations must have its own local *control-state* and, therefore, is considered a *processs*. From this perspective, the *configuration* capturing the global state of a concurrent program at any given moment is determined by the local state of all its processes together with a shared *global memory*.

As in synchronous programming, a *micro-step* can take place when at least one process is *active*, *i.e.*, when it is able to execute an action realising a statement other than  $\pi$ . In this manner, a micro-step produces a change in the configuration resulting from a process executing an action that modifies its own local state and possibly the global memory. Thus, in the course of an instant, active processes induce micro-steps until every process either terminates or reaches a pause, thereby completing a *macro-step*. Then, from the resulting configuration, the environment can provide a fresh stimulus for continuing the computation with a new macro-step occurring in the next instant.

The interaction between processes at the micro-step level must be controlled according to some pre-established rules of *admissible* scheduling in order to enforce the Synchrony Hypothesis abstraction. For instance, suppose in  $P \parallel Q$ , program P performs a write to a variable x and Q concurrently reads x. Then, under the Synchrony Hypothesis the producer P (system) is faster than the consumer (environment)Q, or, equivalently, Q waits for P. A canonical notion of admissibility that enforces such causalities is the "init;update;read" protocol [37], which is referred to as the "iur" protocol in the following. It decrees that all initialisations is must take place before any update !s which in turn must both be scheduled before any read, i.e., any conditional test s ? P : Q on s.

In the next Sec. 2.2 we define the notion of a free unconstrained execution for pSCL programs and then in Sec. 2.3 introduce the restriction imposed by the iur protocol. This defines the operational semantics of the class of *causal* pSCL programs for which we shall later, in Secs. 3 and 4, provide a suitable notion of *constructive* macro-step responses in terms of a denotational fixed-point analysis.

### 2.2 Micro-step Free Scheduling.

In our operational model, a *process* T is defined by its own current *control-state*, or *state* for short, which contains: (i) information about the precise position of T in the tree structure of forked processes and (ii) control-flow references to specific parts of the code. Formally, T is given by a triplet  $\langle id, prog, next \rangle$  where we write T.id, T.prog or T.next for referring to the individual elements of T which are called, respectively, identifier, current-program and next-control. Concretely,

- *T.id* is a non-empty sequence containing an alternation of natural numbers and the symbols *l*, *r* that always starts and ends with a number. For instance, 0.*l*.5 and 1.*r*.3.*l*.7

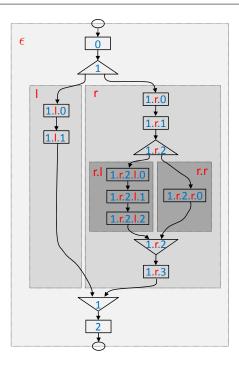

Fig. 1 A sequential-parallel program structure of thread identifiers.

are identifiers but 0.r and r.1.r.2 are not. Meta-variables to range over identifiers are  $\iota$ ,  $\kappa$ , possibly with indices.

- *T.prog* is the pSCL expression that is currently scheduled to generate *T*'s actions. Since these are pSCL expressions we use the meta-variables *P*, *Q*, *etc.*, to range over these.

- *T.next* is a list of future program fragments that can be converted into actions sequentially after *T.prog* has terminated. This list is extended when a sequential composition is executed in *T.prog*. We use the meta-variable *Ks* to range over next-controls.

The identifier T.id localises process T uniquely in the sequential-parallel control flow of the program context which has generated T. The intuition is that the numbers in the identifier are counting the sequential steps taken by the program context. The symbols (l for left and r for right) recall the path of previous parallel forks from which the process has emerged. Where we are only interested in the depth of a process in the thread hierarchy, we use a thread projection function  $th(t) \in \{l, r\}^*$  which drops from t all sequencing numbers. The sequence th(T.id) can be interpreted as the static thread identifier of process T.

*Example 1* The serial-parallel graph in Fig. 1 gives an example of the thread identifiers generated by the fprog  $P_{\varepsilon} = a_0$ ;  $(P_l \parallel P_r)$ ;  $a_2$  with

$$\begin{array}{ll} P_{l} = a_{1.l.0} \, ; \, a_{1.l.1} & P_{r} = a_{1.r.0} \, ; \, a_{1.r.1} \, ; \, (P_{r.l} \parallel P_{r.r}) \, ; \, a_{1.r.3} \\ P_{r.l} = a_{1.r.2.l.0} \, ; \, a_{1.r.2.l.1} \, ; \, a_{1.r.2.l.2} & P_{r.r} = a_{1.r.2.r.0}, \end{array}$$

where all  $a_i$  are primitive statements  $\{\varepsilon, !s, js\}$ . The subscripts  $\iota$  indicate the thread identifier associated with the action  $a_i$  when it is executed. In Fig. 1 these primitive statements are

shown as rectangular boxes with their identifier written inside it. Notice how the letters l and r (displayed in red colour) identify the static thread in which the action is executed. For instance the action  $a_{0.r.2.l.1}$  is executed in the static thread r.l, which is the left child of the right child of the main thread. This is the projection th(0.r.2.l.1) = r.l. The first top level action  $a_0$  is in the root thread  $\varepsilon$ , i.e.,  $th(0) = \varepsilon$ , where  $\varepsilon$  denotes the empty sequence. The hierarchical thread structure is visualised by the dotted gray background boxes.

**Definition 1** To compare the sequential depth of processes, we use the (partial) lexicographic order  $\prec$  on path identifiers. The natural numbers are ordered in the usual way, i.e.,  $0 < 1 < 2 \ldots$  while the symbols l, r are considered incomparable. Thus, for identifiers  $\iota = d_1 \ldots d_n$  and  $\iota' = d'_1 \ldots d'_m$  we have that  $\iota \prec \iota'$  iff  $\iota$  is a proper prefix of  $\iota'$  or  $\iota$  is lexically below  $\iota'$ , formally:

```

- n < m and \forall 1 \le j \le n. d_j = d'_j, or - there is 0 \le i < n such that d_{i+1} < d'_{i+1} and \forall 1 \le j \le i we have d_j = d'_j.

```

We write  $\leq$  for the reflexive closure of  $\prec$ , *i.e.*,  $\iota \leq \iota'$  iff  $\iota \prec \iota'$  or  $\iota = \iota'$ .

The order  $\leq$  contains both the thread hierarchy and sequencing. If  $\iota \leq \iota'$  then  $\iota'$  is a sequential successor of  $\iota$  in program order. If  $\iota \not\leq \iota'$  and also  $\iota' \not\leq \iota$  then both  $\iota$  and  $\iota'$  are concurrent. Note that there is no relationship between  $\iota \prec \iota'$  and the prefix order on  $th(\iota)$  and  $th(\iota')$ . The sequential successor  $\iota'$ , in general, can be both a descendant or an ancestor of  $\iota$  in the thread hierarchy.

Example 2 For instance, in our example of Fig. 1, we have  $1.r.2 \prec 1.r.2.l.1 \prec 1.r.3$  following the sequential program order but  $1.l.0 \not\prec 1.r.2.l.1$  and  $1.r.2.l.1 \not\prec 1.l.0$ , because the labels l and r are incomparable. The actions with thread identifiers 1.l.0 and 1.r.2.l.1 are not sequentially ordered. They are executed in the concurrent threads th(1.r.2.l.1) = r.l and th(1.l.0) = l. Observe that  $1.r.2.l.1 \preceq 1.r.3$  but th(1.r.2.l.1) = r.l is not a prefix of r = th(1.r.3). In the other direction, the fork node 1.r.2 is a sequential predecessor of 1.r.2.l.1 and r = th(1.r.2) is an ancestor of r.l = th(1.r.2.l.1).

Formally, the *global memory* is a Boolean valuation function  $\rho: V \to \mathbb{B}$  which indicates the current value for each variable  $s \in V$ . Any action of a process T (relative to a given memory  $\rho$ ) produces a new memory  $\rho'$  and a set of *successor processes* T'. Thus, any action is completely specified by the *memory* function  $\rho' := mem(T, \rho)$  and the *succession* function  $T' := nxt(T, \rho)$ . For any  $x \in V$ , the memory function is defined by:

$$mem(T, \rho)(x) := \begin{cases} 0 & \text{if } T.prog = \text{; } s \text{ and } x = s \\ 1 & \text{if } T.prog = \text{! } s \text{ and } x = s \\ \rho(x) & \text{otherwise.} \end{cases}$$

This says that for a given variable  $s \in V$ , if T performs a reset s then s is changed to 0, if T performs a set s then s is changed to 1, otherwise, s keeps its value from the previous memory. We define the succession  $nxt(T, \rho)$  by case analysis on T.prog, where the sequential enumeration for identifier t is computed by an increment function inc(t) which increases by

1 the last number of the identifier  $\iota$ , e.g., inc(1.r.6) = 1.r.7:

$$nxt(\langle \iota, P, [] \rangle, \rho) := \emptyset \text{ if } P \equiv \varepsilon, P \equiv \mathfrak{f} \text{ or } P \equiv \mathfrak{f} \text{s}$$

(1)

$$nxt(\langle \iota, P, Q :: Ks \rangle, \rho) := \{\langle inc(\iota), Q, Ks \rangle\} \text{ if } P \equiv \varepsilon, P \equiv \varepsilon \text{ or } P \equiv \varepsilon \text{ s}$$

(2)

$$nxt(\langle \iota, P; Q, Ks \rangle, \rho) := \{\langle \iota, P, Q :: Ks \rangle\}$$

(3)

$$nxt(\langle \iota, rec \, p. P, Ks \rangle, \rho) := \{\langle \iota, P\{rec \, p. P/p\}, Ks \rangle\} \tag{4}$$

$$nxt(\langle \iota, s ? P : Q, Ks \rangle, \rho) := \begin{cases} \{\langle inc(\iota), P, Ks \rangle\} & \text{if } \rho(s) = 1 \\ \{\langle inc(\iota), Q, Ks \rangle\} & \text{otherwise} \end{cases}$$

(5)

$$nxt(\langle \iota, P \| Q, Ks \rangle, \rho) := \{ \langle \iota, \varepsilon, Ks \rangle, \langle \iota.l.0, P, [] \rangle, \langle \iota.r.0, Q, [] \rangle \}. \tag{6}$$

Let us explain the different cases one by one:

- (1) If the program T.prog is one of the basic statements (*i.e.*, empty  $\varepsilon$ , set !s or reset ;s) and the list of continuation processes in the next-control T.next is empty [], then the process (after execution) is terminated and disappears from the configuration. This is achieved by setting the succession to be the empty set.

- (2) If T.prog is one of the basic statements and the list of continuation processes in T.next is a non-empty list Q::Ks, then we start Q in a new process with next-control Ks and a sequentially incremented index inc(1).

- (3) If T.prog is a sequential composition P; Q then we start P in a new process with the same identifier and add Q to the front of the next-control list. The identifier does not increment since we do not consider the new process  $\langle \iota, P, Q :: Ks \rangle$  a sequential successor but only a structural replacement.

- (4) A loop T.prog = rec p. P behaves like its unfolding  $P\{rec p. P/p\}$ , without modification to the identifier and next-controls.

- (5) Next consider a process with conditional program T.prog = s? P:Q in memory  $\rho$ . Depending on whether the memory value for the variable s is 1 or 0 we install the P or the Q branch, respectively, with an incremented identifier and the same next-control. The identifier is incremented because the branches are considered as being executed strictly after the conditional test, in sequential program order.

- (6) Finally, executing a parallel program  $T.prog = P \parallel Q$  instantiates the two sub-threads P and Q in their own process  $\langle t.l.0, P, [] \rangle$  and  $\langle t.r.0, Q, [] \rangle$ , respectively, with a fresh and empty next-control but extended identifiers. The process P is the *initial* sequential statement of the *left* child of the parent process  $\langle t, P \parallel Q, Ks \rangle$ . Therefore, we add the suffix l.0 to the parent's identifier, and analogously r.0 for the right child Q. At the same time that the parent process forks its two children it transforms itself into a join process  $\langle t, \varepsilon, Ks \rangle$ . Since  $t \prec t.l.0$  and  $t \prec t.r.0$  both children have strictly larger identifiers. Since only processes with maximal identifiers are executable (details below), the join process must wait for the children to terminate before it can release the next-controls Ks, or terminate itself in case Ks = [].

Note that there is no clause for the succession of a pausing process or a process label, *i.e.*,  $nxt(\langle \iota, \pi, Ks \rangle, \rho)$  and  $nxt(\langle \iota, p, Ks \rangle, \rho)$  are undefined. This is no problem since (i) program  $\pi$  is never executed in a micro-step action but only by the next global clock tick (see below), and (ii) we are only interested in the behaviour of *closed* pSCL expressions which do not have any free process labels.

Example 3 Consider the process  $T_0 = \langle 0, x; y ? \pi : !x, [] \rangle$ . This process resets variable x and then either pauses or sets variable x depending on the value of variable y. Let us derive its behaviour in the formal semantics.

Starting from some initial memory  $\rho_0$ , executing  $T_0$  yields a new memory  $\rho_1 = mem(T_0, \rho_0)$  and a set of successors  $S_1 = nxt(T_0, \rho_0)$ . This first action breaks up the sequential composition operator; according to rule (3). This results in  $S_1 = \{T_1\}$  where  $T_1 = \langle 0, ix, [y?\pi:!x] \rangle$ . The action does not modify the memory, i.e.,  $\rho_1 = \rho_0$ . Proceeding with  $T_1$  from  $\rho_1$ , we come to execute the reset ix following rule (2), obtaining  $\rho_2 = mem(T_1, \rho_1)$  and successors  $S_2 = nxt(T_1, \rho_1)$ . Memory  $\rho_2$  now assigns 0 to variable x, while y retains its initial value from  $\rho_0$ . The succession is  $S_2 = \{T_2\}$  with  $T_2 = \langle 1, y?\pi:!x, [] \rangle$ . Notice the increment of the identifier  $T_2.id = 1 = inc(0) = inc(T_1.id)$  which reflects the fact that execution has passed a sequential composition operator. The conditional  $T_2$  now reads the value of y in memory  $\rho_2$  and passes control to the 'then' or 'else' branch:

- If  $\rho_2(y) = \rho_0(y) = 1$  then the conditional executes the 'then' branch. We get  $\rho_3 = mem(T_2, \rho_2) = \rho_2$  and  $S_3 = nxt(T_2, \rho_2) = \{T_3\}$  with  $T_3 = \langle 2, \pi, [] \rangle$  by rule (5). There are no micro-step rules for  $\pi$  which is forced to pause during the current synchronous instant.  $T_3$  makes progress only at the next global clock tick where it transforms into  $T_3' = \langle 0, \varepsilon, [] \rangle$  as described later.

- If  $\rho_2(y) = \rho_0(y) = 0$  then  $\rho_3 = mem(T_2, \rho_2) = \rho_2$  and  $S_3 = nxt(T_2, \rho_2) = \{T_3\}$  with  $T_3 = \langle 2, !x, [] \rangle$  by rule (5). From here, the execution of !x sets variable x and yields the new memory  $\rho_4 = mem(T_3, \rho_3)$  with  $\rho_4(x) = 1$  and  $\rho_4(y) = \rho_2(y)$ . Since  $S_4 = nxt(T_3, \rho_3) = \emptyset$  by rule (1), there are no more processes from which we can continue. The execution of  $T_0$  has terminated instantaneously in the current synchronous instant.

Let us combine the memory and succession functions for a single process to define the micro-steps of an arbitrary set of processes running concurrently. This requires the notion of a *configuration*, defined next:

**Definition 2** A *configuration* is given by a pair  $(\Sigma, \rho)$ , where  $\rho$  is the global memory and  $\Sigma$ , called the *process pool*, is a finite set of (closed) processes such that

- all identifiers are distinct, *i.e.*, for all  $T_1, T_2 \in \Sigma$ , if  $T_1.id = T_2.id$  then  $T_1 = T_2$ ;

- the sequential ordering of identifiers coincides with the thread hierarchy, *i.e.*, for all  $T_1, T_2 \in \Sigma$ , we have  $T_1.id \leq T_2.id$  iff  $th(T_1.id)$  is a (not necessarily proper) prefix of  $th(T_2.id)$ ;

- the identifiers form a full thread tree, *i.e.*, for each  $T \in \Sigma$  and every proper prefix (ancestor)  $t \in \{r, l\}^*$  of th(T.id), there is a process  $T' \in \Sigma$  of T with th(T'.id) = t.

A configuration  $(\Sigma, \rho)$  is *empty* if  $\Sigma = \emptyset$ . We call a process  $T \in \Sigma$

- pausing when  $T.prog = \pi$ ;

- *active* if it is not pausing and T.id is  $\leq$ -maximal (identifier order) in  $\Sigma$ ;

- waiting if it is neither pausing nor active.

A configuration with memory  $\rho$  in which all the processes in  $\Sigma$  are waiting or pausing, is called *quiescent*.

*Micro-sequences*. From a given configuration  $(\Sigma, \rho)$  and a selection  $T \in \Sigma$  of an active process, we can let T execute an action to produce a *micro-step*

$$(\Sigma, \rho) \xrightarrow{T} (\Sigma', \rho'),$$

(7)

where in the free scheduling there is no constraint on the selection of T other than it being active. The resulting memory  $\rho' = mem(T, \rho)$  is computed directly from the *mem* function.

The new process pool  $\Sigma'$  is obtained by removing T from  $\Sigma$  and replacing it by the set of successors generated by nxt, i.e.,  $\Sigma' = \Sigma \setminus \{T\} \cup nxt(T,\rho)$ . Note that in the free schedule both the next process pool  $\Sigma'$  and the new memory  $\rho'$  only depend on the active process T that is executed and the current memory  $\rho$ . They do not depend on the other processes in  $\Sigma$ . Since the successor configuration is uniquely determined by  $(\Sigma,\rho)$  and T, we may write  $(\Sigma',\rho') = T(\Sigma,\rho)$ . In a *micro-sequence* the scheduler runs through a succession

$$(\Sigma_0, \rho_0) \xrightarrow{T_1} (\Sigma_1, \rho_1) \xrightarrow{T_2} \cdots \xrightarrow{T_k} (\Sigma_k, \rho_k)$$

(8)

of micro-steps obtained from the interleaving of process executions. We let  $\rightarrow$  be the reflexive and transitive closure of  $\rightarrow$ . That is, we write

$$R: (\Sigma_0, \rho_0) \rightarrow (\Sigma_k, \rho_k)$$

to express that there exists a micro-sequence R, not necessarily maximal, from configuration  $(\Sigma_0, \rho_0)$  to  $(\Sigma_k, \rho_k)$ . The sequence R is a function mapping each index  $1 \le j \le k$  to the process  $R(j) = T_j$  executed at micro-step j and len(R) = k is the length of the micro-sequence, *i.e.*, the number of actions executed so far. We call any pair (i, R(i)) consisting of a micro-step index  $1 \le i \le len(R)$  together with the process R(i) executed at position i, a process instance of R. Further, it will be necessary to restrict a micro-sequence  $R: (\Sigma_0, \rho_0) \twoheadrightarrow (\Sigma_n, \rho_n)$  to its prefixes  $R@i: (\Sigma_0, \rho_0) \twoheadrightarrow (\Sigma_i, \rho_i)$  for  $i \le n = len(R)$ .

Macro-steps. A macro-step, also called a synchronous instant, or instant for short, abbreviated

$$R: (\Sigma_0, \rho_0) \Longrightarrow (\Sigma_k, \rho_k)$$

(9)

is a maximal micro-sequence R that reaches a final quiescent configuration. Note that for any memory  $\rho$ , a configuration  $(\emptyset, \rho)$  is trivially quiescent. For the sake of simplicity, sometimes we drop the mapping M from our relations  $\twoheadrightarrow$  and  $\Longrightarrow$ . When  $(\Sigma_k, \rho_k)$  is quiescent but non-empty then no further micro-step is possible (which explains the term 'quiescent') since all processes are waiting for the clock to tick. Such a clock tick

$$(\Sigma_k, \rho_k) \Longrightarrow^{tick} (\Sigma', \rho') \tag{10}$$

consists of eliminating every pausing process with empty continuation  $\langle \iota d, \pi, [] \rangle \in \Sigma_k$  and replacing every pausing process  $\langle \iota d, \pi, Q :: Ks \rangle \in \Sigma_k$  with a non-empty continuation by a new process  $\langle \iota 0, Q, Ks \rangle \in \Sigma'$  preserving the sequential identifier of all ancestors but restarting the current thread at sequence number 0. The new memory  $\rho'$  preserves all internal and output variables but permits the environment to change any input variables for the next macro-step. For the investigations in this article, however, we are only interested in single macro-steps generated by the behaviour of pSCL expressions. Therefore, we will not be concerned with the modelling of successions of clock ticks.

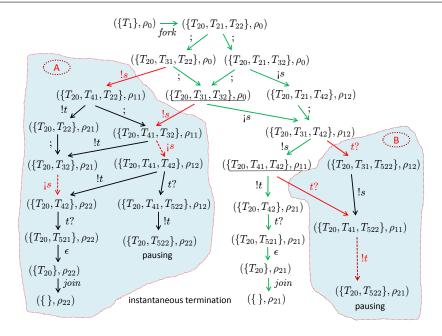

Example 4 Let  $(\Sigma_1, \rho_0)$  be a configuration where  $\rho_0$  gives value 0 to every variable and the process pool  $\Sigma_1 = \{T_1\}$  consists of the root process:  $T_1 = \langle 0, (!s; !t | | ;s; t? \varepsilon : \pi), [] \rangle$ . The complete computation graph for the free scheduling from  $(\Sigma_1, \rho_0)$  is depicted in Fig. 2. The processes are abbreviated as follows:

$$\begin{array}{lll} \text{re abbreviated as follows:} \\ T_{1} &= \langle 0, !s \; ; !t \; || \; ;s \; ;t \; ? \; \varepsilon : \pi, [] \rangle & T_{31} &= \langle 0.l.0, !s, [!t] \rangle \\ T_{20} &= \langle 0, \varepsilon, [] \rangle & T_{32} &= \langle 0.r.0, ;s, [t \; ? \; \varepsilon : \pi] \rangle \\ T_{21} &= \langle 0.l.0, !s \; ; !t, [] \rangle & T_{41} &= \langle 0.l.1, !t, [] \rangle \\ T_{22} &= \langle 0.r.0, ;s \; ;t \; ? \; \varepsilon : \pi, [] \rangle & T_{42} &= \langle 0.r.1, t \; ? \; \varepsilon : \pi, [] \rangle \\ T_{521} &= \langle 0.r.2, \varepsilon, [] \rangle & T_{522} &= \langle 0.r.2, \pi, [] \rangle \\ \end{array}$$

Fig. 2 The free scheduling graph of process  $T_1$  of Ex. 4

Each edge in Fig. 2 is a single micro-step. For ease of explanation we do not use the selected process  $T_i$  as the label like in (7) but instead the primitive operator executed in the action, *i.e.*, a sequential composition; (rule (3)), atomic set, reset or the empty statements !s, !t, ¡s,  $\varepsilon$  (rules (1) and (2)) or a parallel composition  $\parallel$  (rule (6)). The shaded regions named A and B will be explained later.

Since  $T_1$  is active it can induce the micro-step  $(\Sigma_1, \rho_0) \to (\Sigma_2, \rho_0)$  with the a succession  $\Sigma_2 = \{T_{20}, T_{21}, T_{22}\}$  of three processes as a result of executing the parallel fork, the parent  $T_{20}$ and its two children  $T_{21}$  and  $T_{22}$ . Observe that in  $\Sigma_2$  the two children are active but the parent with identifier 0 is waiting, because 0 < 0.l.0 and 0 < 0.r.0. The parent  $T_{20}$  now plays the role of a 'join' in the sense that it cannot execute any action until the two children terminate and its own identifier becomes maximal again. Let us suppose that  $T_{21}$  and  $T_{22}$  are scheduled in that order to get  $(\Sigma_2, \rho_0) \rightarrow (\Sigma_4, \rho_0)$  with  $\Sigma_4 = \{T_{20}, T_{31}, T_{32}\}$ , where  $T_{31}$  and  $T_{32}$  are both active. The configuration  $(\Sigma_4, \rho_0)$  is underlined in Fig. 2. Notice that we reach exactly the same configuration if we first schedule  $T_{22}$  and then  $T_{21}$ . The concurrent execution of the sequential compositions in  $T_{21}$  and  $T_{22}$  is confluent, because there are no read or write accesses to variables. However, in  $(\Sigma_4, \rho_0)$  things become interesting since the chosen scheduling order will result in different configurations. For if  $(\Sigma_4, \rho_0) \rightarrow (\Sigma_6, \rho_{11})$ , with  $\Sigma_6 = \{T_{20}, T_{41}, T_{42}\}$ , results from scheduling  $T_{32}$  followed by  $T_{31}$ , then first the reset is is performed and thereafter the set !s, so that  $\rho_{11}(s) = 1$ . On the other hand, if first  $T_{31}$  is picked and then  $T_{32}$  does its initial action, then  $(\Sigma_4, \rho_0) \rightarrow (\Sigma_6, \rho_{12})$  with  $\rho_{12}(s) = 0$ . Although the resulting process pool  $\Sigma_6$  is the same in both configurations, the global memory is not.

Continuing the schedule from configuration  $(\Sigma_6, \rho_{11})$ , also underlined in Fig. 2, we see that there is a race between the reading of variable t by  $T_{42}$  the writing to t by  $T_{41}$ . If we first execute  $T_{41}$ , then the conditional  $T_{42}$  will activate its 'then'-branch  $\varepsilon$ . Therefore, we eventually reach the configuration  $(\Sigma_9, \rho_{21})$  with  $\Sigma_9 = \{T_{20}\}$  where the memory satisfies  $\rho_{21}(s) = T_{20}(s)$

$\rho_{21}(t)=1$ . Now 'join' process  $T_{20}$  becomes active which instantaneously terminates reaching the quiescent configuration  $(\{\},\rho_{21})$ . On the other hand, if in  $(\Sigma_6,\rho_{11})$  the process  $T_{42}$  first gets to test the value of t, which is 0, before  $T_{41}$  sets it to 1, then the 'else'-branch is selected and we end up in the configuration  $(\Sigma_8,\rho_{21})$  where  $\Sigma_8=\{T_{20},T_{522}\}$ . This configuration is also quiescent as it contains no active processes. Here, the 'join' process  $T_{20}$  is still waiting since it has a strictly smaller sequence number than process  $T_{522}$  which is pausing. No progress can be made until the next clock tick makes  $T_{522}$  disappear from the configuration, thereby activating  $T_{20}$  which then terminates instantaneously. Note that the conflict between  $T_{41}$  and  $T_{42}$  in  $(\Sigma_6,\rho_{11})$  results in a non-determinism of control, viz. between terminating in the same instant or the next.

Clearly, as demonstrated in Ex. 4 the selection strategy applied in the free scheduling of a program determines the final memory content and termination behaviour of a program in a macro-step. If we would consider pSCL as a just another clocked process algebra such as [42, 21,56] or a model of general statecharts, *e.g.*, [70,84,40] (or in fact Java threads, for that matter) the non-determinism would not worry us. It is a natural consequence of the asynchrony of parallel execution. We can leave it in the responsibility of the versed programmer to harness her or his programs by explicit synchronisation through shared memory mutual exclusion algorithms (see [58]) in order to get rid of non-determinacy. Yet, this is not the right approach for synchronous programming where every program, by compilation, is required to code a deterministic Mealy machine. In synchronous programming it is the compiler which has to achieve determinate tick responses under pessimistic assumption on the varying degree of perturbations arising from the non-determinism of target run-time system.

In synchronous programming the programmer is supported by static schedulability and causality analyses. Often non-determinism can be eliminated by restricting the free scheduling to so-called *admissible* schedules that are natural for, or intended by, the programmer and at the same time reliably implemented on the chosen run-time platform by a trusted compiler.

Example 5 Consider Example 4 in which the non-determinacy of the tick response is due to races between the setting and resetting of variable s and the reading and writing of variable t. Suppose we compile the root process  $T_0$  as a data-flow network in which the non-determinism maps to the concurrent execution of function blocks. Then it is easy to ensure that the data-flow always executes reset of a variable (value initialisation) before any set (value update) and all write accesses before the reads. This natural ordering prohibits the execution of the transitions shown in Fig. 2 as dashed arrows. It eliminates the path in region s in which the set action s happens after the reads s and the paths in region s with the resets s occurring after the sets s. The remaining admissible scheduling paths then all lead, deterministically, to instantaneous termination in configuration (s of s or s or

A canonical notion of admissibility to avoid causality locks is the "init;update;read" (iur) protocol, which forces the accesses of every variable to undergo strict cycles of first initialisations (*is*), then updates (*!s*) and finally reads (*s*?). Moreover, the iur protocol can be refined by limiting the number of initialisations that are permitted during a single macrostep on any variable. Liberal notions of sequential constructiveness permitting more than one init;update;read cycle have recently been proposed [37,38]. In the traditional model of synchronous programming—paradigmatically represented by Esterel—only one iur cycle is permitted. This leads to a more conservative notion of constructiveness which is the subject of this article and formalised in the next section.

Since well-formed pSCL programs are clock-guarded, we can unfold all loops and extract finite *rec*-free expressions that fully describe the program's macro step reactions. Therefore,

as the main results in this article concern the scheduling of actions inside a single finite macro-step, it suffices to consider only finite, recursion-free pSCL programs, *i.e.*, fprogs.

#### 2.3 Reactiveness and Determinacy.

All non-determinism of concurrent execution arises from two types of data races: write-write conflicts and write-read conflicts. To remove these races the iur scheduling protocol enforces precedence of resets over sets and of writes over reads. The strict ordering can be broken only if the variable accesses are confluent. A suitable notion of confluence has been introduced in [37,38].

**Definition 3 (Confluence of Processes)** Let  $T_1$  and  $T_2$  be two arbitrary processes and  $(\Sigma, \rho)$  a configuration. Then,

- 1.  $T_1, T_2$  are called *conflicting* in  $(\Sigma, \rho)$  if both  $T_1$  and  $T_2$  are active in  $\Sigma$  and  $T_1(T_2(\Sigma, \rho)) \neq T_2(T_1(\Sigma, \rho))$ ;

- 2.  $T_1, T_2$  are *confluent* in  $(\Sigma, \rho)$ , written  $T_1 \sim_{(\Sigma, \rho)} T_2$ , if there is no micro-sequence  $(\Sigma, \rho) \twoheadrightarrow (\Sigma', \rho')$  such that  $T_1$  and  $T_2$  are conflicting in  $(\Sigma', \rho')$ .

Example 6 As an illustration consider once more Example 4. Processes  $T_{31}$  and  $T_{32}$  are conflicting in configuration  $(\Sigma_4, \rho_0) = (\{T_{20}, T_{31}, T_{32}\}, \rho_0)$  because, as we have seen, both are active in this configuration and, moreover, different execution orders lead to different results. Since the action of  $T_{31}$  is !s (update) and the action of  $T_{32}$  is the reset ¡s (init), the scheduling protocol gives precedence to  $T_{32}$ . Similarly,  $T_{41}$  and  $T_{42}$  are in conflict in configuration  $(\Sigma_6, \rho_{12})$  with  $\Sigma_6 = \{T_{20}, T_{41}, T_{42}\}$  as can be seen from Fig. 2. For their part, processes  $T_{21}$  and  $T_{22}$  are independent or confluent in  $(\Sigma_2, \rho_0)$  with  $\Sigma_2 = \{T_{20}, T_{21}, T_{22}\}$ . This is so because in every micro-sequence  $(\Sigma_2, \rho_0) \rightarrow (\Sigma', \rho')$  the only configuration in which both  $T_{21}$  and  $T_{22}$  are active is precisely  $(\Sigma_2, \rho_0)$ . Furthermore, as can be seen from Fig. 2, the order of execution is unimportant in this case, namely  $T_{21}(T_{22}(\Sigma_2, \rho_0)) = T_{21}(T_{22}(\Sigma_2, \rho_0)) = (\Sigma_4, \rho_0)$ , where  $\Sigma_4 = \{T_{20}, T_{31}, T_{32}\}$ . Note that since the initial action of both  $T_{21}$  and  $T_{22}$  is the breaking up of the sequential composition, and thus not variable accesses, their ordering is unconstrained by the "init;update;read" scheduling protocol.

In this article we introduce a fairly stringent interpretation of the iur protocol derived from conservative SMoCCs such as Esterel or Quartz, which we term *Berry admissibility* (Def. 4 below). It uses confluence to permit "ineffective" sets after reads but is stronger than SC-admissibility [37], as it enforces the iur protocol on *all* accesses not just concurrent ones as in [37]. Whatever synchronisation protocol *X* we use —there may be many other interesting ones still to be discovered—the restriction to *X*-admissible executions not only reduces non-determinacy. Such synchronisation constraints may lead to deadlock, i.e., configurations in which no micro-step is possible without violating *X*-admissiblity. Thus we must care about *X*-reactiveness, *i.e.*, the property that a program does not get stuck when executed in an *X*-admissible fashion.

### 2.3.1 B-Admissibility and B-Reactiveness

The tighter the underlying notion of *X*-admissibility the more information we have from knowing that a program is *X*-reactive. If all X-admissible schedules are also Y-admissible then a program without deadlocks under X is also deadlock-free under Y. Here we introduce

a suitable notion of admissibility that captures the essence of Esterel which is tighter than *SC-admissibility* introduced in [37,38].

**Definition 4 (Berry Admissibility and Reactiveness)** A micro-sequence  $R: (\Sigma_0, \rho_0) \twoheadrightarrow (\Sigma_n, \rho_n)$  is *Berry admissible* (*B-admissible*) iff

- (1) R does not reset any variable that has been set before. Formally, if R(i) for  $0 < i \le n$  executes a set !s for some  $s \in V$ , then no R(j) for  $i < j \le n$  executes a reset ;s.

- (2) *R* does not write any variable which has been read before, unless this late write is ineffective in the sense that the write is confluent with the read and the very same value has been written already before the read.

Formally, if R(j) for  $0 < j \le n$  executes a conditional test s ? P : Q for some P, Q, and R(k) for  $j < k \le n$  performs a set !s (reset js), then there exists an index i < j before the read where R(i) already executed a set !s (reset js) and  $R(j) \sim_{(\Sigma_j, \rho_j)} R(k)$ .

An fprog P is called *Berry reactive* (*B-reactive*) if from every initial configuration  $(\{\langle 0, P, [] \rangle\}, \rho_0)$  there is at least one B-admissible instant.

Example 7 If a reset happens sequentially after a set (violating Def. 4(1)), as in  $P_1 := !s ; ; s$ , then this violates the monotonicity of signal stabilisation. In the conservative delay-insensitive model of Esterel this is a hazard, since a concurrent environment could read either the first output value s = 1 (which is interpreted as an emit) or the second s = 0 (which is an initialization). This creates a write-write race, thus jeopardising determinism.  $P_1$  does not have a B-admissible execution. The opposite ordering  $P_2 := ; s ; !s$  of a reset followed by a set is B-admissible, since it adheres to the monotonic stabilisation protocol.

A read-write race (violating Def. 4(2)) occurs in the sequential programs  $P_3 := s$ ? !s:  $\varepsilon$  and  $P_4 := s$ ? ¡s:  $\varepsilon$ . The write accesses !s and ¡s, respectively, may effectively overwrite the externally controlled value of s which is tested in the conditionals. If we consider  $P_3$  and  $P_4$  to be environments of themselves then we run into a causality loop: the test s? must wait until the program has set or reset its value, which however can only happen after the test has been executed. If R is the micro-sequence generated from  $P_3$  with initial memory  $\rho_0(s) = 1$  then it executes the set !s after the read s? without any set having happened before the read. Similarly, we get a reset ¡s after the read s? in  $P_4$  but this reset value has not been established before the read. Therefore, neither  $P_3$  nor  $P_4$  are B-reactive. In the hardware translation of Esterel,  $P_3$  would be a delay loop s = s which has two stable solutions s = 0 and s = 1, while  $P_4$  generates essentially the feed-back system  $s = \bar{s} \cdot s$  which may produces glitches before it settles at s = 0, if it stabilises at all.

$P_3$  and  $P_4$  were acceptable if the status of s was already decided before the test s?. For instance, in !s;  $P_3$  the second !s in  $P_3$  is ineffective from the point of view of the read access because the status 1 on s is determined by the first !s which occurs sequentially before the read. Thus, executing !s;  $P_3$  is B-admissible.  $P_4$  can be executed admissibly in the form !s;  $P_4$  which then bypasses the reset !s in  $P_4$ . On the other hand, !s;  $P_4$  would not be B-reactive because it generates a reset !s after a set !s. We note that all programs  $P_1-P_4$  are sequentially admissible [37] (called  $\Delta_*$ -admissibility in [4]) because under sequential admissibility glitches can only be generated from concurrent accesses, not sequential ones as in  $P_1$  and  $P_2$ .

*Example* 8 Although each fprog P := x? ! $y : \varepsilon$  and Q := y? ! $x : \varepsilon$  is B-reactive, their concurrent composition fprog  $P \parallel Q$  is not. There is only one initial memory  $\rho_0$  from which

this has any B-admissible instants, viz.  $\rho_0(x) = \rho_0(y) = 0$ . Whenever initially  $\rho_0(x) = 1$  (or  $\rho_0(y) = 1$ ), then the write statement !y in P (or !x in Q) is executed after x (or y) has been read by P. This violates Def. 4(2) because there are no other writes before the read which would make the "late" write ineffective.

Example 9 All the scheduling sequences  $R:(\{T_1\},\rho_0) \rightarrow (\{\},\rho_{21})$  of Ex. 4, following the transitions colored green in Fig. 2 are B-admissible. None of the scheduling sequences going through a red transition, entering region A or B, is B-admissible. The sequences entering region A are violating Def. 4(1) by resetting variable s (dashed red arrows labelled s) after s has been set (solid red arrows labelled s). The sequences entering region s are breaking the constraint Def. 4(2) because variable s is set (dashed red arrow labelled s) after it has been read (solid red arrows labelled s), without any setting of variable s before the read. However, since at least one B-admissible scheduling sequence leads to completion, the program s; s is s in s is s in s in

### 2.3.2 SC-Admissibility and SC-Read-Determinacy

When it comes to the question of determinacy then we want the underlying notion of *X*-admissibility to be as weak as possible. If a program analysis detects determinacy under all *X*-admissible executions, then the implied level of robustness depends on how much non-determinism is still permitted by *X*-admissible executions. For instance, if *X*-admissibility limits execution to a single micro-sequence, *e.g.* through a global linear priority ordering on all statements, then determinacy is trivial. On the other hand, knowing that a program is determinate under all free schedules, is a very strong (and rare) property for a program to have. To get more headroom for our main result we use SC-admissibility. In contrast to B-admissibility this admits writes-after-reads and resets-after-sets, if these are sequential successors in program order or confluent. The following definition is rephrased from [37, 38].

**Definition 5 (SC-Admissibility and Reactiveness)** A micro-sequence  $R: (\Sigma_0, \rho_0) \twoheadrightarrow (\Sigma_k, \rho_k)$  is SC-admissible if for every two processes R(i), R(j) such that  $0 < i < j \le n$  and either

- (i) R(j) performs a reset is or set is on a variable s that was read (tested) by R(i), or

- (ii) R(j) performs a reset ; s on a variable s on which R(i) performed a set !s,

the first R(i) is sequentially before R(j) in program order or both are confluent, *i.e.*, we have  $R(i).id \leq R(j).id$  or  $R(i) \sim_{(\Sigma_i, \rho_i)} R(j)$ .

An fprog *P* is *SC-reactive*, if from every initial configuration  $(\{\langle 0, P, [] \rangle\}, \rho_0)$  there is at least one SC-admissible instant for *P*.

One can show that B-admissibility is more restrictive than SC-admissibility.

**Proposition 1** Every B-admissible micro-sequence is also SC-admissible.

*Proof* Let  $R: (\Sigma_0, \rho_0) \twoheadrightarrow (\Sigma_n, \rho_n)$  be a B-admissible micro-sequence, with processes instances R(i) and R(j) such that  $0 < i < j \le n$ . First note that by condition (1) of B-admissibility Def. 4, the situation (ii) of Def. 5 cannot occur. We only need to care about the situation (i), where R(i) is a read and R(j) a write of the same variable s. But then condition (2) of B-admissibility implies both are confluent, *i.e.*,  $R(i) \sim_{(\Sigma_i, \rho_i)} R(j)$ . This was to be shown.

Example 10 The Ex. 4 is B-reactive and thus also SC-reactive. However, it does not have any SC-admissible scheduling sequences which are not B-admissible at the same time. None of the scheduling sequences entering regions A or B in Fig. 2 are SC-admissible. Let us look at what happens in region A. For instance, take the scheduling

$$R = T_1, T_{21}, T_{31}, T_{41}, T_{22}, T_{32}, T_{42}, T_{521}, T_{20} : (\{T_1\}, \rho_0) \rightarrow (\{\}, \rho_{22})$$

in which  $R(3) = T_{31}$  performs a set !s and later  $R(6) = T_{32}$  performs a reset is. This violation of resets-before-sets is permitted under SC-admissibility only if the actions are sequentially ordered or confluent. The former is not the case,  $T_{31}.id = 0.l.0 \not \leq 0.r.0 = T_{32}.id$ , because both processes are from concurrent threads. The latter is not the case either, because  $T_{31} \not\sim_{(\{T_{20},T_{31},T_{22}\},\rho_0)} T_{32}$ . In fact, there is the (free) schedule  $T_{22}:(\{T_{20},T_{31},T_{22}\},\rho_0) \rightarrow (\{T_{20},T_{31},T_{32}\},\rho_0)$  (underlined in Fig. 2) which reaches the configuration  $(\{T_{20},T_{31},T_{32}\},\rho_0)$  in which both  $T_{31}$  and  $T_{32}$  are active and conflicting (see Def. 3). Executing  $T_{31},T_{32}$  from here leads to  $(\{T_{20},T_{41},T_{42}\},\rho_{12})$  while the swapped ordering  $T_{32},T_{31}$  ends up in  $(\{T_{20},T_{41},T_{42}\},\rho_{11})$  which have different memories.

Similarly, one can show that the two concurrent processes  $T_{42}$  and  $T_{41}$  which read and set variable t are in conflict on every schedule that runs through region B. The critical configuration for region B is  $(\{T_{20}, T_{41}, T_{42}\}, \rho_{11})$  (underlined in Fig. 2) in which processes  $T_{42}$  and  $T_{41}$  are in conflict with each other.

Clearly, by Prop. 1, every B-reactive program is also SC-reactive. An X-reactive program is guaranteed not to deadlock under X-admissible execution. However, it may be non-determinate, *i.e.*, generate different final memory states. In defining determinacy precisely we meet another degree of freedom, depending on whether or not we permit the outcome at the end of an instant to be functionally dependent on the memory configuration at the beginning of the instant. For instance, we might distinguish, as done in Esterel V7, between *temporary* and *registered* variables. The value of a temporary variable is ephemeral and must be recomputed by the program at every instant. The value of a registered variable is provided by the environment in memory at the beginning of each instant. Hence, the final response may depend on the initial value of registered variables but not on the initial value of the temporary variables. This gives rise to the following definition, parametric in *X*-admissibility, where the notations  $\rightarrow_X$  and  $\Longrightarrow_X$  are used to indicate that the corresponding micro-sequence complies with a particular notion X of admissibility. E.g.  $\rightarrow_B$  refers to a B-admissible micro-sequence and  $\Longrightarrow_{SC}$  indicates a SC-admissible instant.

**Definition 6 (X-Determinacy)** For a given set of *temporary* variables  $W \subseteq V$ , an fprog P is *X-determinate for W* ( $X_W$ -determinate) iff the following two conditions hold:

For every fixed initial memory, P computes the same final memory in all X-admissible instants.

Formally, if

$$(\langle \iota, P \rangle, \rho_0) \Longrightarrow_X (\Sigma_0, \gamma_0)$$

and  $(\langle \iota, P \rangle, \rho_0) \Longrightarrow_X (\Sigma_1, \gamma_1)$  then  $\gamma_0 = \gamma_1$ .

2. For every temporary variable in W, P either (i) computes the very same final value in all X-admissible instants, or (ii) it does not modify the initial memory value of this variable in any X-admissible instant. In other words, if P changes the value of a variable  $x \in W$  in any X-admissible instant then this must be the final value for x in all X-admissible instants.

Formally, for all  $x \in W$  and  $\gamma_0$ ,  $\rho_0$ ,  $\Sigma_0$ : if  $(\langle \iota, P \rangle, \rho_0) \Longrightarrow_X (\Sigma_0, \gamma_0)$  and  $\gamma_0(x) \neq \rho_0(x)$ , then for all  $\gamma_1$ ,  $\rho_1$ ,  $\Sigma_1$  such that  $(\langle \iota, P \rangle, \rho_1) \Longrightarrow_X (\Sigma_1, \gamma_1)$ , we have  $\gamma_1(x) = \gamma_0(x)$ .

In this article we will treat two special cases: When W is the empty set,  $W = \emptyset$ , then  $X_W$ -determinacy is simply called X-determinacy. When W = rd(P) is the set of read variables of P, defined by

$$rd(P) := \begin{cases} rd(P_1) \cup rd(P_2) & \text{if } P = P_1 \parallel P_2 \text{ or } P = P_1 ; P_2 \\ \{s\} \cup rd(P_1) \cup rd(P_2) & \text{if } P = s ? P_1 : P_2 \\ \emptyset & \text{otherwise} \end{cases}$$

then  $X_W$ -determinacy is referred to as *X-read-determinacy*. The following proposition is obvious, with Prop. 1:

**Proposition 2** Every X-read-determinate fprog is also X-determinate and every SC-determinate program is B-determinate.

Note that purely *sequential* programs, *i.e.*, those without the concurrency operator  $\parallel$ , are trivially deterministic and hence SC-read-determinate. Sequential programs are also always SC-reactive. They can however fail B-reactiveness, *i.e.*, if their execution is not B-admissible because it generates a causal hazard in the access to a variable (see Ex. 7). This models the stronger interpretation of reactiveness in the more conservative SMoCCs like Esterel and Quartz which we deal with, here. Also, SC-read-determinacy is trivial for pure input variables which are never written by a program because their final value will always be the same as the initial value. Hence, all programs, including those containing the  $\parallel$  operator, with *disjoint* input and output variables, are SC-read-determinate but possibly not B-reactive.

The following Ex. 11 brings home the problems causality poses for compositionality.

Example 11 All  $P_1$ ,  $P_3$ ,  $P_4$  from Ex. 7 are purely sequential programs which are not B-reactive but SC-read-determinate. An fprog which is B-reactive but not SC-determinate is the parallel composition  $P \parallel Q$ , where P := x?  $\varepsilon$ :!y and Q := y?  $\varepsilon$ :!x. The left component P sets y to 1 if x is 0 and the right sub-expression Q sets x to 1 if y is 0. Indeed, if both variables  $x, y \in rd(P \parallel Q)$  are initially  $\rho_0(x) = \rho_0(y) = 0$ , the response of  $P \parallel Q$  is non-determinate (under B-admissible scheduling). If P is first executed to termination and then Q, we get the final memory  $\gamma_0(x) = 0$ ,  $\gamma_0(y) = 1$ ; otherwise, if we first execute Q and then Q, the result will be  $\gamma_0(x) = 1$ ,  $\gamma_0(y) = 0$ . This is an internal non-determinism observable from a single fixed initial memory.  $P \parallel Q$  is B-reactive but not B-determinate and thus neither SC-determinate.

That a program is non-determinate does not mean all its sub-programs must be non-determinate, too. *E.g.*, both fprogs *P* and *Q* in this example are SC-read-determinate. *E.g.*, the only read variable  $x \in rd(P)$  is not touched by *P* and thus left to be controlled by the environment. This satisfies condition (2) of Def. 6. Note that the value of *y* is changed in the SC-admissible execution of *P* starting from  $\rho_0(x) = 0$  and  $\rho_0(y) = 0$  and its final value  $\gamma_0(y) = 1$  is *not* the final value for all SC-admissible instants, *e.g.*, if  $\rho_0(x) = 1$  and  $\rho_0(y) = 0$  then we get  $\gamma_0(y) = 0$ . However, this is not a violation of Def. 6(2) because  $y \notin rd(P)$ .

Finally note that non-determinate programs can become determinate in context. *E.g.*, the SC-admissibility rules make sure that in  $P \| Q \| !x$  the set !x is executed before the test x? in P, which means that P does not write !y which prevents Q from writing !x, thereby avoiding an admissibility hazard with any earlier read of y by Q. Moreover, since the set !x is executed before the read x? by P, the set !x by Q is confluent with the read. As a consequence, for any given initial memory  $\rho_0$ , all SC-admissible executions of  $P \| Q \| !x$  produce the same determinate response  $\gamma_0$  with  $\gamma_0(x) = 1$  and  $\gamma_0(y) = \rho_0(y)$  is the initial value. Thus, the fprog  $P \| Q \| !x$  is SC-read-determinate.

In Sec. 4 below we shall give a sound denotational fixed point analysis to check a program is B-reactive and SC-read-determinate. Our fixed point characterisation defines the class of *input Berry constructive* (IBC) programs which includes more programs than the *strong Berry constructive* (SBC) programs introduced in [4]. The result established in [4], that every SBC program is SC-reactive and SC-determinate, is a corollary of the main Thm. 1 in this article which says that every IBC program is B-reactive and SC-read-determinate.

We first need to introduce the appropriate abstract semantical domains. This is done in the following Sec. 3.

### 3 Abstract Domains and Environments.

The constructiveness analysis on finite pSCL programs (fprogs) takes place in an abstract domain of information values which describe the sequential and concurrent interaction of signals. It accounts for data dependencies and can deal with the difference of a variable retaining its original initial value from the initial memory (pristine), being initialised to 0 and then either remaining 0 (signal absence) or being set to 1 (signal presence). This includes monotonic value changes from 0 to 1 and, essentially, corresponds to Berry's notion of constructiveness in Esterel [12], yet is able to deal with explicit initialisations which requires the ability to cope with prescriptive sequencing. This section introduces this abstract domain and its natural extension to environments, namely discrete structures able to maintain the information of a number of signal variables.

#### 3.1 Value Domain $I(\mathbb{D})$ of Value Status.

Instead of distinguishing just two signal statuses "absent" and "present" as in traditional SMoCC, we consider the sequential behaviour of a variable (during each instant) as taking place in a linearly ordered 4-valued domain  $\mathbb{D} = \{\bot \le 0 \le 1 \le \top\}$ . This requires to consider two additional logical memory values, namely  $\perp$  and  $\top$ . The former indicates that the corresponding variable contains its initial memory value, i.e., a pristine 0 or 1. The latter tells us that the variable value has passed from 1 to 0 at some point, independently of what the final memory result is. The linear ordering  $\leq$  captures a trajectory through a *single* instance of the iur protocol. Observe the difference between the variable values  $\mathbb{B} = \{0,1\}$ , which appear at "run-time" as defined in the operational semantics, and the signal statuses  $\mathbb{D}$ , which are the basis of constructiveness analysis. The latter lifts our description to a higher level in which the semantics of variables is enriched to reflect the fact that they are controlled by an implicit synchronisation protocol. Observe that the ordering  $\leq$  in  $\mathbb D$  is transitive which permits monotonic status changes from  $\perp$  directly to 1, without first passing through 0. This means a program can set a variable (emit a signal in Esterel) which has not been explicitly reset. This matches the iur protocol, from which the notions of B/SC-admissibility are derived, which does not require an update to be preceded by an init operation. However, our fixed point semantics can be easily modified, without changing the domain D, for the stronger requirement if needed.

We now go one step further in the abstraction. In the analysis we operate on *predictions* of variable statuses. Possible statuses of variables are approximated by closed *intervals*  $I(\mathbb{D}) = \{[a,b] \mid a,b \in \mathbb{D}, a \leq b\}$  over  $\mathbb{D}$ . An interval  $[a,b] \in I(\mathbb{D})$  in this 10-valued domain corresponds to the set of statuses  $set([a,b]) = \{x \mid a \leq x \leq b\} \subseteq \mathbb{D}$ . Intervals [a,b] such that