CHRISTIAN-ALBRECHTS-UNIVERSITÄT ZU KIEL

Diploma Thesis

## Esterel Compiler for a Synchronous Reactive Processor

Marian Boldt

## 2007 - 12 - 18

Department of Computer Science Real-Time and Embedded Systems Group

Advised by: Prof. Dr. Reinhard von Hanxleden Dipl.-Inf. Claus Traulsen

## Eidesstattliche Erklärung

Hiermit erkläre ich an Eides statt, dass ich die vorliegende Arbeit selbstständig verfasst und keine anderen als die angegebenen Hilfsmittel verwendet habe.

Kiel,

#### Abstract

The synchronous language Esterel is well-suited for programming control-dominated reactive systems. It provides non-traditional control structures, in particular concurrency and various forms of preemption, which allow to concisely express reactive behavior. As these control structures cannot be mapped easily onto traditional, sequential processors, an alternative approach that has emerged recently makes use of special-purpose reactive processors.

The *Kiel Esterel Processor* (KEP) is a synchronous reactive processor. It supports exception handling and provides context-dependent preemption handling instructions.

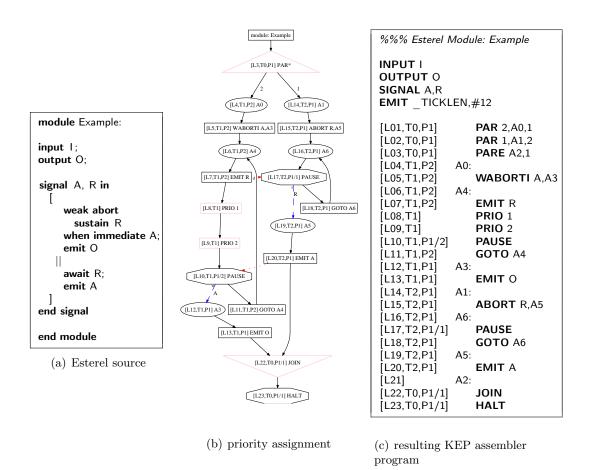

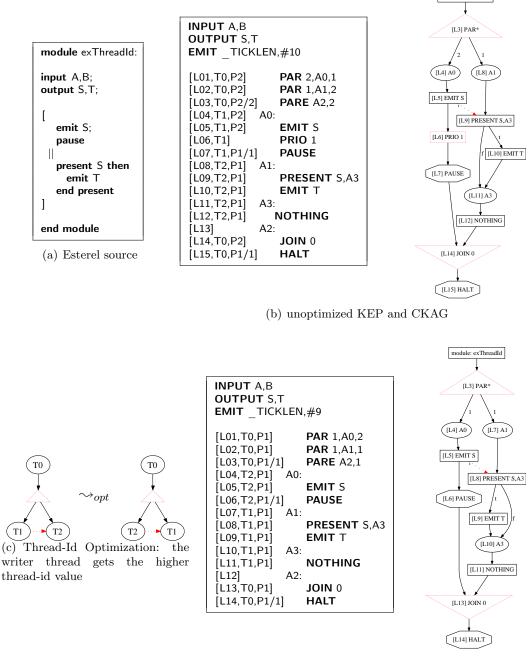

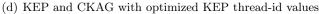

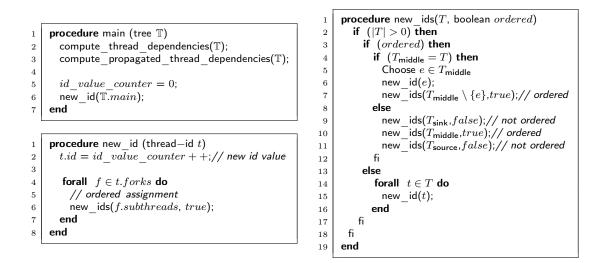

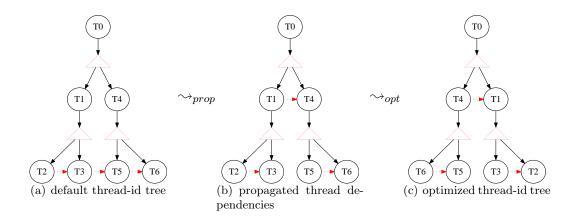

This thesis presents a compiler from *Esterel to KEP assembler* (strl2kasm). The translation of most Esterel statements into KEP assembler is straightforward, especially preemption constructs can be mapped directly. However, it is not trivial to implement the concurrency of Esterel. Concurrency is mapped to multiple threads, yet the compiler must ensure that all data and control dependencies are fulfilled. A priority assignment approach is presented that makes use of an intermediate graph structure, namely the *Concurrent KEP Assembler Graph* (CKAG), that is used to represent the control flow behavior of the KEP assembler program. It is also used to compute and store the concurrent program dependencies that are needed for the priority assignment. The complexity of the assignment algorithm for most programs is linear in the program size. Unlike earlier Esterel compilation schemes, this approach avoids unnecessary context switches by considering actual execution state at run time for each thread. Furthermore, it avoids code replication present in other approaches by implementing consequently the *Write Things Once* (WTO) principle.

## Contents

| 1 | Introduction                                                                                                                                                                                                                                                                                                                     | 1                                                                                  |

|---|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------|

| 2 | Basics and Related Work2.1The Esterel Language2.2The Kiel Esterel Processor (KEP)                                                                                                                                                                                                                                                | <b>5</b><br>6<br>11                                                                |

| 3 | Preprocessing: Esterel Dismantling         3.1       Module/Run Dismantling         3.2       Dismantling of Temporal and Finite Loops         3.3       Priority Dismantling         3.4       Simplification of Complex Signal Expressions         3.4.1       Case Expressions         3.4.2       Boolean Signal Expressions | <ol> <li>15</li> <li>17</li> <li>17</li> <li>21</li> <li>25</li> <li>26</li> </ol> |

| 4 | The Concurrent KEP Assembler Graph (CKAG)4.1Nodes and Edges4.2KEP Thread-Id Tree4.3Symbol Scopes                                                                                                                                                                                                                                 | 27<br>28<br>33<br>38                                                               |

| 5 | Constructing the CKAG         5.1       Compiling Complex Statements                                                                                                                                                                                                                                                             | <b>41</b><br>44<br>47<br>48<br>51                                                  |

| 6 | Priority Assignment6.1Signal Dependencies6.2Priority Constraints6.3Assignment Algorithm6.4Realizing the Priority Assignment                                                                                                                                                                                                      | <b>53</b><br>55<br>58<br>62<br>63                                                  |

| 7 | Compiler Optimizations7.1Dead Code Removal7.2KEP Collapsing7.3Priority Assignment Modification7.4Minimizing Dependency Count7.5Thread-Id Value Assignment                                                                                                                                                                        | <b>65</b><br>66<br>69<br>69<br>70                                                  |

### Contents

|    | 7.5.1        | Thread-Id Value Assignment Algorithm    | 75  |

|----|--------------|-----------------------------------------|-----|

|    | 7.5.2        | Weighted Propagated Thread Dependencies | 78  |

|    | 7.5.3        | Thread-Id Reuse                         | 80  |

| 8  | Experiment   | al Results                              | 83  |

| 9  | Implementa   | ation                                   | 87  |

|    | 9.1 Compi    | ler Modules                             | 87  |

|    | 9.2 Data S   | Structures and their Visitor Classes    | 90  |

| 10 | Conclusion   | s and Further Work                      | 95  |

| Bi | bliography   |                                         | 99  |

| Α  | A Examples 1 |                                         | 103 |

|    |              |                                         |     |

# List of Figures

| . 7  |

|------|

|      |

| . 7  |

| . 9  |

| . 10 |

| . 13 |

| . 16 |

| . 18 |

| . 19 |

| . 22 |

| . 23 |

| . 24 |

| 28   |

| . 36 |

| . 39 |

| . 43 |

| . 46 |

| . 48 |

| . 49 |

| . 55 |

| . 60 |

| . 60 |

| . 61 |

| . 67 |

| . 68 |

| . 71 |

| . 73 |

| . 73 |

| . 75 |

| . 79 |

| . 83 |

|      |

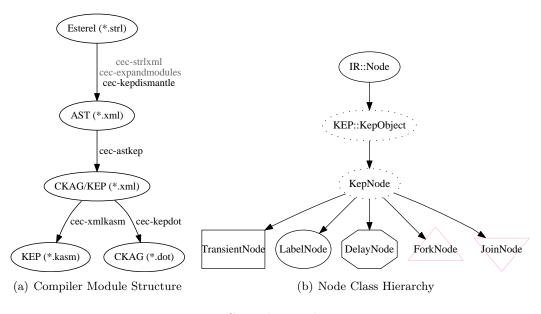

| 9.1 | Compiler Overview                 | 88  |

|-----|-----------------------------------|-----|

| 9.2 | Compiler Structure                | 88  |

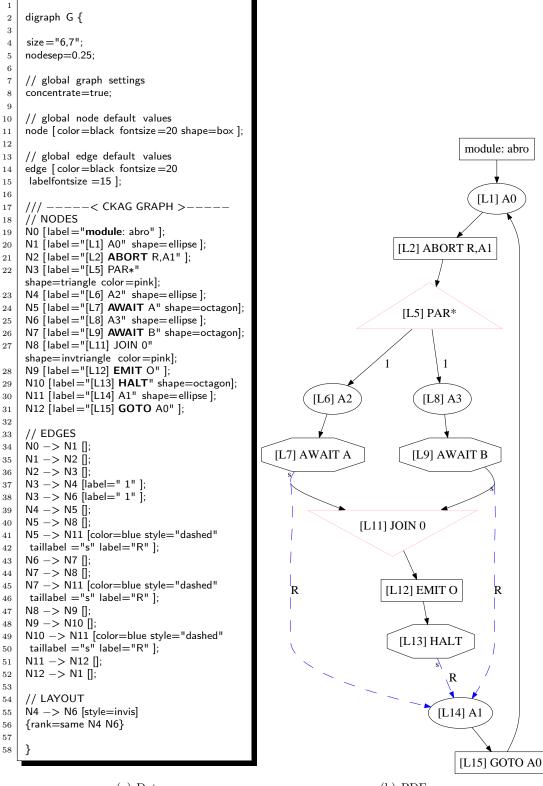

| 9.3 | CKAG Dot Representation           | 91  |

|     |                                   |     |

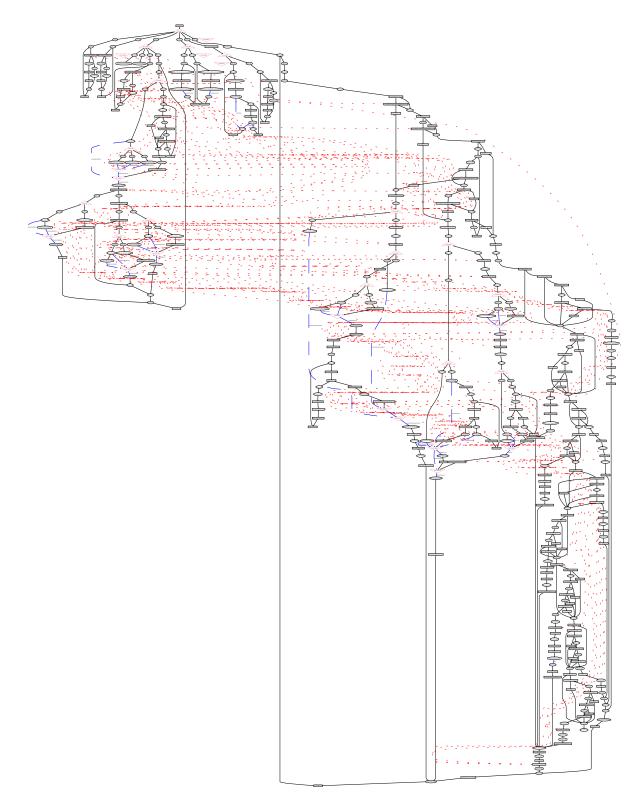

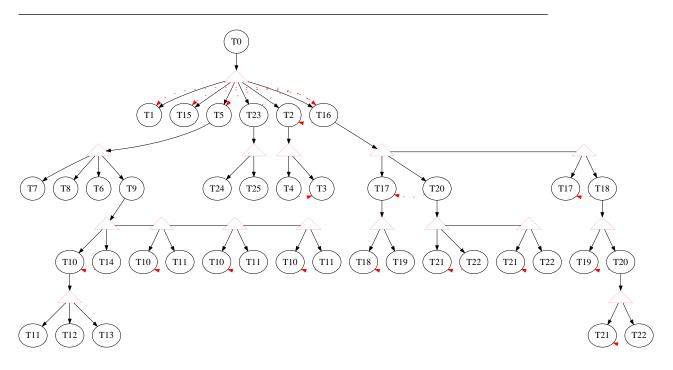

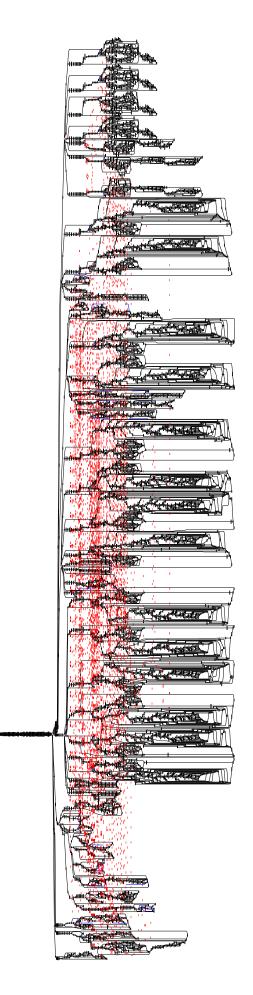

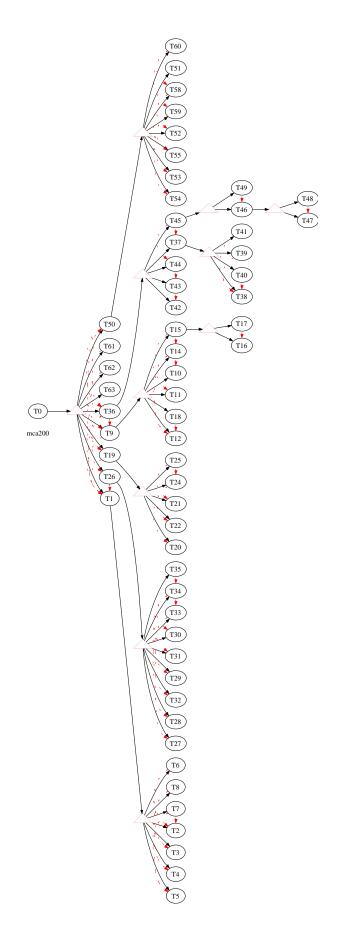

| A.1 | CKAG of the Tcint                 | 104 |

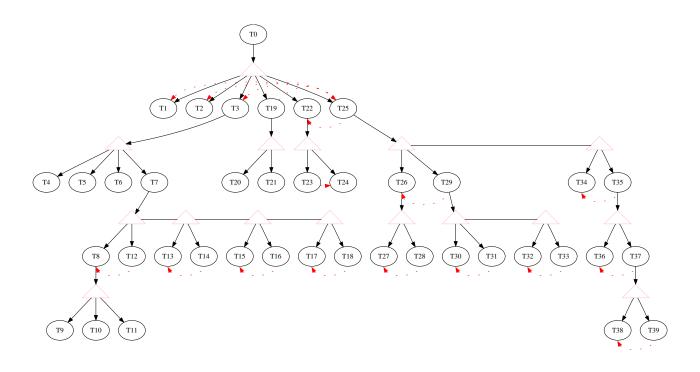

| A.2 | Thread-Id Tree of Tcint           | 105 |

| A.3 | Optimized Thread-Id Tree of Tcint | 105 |

| A.4 | CKAG of the Mca200                | 106 |

| A.5 | Optimized Thread-Id Tree of Tcint | 107 |

## 1 Introduction

Embedded systems get more and more popular and today appear in most electrical devices. Thus, it has become an important task to create reliable software for these systems. Since their control flow is often non-standard, languages and processors were designed to implement their behavior explicitly. The properties of such systems and their differences to common applications are now discussed. Therefore, systems in general are considered, which can be divided into three main categories [5]:

- Transformational Systems: Computation of an output result from a given input argument, e.g., numerical computations or interpreter/compiler. These systems are also denoted as *standard control flow* applications.

- Interactive Systems: The environmental interaction is triggered by the system itself, *i. e.*, the response time affects not the result, *e. g.*, databases and operating systems.

- *Reactive Systems*: These react continuously to inputs from the environment by generating corresponding outputs timely. The result depends on the response time.

Most systems and their programs consist of sub-systems and program parts that belong to different categories. Many embedded systems belong to the class of *reactive* systems. A further definition for reactive systems is given by Edwards *et al.* [18]:

- Criticality: They are highly critical, e.g., time-critical, safety-critical.

- *Parallelism*: Distributed components operate often in parallel to achieve the desired behavior.

- Determinism: This is obviously desired for critical systems.

To ensure short response times in time-critical systems, it is recommended to support *preemptive* control flow.

The implementation of reactive systems with all the above requirements is no easy task, because the programming paradigms of standard programming languages, like C/C++, are designed to address standard control flow, applicable to implement transformational systems. In particular, a timing model is not a standard language construct and therefore, it has to be implemented by hand. This is a significant obstacle for the implementation of time-critical systems. This leads to a higher complexity on the implementation side, which makes it more difficult. Concurrency

#### 1 Introduction

is as well hard to express, it is often implemented in a non-deterministic or nonefficient way.

To address these difficulties, the reactive and synchronous languages, like Signal [25], Lustre [26] and Esterel [9, 7], have been developed. They are designed to express reactive control directly in its syntax. These provide a discrete and abstract time model that orders the execution into a chain of ticks. The execution at these ticks is assumed to be instantaneous [10]. Here we consider the synchronous language Esterel, that is both parallel and deterministic. It has a formal mathematical semantics that imposes a strong deterministic program behavior and allows the programmers to develop critical software faster and better.

There exist different strategies to implement an Esterel program. The hardware approach generates combinational circuits from Esterel, e.g., expressed in the hardware description languages VHDL or Verilog [4]. The implementation results in an efficient implementation, but is not flexible because a change in the Esterel source requires a complete re-synthesis. The software approach translates Esterel to a nonsynchronous language like C to be executed on standard COTS hardware [10, 16]. This solution is flexible, but the generated code might be slow because standard hardware is not designed to match reactive control flow. Both principles can be combined to a hybrid approach—the hardware-software co-design [3].

Another alternative for synthesizing Esterel has emerged, the reactive processing approach. The Esterel program is running on a processor, here the *Kiel Esterel Processor* (KEP) [27], that has been developed specifically for reactive systems. The instruction set of these reactive processors closely resembles the constructs found in Esterel, such as waiting for occurrence of a signal or abortion. Reactive processors provide direct hardware support for reactive control flow, which keeps executables fast and compact and results in lower power consumption compared to traditional architectures.

Apart from efficiency and determinism concerns, another advantage of reactive processors is that due to their comparatively simple structure, *i. e.*, no caches and no pipe lining, and their direct implementation of reactive control flow constructs, it becomes feasible to precisely characterize their timing behavior [39]. In conjunction with the synchronous model of computation, which discretizes time into logical ticks, it is thus possible to derive exact, tight bounds on its Worst Case Reaction Time (WCRT) [11], which tells how much time it takes the system to react to the environment. This is important for time-critical reactive systems. The KEP is equipped with a Tick Manager that can provide a constant logical tick rate and also detects internal timing overruns. This can serve to detect hardware failures, reduce jitter, and provides another safeguard—in addition to static analysis—that real-time deadlines are met.

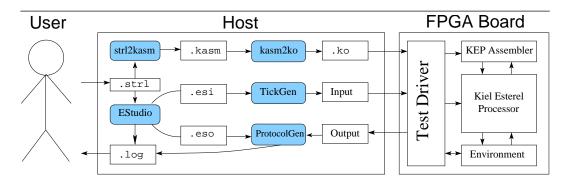

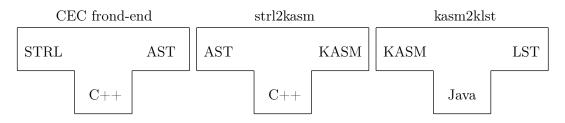

This thesis presents the *Esterel to KEP assembler* (strl2kasm) compiler. The strl2kasm bridges the gap between Esterel and the KEP assembler. This makes it possible to write programs in Esterel and execute them on the KEP. It is also used for a variant of the HW/SW co-design approach that uses the KEP [22, 21], where the software part is KEP assembler generated by the strl2kasm. The compiler is embedded within the *Columbia Esterel Compiler* (CEC) compiler [15] and uses the CEC

as front-end to parse Esterel. This is easily possible due to the modular architecture of the CEC. The CEC uses an intermediate data structure, the *GRaph Code* (GRC), to split the Esterel statements into their basic parts using common language constructs. The strl2kasm uses its own representation, the *Concurrent KEP Assembler Graph* (CKAG) to express the control flow of KEP assembler instructions. This different internal intermediate data structures is needed due to the different compilation targets. The CEC generates common soft- and hardware code, whereas the strl2kasm match the reactive parts of Esterel directly onto the KEP assembler. This is possible because the KEP *Instruction Set Architecture* (ISA) closely resembles the Esterel language, *i. e.*, many Esterel statements can be translated straightforward to the KEP ISA.

A compilation approach for sequential Esterel programs and its WCRT were presented [29] that uses the *KEP Assembler Graph* (KAG), a forerunner of the CKAG, that supported only sequential Esterel programs. The strl2kasm now supports concurrent Esterel programs by using the multi-threaded features of the KEP, making further compilation steps necessary, in particular the *priority assignment*.

The KEP supports concurrency by implementing a priority based multi-threading concept. The threads are created by so called PAR instructions that define which instructions belong to the thread in conjunction with the initial thread priority. The PAR instructions match the Esterel concurrency operator, where the concurrent Esterel bodies correspond to the instructions of a thread. Due to the semantics of Esterel, the thread instructions are not independent from each other and have to be executed in some order. *E.g.*, an EMIT S instruction is executed before an according PRESENT S. The execution order is influenced by the threads priorities. The instructions of the thread with the highest priority are executed. Therefore the KEP ISA provides the PRIO instructions. These have an integer argument, a priority, to that its thread is changed to within the KEP scheduling.

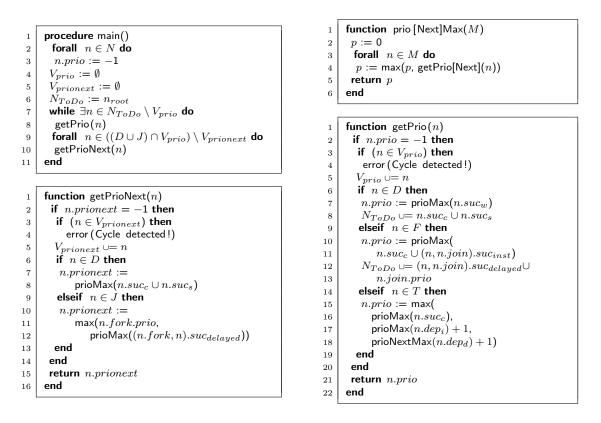

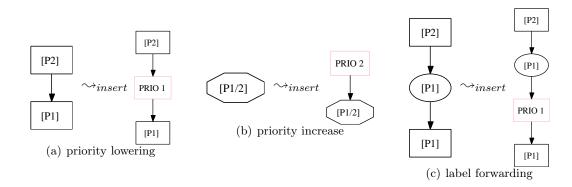

The main purpose for the strl2kasm is to set these priorities in a way that the instructions are always executed in the right order. Note that the ordering has to be ensured for all possible signal statuses from the input side. Therefore the strl2kasm compiler can set the initial priorities in the PAR instructions as well as insert PRIO instructions. This goal is achieved by the earlier mentioned priority assignment. Its basic idea is to assign each instruction a priority by which the instruction has to be executed, thereby a higher priority is assigned to an EMIT S than to an according PRESENT S. This is called a dependency constraint, any such must be fulfilled. Other constraints belong to the normal control flow, which induces that thread priorities can never grow instantaneously, because an instantaneous priority increase does not guarantee that a thread with a higher priority has not already been executed. The fulfillment of all constraints is the priority assignment. The priority assignment computation is based on a Depth First Search (DFS) algorithm that traverses only the instantaneously reachable successors of an instruction. After the assignment, the threads are initialized accordingly, and wherever the assigned priority between instructions differ, a PRIO instruction is inserted.

#### 1 Introduction

The strl2kasm supports several optimization techniques. Some are common with other compilers like *dead code elimination* and *constant propagation*. Other target the KEP scheduling principle to solve dependency constraints with appropriate thread identifiers when possible.

The strl2kasm generates efficient assembler code by making use of the KEP scheduling principles and the optimizations resulting from these.

In addition to this introduction chapter, this thesis is organized as follows:

- Chapter 2 describes the synchronous language Esterel and its compilation, as well as the KEP and its instruction set architecture.

- In Chapter 3 the Esterel dismantling is presented. This is a pre-processing step that reduces the amount of Esterel syntax without weakening the expressive-ness of Esterel.

- Chapter 4 introduces the CKAG, an intermediate graph structure that is needed during the compilation.

- The creation of the CKAG is described in Chapter 5. This is the first main compilation step.

- The Esterel concurrency is implemented by the *priority assignment* explained in Chapter 6. If necessary, PRIO instructions are inserted.

- Chapter 7 presents several compiler optimizations that are implemented in the strl2kasm.

- The strl2kasm is discussed and validated in Chapter 8 on the basis of the estbench, a set of standard Esterel programs.

- The strl2kasm implementation and usage is described in Chapter 9.

- The conclusions of this thesis are presented in Chapter 10 along with possible further work.

- The Appendix shows some bigger CKAG and thread-id tree examples.

Several aspects of the work documented in this thesis were already presented elsewhere. A sequential version of the KEP and its WCRT, based on the KAG, were presented at *CASES'05* [29]. The priority assignment used by the strl2kasm was presented at *ASPLOS'06* [28]. The strl2kasm was also used for an approach of HW/SW co-design using the KEP [22]. The computation of the WCRT has also been implemented in the strl2kasm as a student research project [11], and was presented at SLA++P'07 [12].

The specifies of each compiler depend heavily on its source and target language. For the *Esterel to KEP assembler* (strl2kasm) compiler presented here, this is the synchronous language Esterel and the instruction set of the KEP. Before discussing the design issues that depend on these languages, first, some general compiler implementation topics are treated that affect several performance criteria, see Aho *et al.* [1] for a detailed overview on compilers. Many of these regard both the compiler implementation and the properties of the resulting target code.

- Compiler Speed: On the one side, the speed of the compilation process is important to generate code in an acceptable amount of time. Therefore the used algorithms are of low complexity or at least have a linear runtime in practice. On the other side, the speed of the target code is even more relevant. Since many Esterel statements are compiled straightforward and efficiently to the KEP assembler, this goal is achieved, see Chapter 8.

- Code Quality: The implementation is split into several modules to handle the complexity of the problem. The implementation on the low level is made as robust and readable as possible. Regarding the target code, several optimization techniques are applied to generate efficient code (see Chapter 7).

- Error Diagnostics: The compiler itself is designed to document the whole compilation process. This makes it easier to find bugs. The quality of the KEP assembler programs is verified by their execution of testcase scenarios that are generated from the according Esterel source (see Chapter 8). The output traces are compared to the output of an Esterel reference implementation, in this case EsterelStudio. A different output indicates an error.

- Portability: The portability criterion can be divided into retargetability and rehostability. The retargetability is hard to achieve, because the KEP instruction set is focused on Esterel. However, the strl2kasm is constructed of several modules, see Chapter 9, which allows a high flexibility. The strl2kasm is written in C++, which is a standard and well established programming language with existing compilers on several architectures. It uses only the standard library and depends on software that is already available for several operating systems. Therefore the rehostability should easily possible. Currently it is running under the Linux operating system as well as Windows using Cygwin.

- Maintainability: The implementation language C++ is an object-oriented programming language that allows easy inheritance and data hiding through class

|                                                        | 1                                                                                                                                                                                                                                             |

|--------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Esterel Source                                         | Description                                                                                                                                                                                                                                   |

| ;                                                      | Sequence operator                                                                                                                                                                                                                             |

|                                                        | Parallel operator                                                                                                                                                                                                                             |

| pause                                                  | The control pauses and restarts<br>in the next instant.                                                                                                                                                                                       |

| emit S                                                 | Signal S is emitted and becomes present in the current instant.                                                                                                                                                                               |

| present <i>S</i> then<br>p<br>else<br>q<br>end present | If signal S is present the then<br>body p is executed otherwise the<br>else body q.                                                                                                                                                           |

| loop<br>p<br>end loop                                  | The body p is infinitely often re-<br>peated if not stopped from an<br>outer preemption. Therefore the<br>loop body p has to be non-<br>instantaneous.                                                                                        |

| suspend<br>p<br>when S                                 | The body p is suspended when signal S occurs.                                                                                                                                                                                                 |

| nothing                                                | Empty statement                                                                                                                                                                                                                               |

| signal S in<br>p<br>end signal                         | A new local signal S is defined<br>with program body p as scope.<br>All global signals of name S are<br>overridden in p. Note that a<br>global S might be present, but<br>the new S will always be absent<br>until an emit S occurs inside p. |

| trap T in<br><br>exit T<br><br>end trap                | The exit T statement terminates, if called, the entire trap body.                                                                                                                                                                             |

Figure 2.1: Esterel Kernel Statements

data structures. Since the strl2kasm implementation is built of classes with well defined interfaces, these can be replaced by sub-classes for further properties as well as the internal rewrite of class methods.

Next the Esterel language and semantics as well as its compilation are described in detail.

## 2.1 The Esterel Language

The Esterel programming language [9] belongs to the synchronous languages. Its execution is divided into logical *instants*, also called *ticks*. The communication between the environment, different programs and within or across threads occurs via *signals*. Each Esterel program provides a signal interface of *input* and *output* signals; local

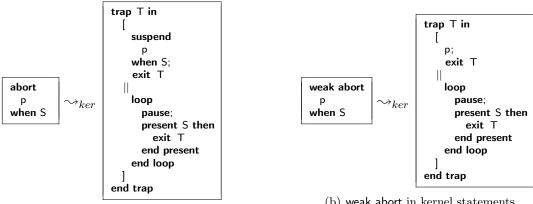

(a) abort in kernel statements

(b) weak abort in kernel statements

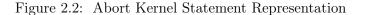

Figure 2.3: The Esterel ABRO example.

signals are declared by the *signal* statement. At each tick, a signal status is either present (emitted) or absent (not emitted); the status may not change within a tick.

Esterel statements are either *instantaneous* (also called *transient*), in which case they do not consume logical time, which is referred to as *synchrony hypothesis* [10]); or they are *delayed*, in which case they finish the execution for the current tick. Most statements are transient including, for example, emit, loop, present, or the preemption operators. Delayed statements include pause, (non-immediate) await, and every.

The Esterel parallelism is expressed by the concurrency operator, denoted by ||, that groups statements in concurrently executed threads. The parallel terminates when all its branches have terminated. Wether concurrent threads are transient or delayed depends on the thread bodies and the signal environment during execution.

Esterel offers two types of abort preemption constructs. An abortion kills its body when an abortion trigger occurs. The strong abortion statement kills its body immediately (at the beginning of a tick), while weak abortion lets its body receive control for a last time (abortion at the end of the tick). A suspension freezes the state of a body in each instant when the trigger event occurs.

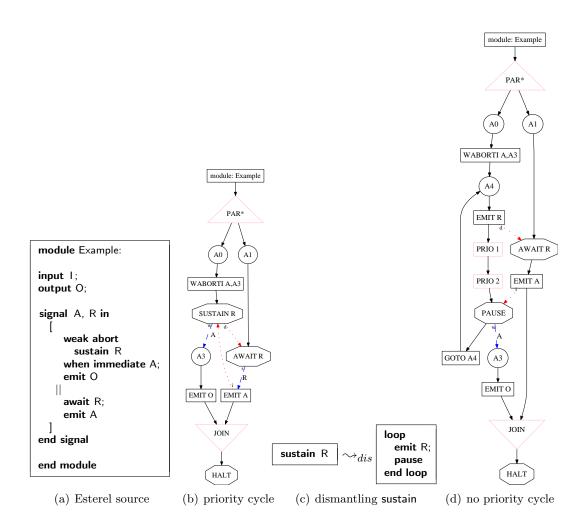

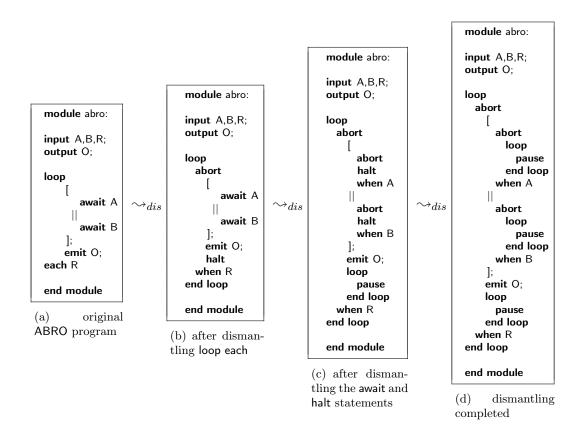

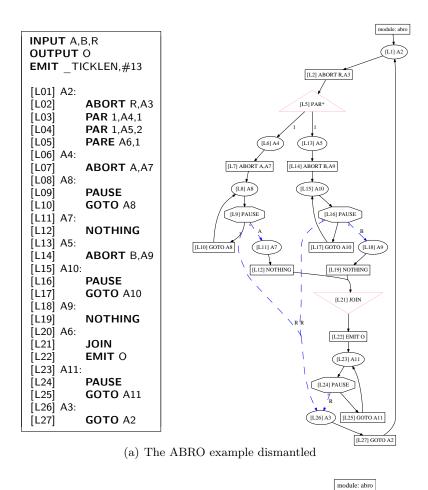

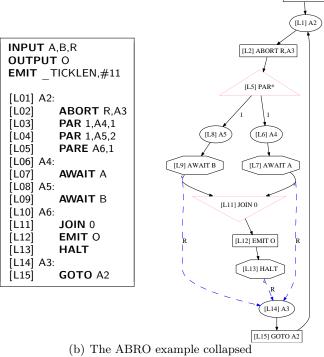

Consider the standard ABRO example in Figure 2.3 (a). It is an example that is minimal by using all the Esterel's reactive features. The program body consists of a loop that encloses an abort over a parallel. The await statements are waiting concurrently for signals A and B. Each await terminates when the specific signal occur. If both signals A and B have occurred then the parallel terminates and the output signal O is emitted. The signal R resets the loop body and this reactive computation starts again.

Esterel also offers an exception handling mechanism via the trap/exit statements. An exception is *declared* with a trap scope, and is *thrown* with an exit statement. An exit T statement terminates immediately the corresponding trap T statement and weakly aborts the trap body. However, there are complications when traps are nested or when the trap scope includes concurrency. The following rules apply: if one thread raises an exception and the corresponding trap scope includes multiple threads, then all the threads are weakly aborted; if concurrent threads execute multiple exit statements in the same tick, the outermost trap takes priority. The execution of multiple exit statements belonging to the same trap is equivalent to a single exit statement.

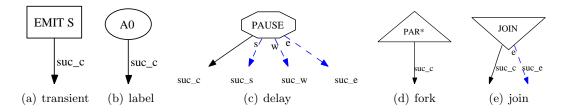

All Esterel statements can be translated into a small set of kernel statements. In Figure 2.1, an overview of the Esterel kernel statements is given. These statements have the full semantically expressiveness as Esterel and are minimal in this behavior. This Esterel sub-set is used to define the semantics of Esterel [6].

The abort statements are not part of the kernel statements. They can be translated to kernel statements as described in Figure 2.2. Their behavior is matched by a trap containing a present test that is executed each instant concurrently to the abort body. If the signal is present then the trap is terminated by an exit; the strong abort is additionally enclosed by a suspend statement to match the immediate stop. However, the number of kernel statements that is needed to represent the abort statements is huge compared to one (abort). Therefore, to be efficient, the KEP ISA supports them directly by the ABORT instruction.

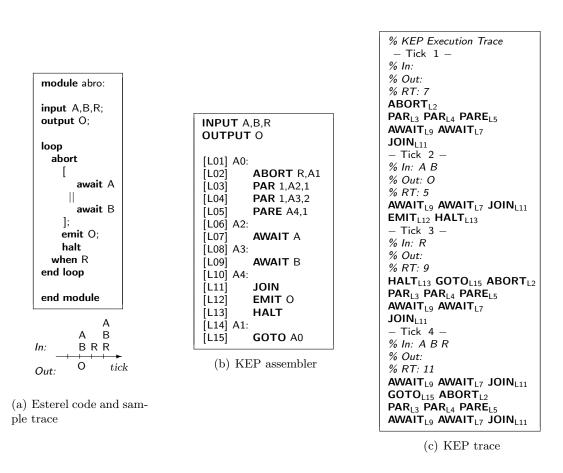

Figure 2.4: The Kiel Esterel Processor

The KEP supports a superset of the kernel statements directly. However, there remain other Esterel statements that are not handled directly, but have to be transformed into equivalent statements that are supported. This is made as a pre-processing step denoted as *esterel dismantling* (see Chapter 3).

Due to the mixture of preemption and concurrency, it is not trivial to determine whether an Esterel program is correct. The usual criteria its *constructive*ness [5]. It can be determined by a translation to combinational circuits to perform *ternary logic* [31] analysis on it. Here, we assume that the source programs are acyclic and this implies that they are constructive. However, the strl2kasm does not make a constructiveness check.

There exist multiple compilers to translate Esterel to VHDL and C. The compilation to standard architectures relies either on the simulation of netlists, or a static schedule is determined and the code is sequentialized accordingly. The Estudio implementation as well as the *Columbia Esterel Compiler* (CEC) [15] are such Esterel compilers. They use an intermediate graph structure, the GRC [34], that splits the Esterel statements into its basic parts. Due to the architecture of the KEP, this is not done in the strl2kasm compilation. This is also the reason why we use a different intermediate format, namely the CKAG that can represent the control flow of all KEP instructions.

Next, the KEP and its Instruction Set Architecture (ISA) is introduced.

| Esterel Source                                                                      | KEP Assembler                                                                                                                                     | Notes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|-------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| emit S [(val)]                                                                      | EMIT S [, {#data reg}]                                                                                                                            | Emit (valued) signal <i>S</i> .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| present <i>S</i> then<br>p<br>else<br>q<br>end present                              | PRESENT <i>S</i> , elseAddr<br>P<br>GOTO endAddr<br>elseAddr:<br>Q<br>endAddr:                                                                    | Jump to <i>elseAddr</i> if <i>S</i> is absent.<br>No GOTO instruction is inserted<br>when the <i>else</i> body is empty.                                                                                                                                                                                                                                                                                                                                                                                                   |

| [weak] abort<br>p<br>when [immediate, n] S<br>suspend<br><br>when [immediate, n] S  | [LOAD _COUNT,n]<br>[W]ABORT[I] <i>S</i> , endAddr<br>P<br>endAddr:<br>[LOAD _COUNT,n]<br>SUSPEND[I] <i>S</i> , endAddr<br><br>endAddr:            | To delay a preemption for $n$ ticks is done by setting the built-in variable _COUNT.                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| trap T in<br><br>exit T<br><br>end trap                                             | startAddr:<br><br>EXIT exitAddr startAddr<br><br>exitAddr:                                                                                        | Exit from a trap,<br>startAddr/exitAddr specifies<br>trap scope. Unlike GOTO,<br>check for concurrent EXITs and<br>terminate enclosing   .                                                                                                                                                                                                                                                                                                                                                                                 |

| pause<br>await [immediate, n] S                                                     | PAUSE<br>[LOAD _COUNT, n]<br>AWAIT [I] S                                                                                                          | Await for a signal. AWAIT<br>TICK is equivalent to PAUSE.                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| sustain S [(val)]                                                                   | SUSTAIN S [, (#val reg)]                                                                                                                          | Sustain (valued) signal $S$ .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| halt                                                                                | HALT                                                                                                                                              | Halt the program.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| nothing                                                                             | NOTHING                                                                                                                                           | No operation. Sometimes<br>needed to distinguish address<br>labels.                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| loop<br><br>end loop                                                                | addr:<br><br>GOTO addr                                                                                                                            | Jump to <i>addr</i> .<br>The loop body has to be non-<br>instantaneous.                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| $\begin{bmatrix} & & \\ & p_1 & \\ & \vdots & \\ & & \\ & & p_n & \\ \end{bmatrix}$ | PAR $prio_1$ , $startAddr_1$ , $id_1$<br><br>PAR $prio_n$ , $startAddr_n$ , $id_n$<br>PARE $endAddr$<br>$startAddr_1$ :<br>P_1<br>$startAddr_2$ : | For each thread, one PAR is<br>needed to define the start ad-<br>dress, thread id and initial pri-<br>ority. The end of a thread is de-<br>fined by the start address of the<br>next thread, except for the last<br>thread, whose end is defined via<br>PARE.<br>Behind the <i>endAddr</i> label, the<br>corresponding <i>join node</i> occurs,<br>which is executed at the end of<br>each instant the parallel is ac-<br>tive. A JOIN instruction is ex-<br>ecuted a second time when it is<br>part of a nested parallel. |

|                                                                                     | PRIO prio                                                                                                                                         | The current thread priority is set<br>to <i>prio</i> . This instruction has no<br>direct Esterel counterpart.                                                                                                                                                                                                                                                                                                                                                                                                              |

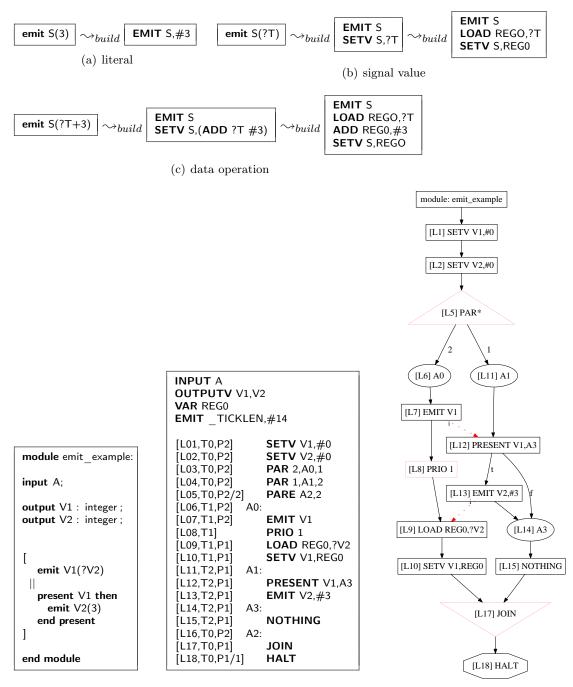

Figure 2.5: Overview of the Esterel syntax and how these Esterel statements are compiled to the KEP instruction set.

## 2.2 The Kiel Esterel Processor (KEP)

The *Kiel Esterel Processor* (KEP) [38] is a reactive processor. It was designed by Xin Li [27], therefore we follow his description:

Neither traditional processors nor classical programming languages have structures or statements/instructions to handle corresponding Esterel statements efficiently. Hence, the implementation of the Esterel semantics on commercial off-theshelf (COTS) processors is problematic since it must be simulated. Therefore, an Esterel-based design proves its efficiency on model description and validation, but can hardly enhance the implementation performance or reduce resource usage.

The KEP is designed to handle Esterel statements directly and efficiently, *i.e.*, it is an *Application Specific Instruction-set Processor* (ASIP) that targets Esterel programs. Notable features of the KEP include the following:

- The KEP is the first reactive processor which employs a multi-threaded architecture for directly handling concurrency. This strategy uses resources efficiently and easily scales up to very high degrees of concurrency.

- The KEP contains a full-custom *reactive core*, whose instruction set and data path have been tailored exclusively for the processing of Esterel code. Hence, all types of Esterel preemption, delays, and exceptions, can be handled by KEP very efficiently.

- The KEP also includes an interface block for handling Esterel input, output and local types of pure and valued signals. Furthermore, testing the presence and values of signals across logical instants (corresponding to Esterel's pre operator) are also directly supported.

- Throughout the development of the KEP, scalability has been considered, hence the allowed number of signals, the maximum thread number, the nesting depth of preemption primitives, and other design parameters are fully configurable.

- Unlike other reactive processing approaches, the KEP ISA is *complete* in that it allows a direct mapping of all Esterel statements onto KEP assembler. All the Esterel kernel statements, including delay, preemption, concurrency and exception handling, are implemented directly and semantically accurately by the KEP, and they can be freely combined and nested as defined by the Esterel semantics. However, it can also make unrefined processing approaches fairly costly. The KEP ISA therefore not only supports common Esterel statements directly, but also takes into consideration the statement context. Providing such a *refined* ISA further minimizes hardware usage while preserving the generality of the language.

Advantages of the KEP compared with traditional processors include:

- **Performance** As the instruction set and data path have been developed specifically for Esterel execution, the Esterel module can be executed fairly fast on KEP. This benefits two key aspects of system performance, *i. e.*, the Worst Case Reaction Time (WCRT) and Average Case Reaction Time (ACRT).

- **Memory** Because most typical Esterel statements can be expressed directly with just a single KEP instruction, an Esterel program executed on the KEP has very low instruction and data memory usage.

- **Power Usage** For controller programming, the main goal of Esterel, the control signals tend to be more often absent than present [7]. Due to the architecture of the KEP, very few instruction cycles are needed for executing a *blank event*, which corresponds to the condition of all signals being absent.

- **Logic Area** The KEP offers a novel light-weight thread model, *i. e.*, the multi-threaded architecture, to implement Esterel concurrency efficiently. This characteristic significantly reduces its logic resource usage for implementing a practical (industry scale) Esterel module.

- **Predictability** The KEP is not designed to optimize (average) performance for general purpose computations, and hence does not have a hierarchy of caches, pipelines, branch predictors, etc. This leads to a simpler design and execution behavior and further implies that control-flow is preserved while compiling Esterel into machine code, and that the execution platform has a very predictable timing behavior.

In summary, the KEP is an efficient reactive processor for handing practical Esterel modules, and appears to be very competitive with other implementations.

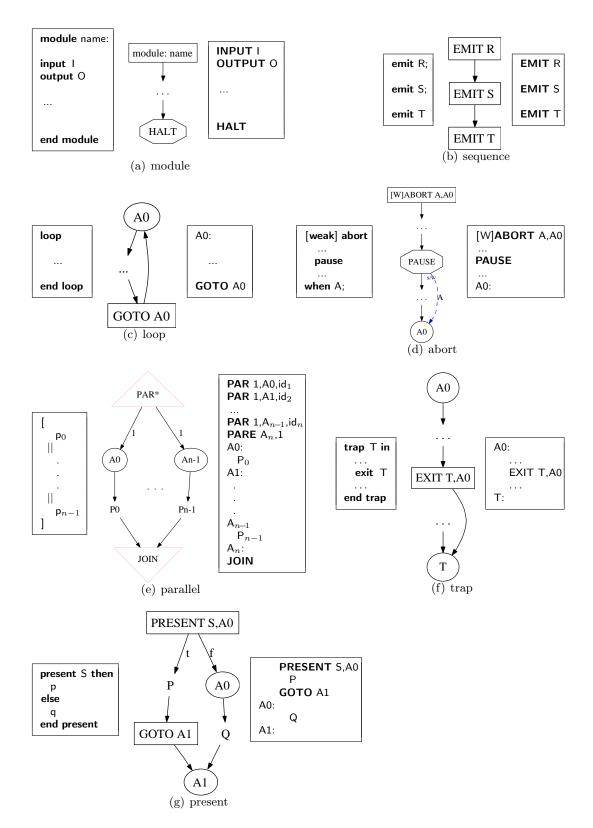

Figures 2.5 and 2.6 give an overview over the KEP ISA. The KEP ISA resembles the Esterel syntax, therefore many Esterel statements are transformed straightforward to their KEP counterparts. Nevertheless, not all Esterel statements are directly supported within the KEP syntax. Therefore, the next chapter describes how these are handled.

| Esterel Source                                                          | KEP Assembler                                                                    | Notes                                                                                                                                                                                                                                     |

|-------------------------------------------------------------------------|----------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| input / [: type]<br>output O [: type]                                   | INPUT[V] <i>I</i><br>OUTPUT[V] <i>O</i>                                          | $type \in \{integer, boolean\}$<br>I/O-statements are part of the<br>interface: no instruction cycles<br>are needed.                                                                                                                      |

| var x : type in                                                         | VAR X                                                                            | $type \in \{integer, boolean\}$<br>The VAR instructions are also<br>part of the interface, even if the<br>Esterel var can occur anywhere.<br>Temporary registers needed for<br>computations are also declared<br>by VAR.                  |

| signal S in end                                                         | SIGNAL S                                                                         | Initialize a local signal $S$ .                                                                                                                                                                                                           |

| sigdecl S := val : type                                                 | SETV <i>S</i> , (#val   reg)                                                     | The signal value of S is set $(sigdecl \in \{input, output, signal\}).$                                                                                                                                                                   |

| $ \begin{array}{c} x := x + 1 \\ x := x - 1 \\ x := x * 2 \end{array} $ | ADD X,#1<br>SUB X,#1<br>MUL X,#2                                                 | Other supported register opera-<br>tions are ORR,ANDR,XORR.                                                                                                                                                                               |

| if x > y then<br>p<br>else<br>q<br>end if                               | CMP X,Y<br>JW G, elseAddr<br>P<br>GOTO endAddr<br>elseAddr:<br>Q<br>endAddr:     | Jump to <i>elseAddr</i> if the JW com-<br>pare for G fails. No GOTO<br>statement when the <i>else</i> body is<br>empty. Other compare opera-<br>tions are GE,L,LE,EE,NE match-<br>ing greater equal, lower (equal),<br>equal and unequal. |

| $\mathbf{x} := \mathbf{f}(5,\mathbf{y})$                                | LOAD _TMP0,#5<br>LOAD _TMP1,Y<br>CALL F<br>LOAD X, _TMP0<br><br>F:<br><br>RETURN | The arguments are loaded to function interface registers TMPi, as after the CALL the result. To address label F the function body of $F$ is compiled.                                                                                     |

|                                                                         | CLRC                                                                             | Clear the carry bit.                                                                                                                                                                                                                      |

|                                                                         | SETC                                                                             | Set the carry bit to '1'.                                                                                                                                                                                                                 |

|                                                                         | SR[C]                                                                            | Shift right. Use also the carry bit by SRC.                                                                                                                                                                                               |

|                                                                         | SL[C]                                                                            | Shift left.                                                                                                                                                                                                                               |

|                                                                         | NOTR                                                                             | Bit inversion.                                                                                                                                                                                                                            |

Figure 2.6: KEP Instruction Set: Interface and Computational Expressions

## 3 Preprocessing: Esterel Dismantling

This chapter describes an Esterel to Esterel transformation, called *Esterel disman*tling, which is very similar to the transformation of Esterel statements to kernel statements in the Esterel Primer [7]. The Esterel programs p are translated to semantically equivalent Esterel programs p', whereby p' is part of a syntactical subset of Esterel:

$$p \rightsquigarrow_{dis} p'$$

whereby  $\llbracket p \rrbracket = \llbracket p' \rrbracket$ .

This subset has the same expressiveness as Esterel, but uses less and simpler statements. Although many statements are dismantled into their kernel statements, the strl2kasm dismantles to a Esterel subset that is a superset of the Esterel kernel statements, because the KEP assembler syntax directly supports some non kernel statements like abort.

This transformation allows the integration of Esterel statements that are not directly supported by the KEP, like the every statement or complex variations of the await, and reduces hereby the amount of syntactical constructs that have to be handled by the compiler in later compilation steps.

The dismantling technique makes the strl2kasm flexible in the use of the input Esterel syntax, it obtains the downward compatibility of older Esterel programs with outdated syntax like the do watching statement, which is replaced by an abort as described in the Esterel Language Primer [7]. It might provide also the upward compatibility to future syntax extensions, provided that the CEC parser is also updated and an appropriate Esterel translation exists, so that the following compilation steps are not affected. However, possible new language constructs that expand the expressiveness of Esterel cannot be handled by dismantling and therefore would effect all compilation steps.

Note that the dismantling is a recursive process, on the one hand the bodies of complex statements are also dismantled, on the other hand some dismantled statements might be dismantled again, until they reach an atomic statement level.

## 3.1 Module/Run Dismantling

Esterel programs consists of modules. A module can be instantiated within another module by using the run statement. Recursive or mutually recursive module instantiation is forbidden [7] so it is possible to replace each run statement by its module body to get a program with only one module, the main module. This module expanding technique is implemented within the CEC [15] and the strl2kasm will make use of it as the first action after parsing.

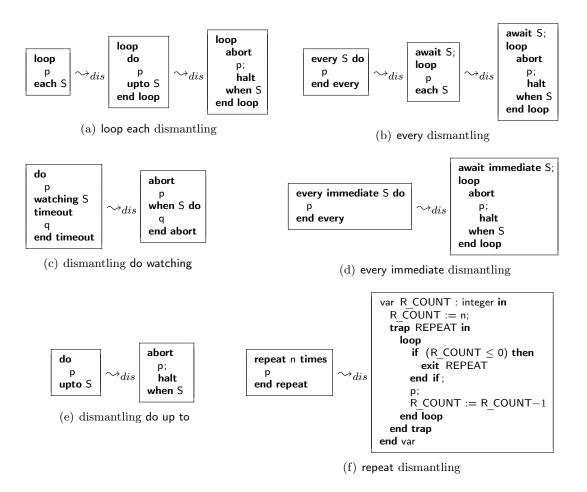

Figure 3.1: The dismantling in (c) and (e) describes how the outdated statements do watching and do up to are handled respectively. The other figures describe the dismantling of the temporal loops loop each and every and the finite loop repeat. Note that the signal expression in loop each has to be nonimmediate. All these Esterel loop variants are described in the Esterel Primer [7]. Note that a module that is not instantiated by a run statement will not be expanded. So it is possible in a program of multiple modules that there are still multiple modules even though the module expanding is performed, in such a case the unused modules will be ignored. Nevertheless the following compilation steps of the strl2kasm expect a single module program.

## 3.2 Dismantling of Temporal and Finite Loops

The loop each statement is a temporal loop, its body is started initially and restarts when the loop each signal expression occurs. After the termination of its body the loop halts waiting for the signal expression. This behavior is matched by a combination of a simple loop and a do up to over the loop each body, see Figure 3.1 (c).

The delay cannot be immediate, otherwise the abort would be instantaneous and infinitely often restarted by the loop. Such an instantaneous loop is not allowed in Esterel. The strl2kasm throws an error message when the loop each signal expression has the immediate attribute.

As described in the Primer [7], the every statement is the second type of temporal loop. The difference to the loop each is that its signal expression is initially awaited before its body is started.

It is also possible that the delay is immediate, in that case the await placed in front is also immediate, but for the following loop each the immediate has to be removed, otherwise the loop body would be instantaneous, as described before.

Unlike loop and temporal loops the repeat statement executes its body only for a finite number of times, but the body nevertheless has to be non-instantaneous. How often the repeat body is executed is specified by an integer expression. If this expression is lower or equal to zero, the repeat statement terminates instantaneously. Determining the positiveness is in general hard to compute and might be statically not possible, so it is not allowed to have the repeat as loop body.

The basic idea of the repeat dismantling is to put the repeat body into a loop. To make this possible the repeat body has to be non-instantaneous. A counter register of name R\_COUNT is initialized before the loop starts. At the beginning of the loop it is tested whether the count is lower or equal to zero and if true, the loop terminates. This is realized by putting the loop within a simple trap. At the end of the loop the counter is incremented by one. In Figure 3.1 (f) the repeat dismantling is described. The dismantling of nested repeat statements uses variables R\_COUNT\_i with  $i \in \mathbb{N}_0$  to distinguish the different variable counts.

## 3.3 Priority Dismantling

Under some circumstances it is necessary to dismantle the Esterel statements halt and await, even though they are directly supported by the KEP. Due to the KEP concurrency model, which uses multi-threading via priorities to ensure the correct

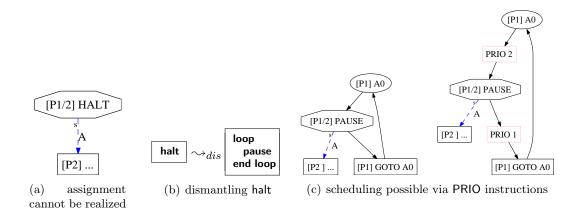

Figure 3.2: This example explains why the priority dismantling is necessary to ensure the KEP multi-threading via priorities. In (a) the HALT instruction has a priority assignment of [P1/2], which means that it should have priority of one and in the next instant its priority must be increased to two, but only if signal A occurs, otherwise its priority has to be one again. This cannot be realized via PRIO instructions, as explained in the text. So we dismantle the halt, see (b), and we can insert PRIO instructions to get the correct behavior, see (c).

execution order according to the semantics of Esterel, the so called priority assignment is performed, see Chapter 6, which tries to fulfill all signal dependencies. After the assignment, appropriate PRIO instructions are inserted to realize the priority assignment.

Not all statements are executed instantaneously, some might be active for several instants. These statements are called *delayed statements*. During these instants, such a statement might have different priorities, depending on the current signal environment, but once assigned, the HALT and AWAIT would hold their priority for all following instants. It is only possible to have two priorities for an instruction at maximum, the first is for the current instant and the second, possibly higher priority, if necessary, for all following instants. The priority assignment takes this into account by assigning an additional priority for the next instant called *prio next*, which becomes valid after the current instant is executed and the next one is started. Only the PAUSE instruction allows to implement this behavior as explained in the following. So the solution is to dismantle all delayed statements onto a level, where the only *delayed* statements are PAUSE instructions.

Figure 3.2 illustrates the problem. The priority assignment might have computed for the delayed instruction HALT a priority of one and a next priority of two, denoted by [P1/2]. The next value depends on the signal A: only when A occurs and the HALT is aborted, the next instruction, which must have for some reason a priority of two, is executed and so the HALT must have a priority of at least two. So the priorities

Figure 3.3: This example shows a priority cycle caused by a sustain statement. Note that in (b) the AWAIT instruction is normally dismantled, but to make the dependency cycle easier to illustrate, it is retained. This cycle is solved by dismantling the sustain, so it possible to insert PRIO instructions in between the writer and reader part to run them in different priorities.

#### 3 Preprocessing: Esterel Dismantling

of the HALT should be always one, except the last instant, when it is aborted, but this point of time might vary and depend on the signal content. Nevertheless, as mentioned, the execution of the PRIO 2 before the HALT would result in a higher priority of two for all the following instants, violating the assignment. If PRIO 2 is not executed, the HALT will always have the priority of one, which also violates the assignment. It is in general not possible to schedule a KEP assembler program with non-PAUSE delayed instructions via PRIO instructions. By dismantling the halt to its kernel statements (b), as described in the Esterel Primer [7], the resulting KEP program can be scheduled. As seen in (c), the insertion of a PRIO 1 and PRIO 2 instruction can now ensure the desired behavior.

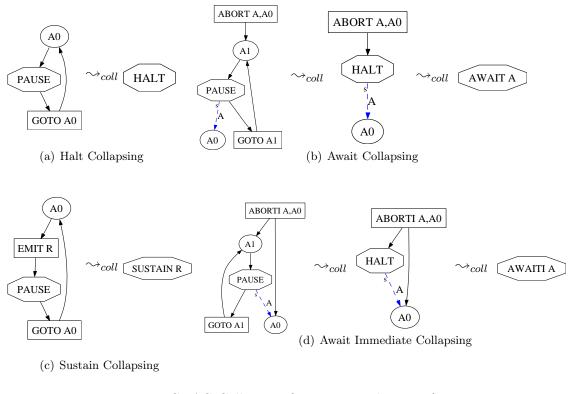

Note that if a delayed statement has to be executed after compiling with the same priority for all instants, the dismantling is not necessary. This can be ensured for statements that are part of the main thread. The strl2kasm uses an optimization technique, called *collapsing* (see Section 7.2), to use yet again the HALT, AWAIT and SUSTAIN instructions if possible. If no PRIO instructions were inserted within a dismantled instruction, then this instruction runs always with the same priority and the collapsing will undo the dismantling.

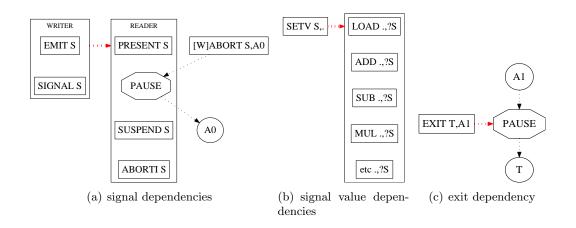

For the same reason as halt and await, the sustain has to be dismantled, because this statement is also delayed and can be active for several instants, whose number may vary. But there is yet another reason, why the sustain must be dismantled, namely to eliminate potential dependency cycles. Even if the problem described before is solved by enlarging the KEP assembler syntax to allow delayed statements to run in different priorities without being dismantled, the sustain has still to be dismantled. The SUSTAIN S instruction influences the status of signal S (is a writer of S) and must be executed before instructions that depend on S's status are executed, e.g., the PRESENT S instruction is a reader of S. In this behavior the SUSTAIN is a writer, but it can also be a reader to another signal, when occurring within an according strong ABORT scope to that signal, because of the delayed control flow. Being a writer and a reader at the same time, whereby writers must have potentially high and readers low priorities, can result in a dependency cycle. In Figure 3.3 (b) the SUSTAIN R instruction/node is a writer to the AWAIT R and a reader of the EMIT A, because the SUSTAIN R occur in the scope of the WABORT A,A3. The writer-reader relation is denoted by dotted lines in the graph. The priority of a writer has to be greater than the of its reader, so the SUSTAIN R priority must be greater than the of AWAIT R and on the other hand the priority of EMIT A has to be greater than the of SUSTAIN R. Since priorities cannot increase instantaneously within a thread (see the control flow constraints in Section 6.2), the following inequation has to be solved in order to assign a schedule:

$prio(SUSTAIN R) < prio(EMIT A) \leq prio(AWAIT R) < prio(SUSTAIN R).$

Because  $prio(SUSTAIN R) \not< prio(SUSTAIN R)$  holds true, it is not possible to solve the inequation, a so called program cycle is found.

By dismantling the sustain statement, none of the resulting statements will be reader and writer at the same time. The writing part corresponds to the EMIT instruction and the reading part to the PAUSE. Within their execution order the EMIT comes first, so it is possible to avoid the potentially dependency cycle, by inserting PRIO instructions in between. The writer instruction can now run with a greater priority than the reader instruction, which was not possible when these instructions were bounded together within the SUSTAIN.

In the example in Figure 3.3 (d) the resulting priority constraints become:

$prio(PAUSE) < prio(EMIT A) \leq prio(AWAIT R) < prio(EMIT R).$

This inequation can be solved, because prio(PAUSE) < prio(EMIT R) is possible and is realized by a PRIO instruction, which lowers the priority. Note that the second PRIO instruction, which increases the priority, takes effect in the next instant, where the EMIT R instruction must have its higher priority again.

Another example of a writer-reader statement is the valued emit of a non-literal value, because the value might be a reader, e.g., an emit S,?T statement is a writer to S and a reader to T. The basic idea to solve this problem is to split the writing and reading parts, as done in the sustain case. The writing part is the signal emission and the reading part the assignment of the signal's value, so the dismantled result would look like emit S; "S := ?T". However such an Esterel statement, which assigns a signal value without emitting this signal at the same time does not exist, at least not in Esterel v5. But the KEP assembler instruction set has such an instruction, the SETV instruction, so the separation of writer and reader is performed during the compilation on the KEP level, see Section 5.2.1, into EMIT S followed by SETV S,?T.

## 3.4 Simplification of Complex Signal Expressions

The Esterel signal expressions, which occur in present, await, abort and suspend statements, can have several non-simple forms. In the following three different types of non-simple expressions are presented.

The signal expressions of await, abort and suspend could be delayed by a preceding positive integer expression, called the *delay*. The specific statement is delayed by that factor, waiting that its signal expression is active accordingly often, before it continues. Note that the simple case is equivalent to a delay of one, whereby a 'delay of zero' is called *immediate* and is inverse to a delay; such an immediate expressions is not per se dismantled, because these are directly supported by the KEP assembler instruction set. The present has no delayed expressions, due to the fact that it is always executed instantaneously.

Another type of signal expression are the *Boolean operations*, which are part of the first order predicate calculus, consisting of the binary and or operations and the unary not operation with signals as atomic expressions.

These kind of expressions can be combined, a short overview of the signal expres-

Figure 3.4: The dismantling of the ABRO example. First the loop each is dismantled, then the await statements and the first halt, after that the two halt statements resulting from the await dismantling are again dismantled. Then the dismantling is completed, because no more dismantling rules are applicable.

#### 3.4 Simplification of Complex Signal Expressions

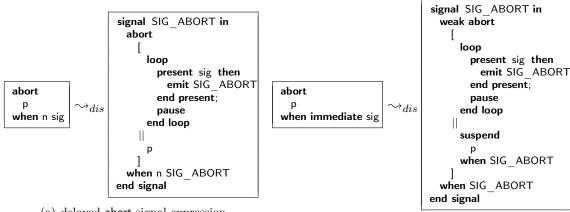

(a) delayed **abort** signal expression

(b) immediate abort signal expression

```

Figure 3.5: The dismantling of Boolean Operations in abort signal expressions is shown, first if the signal expression is delayed by integer n and second when it is immediate.

```

sion grammar:

atomic signals:

$$S = S_1 | S_2 | \dots | A | B | \dots$$

Boolean operation:  $sig = S | not sig | (sig or sig) | (sig and sig)$

[delayed] signal expression:  $dsig = sig | n sig$  where  $n \in \mathbb{N}$ .

The next complex form of signal expression is the *case expression*, which are enumerations of signal expressions. The signal expressions in turn are no case expressions, but might be Boolean operations and/or delayed, if the relevant statement allow delays. The cases are considered in the order they appear in the program. The present, abort and await statements allow case expressions, the suspend does not.

Not all combinations are allowed in each Esterel statement, e.g., the present case expression consists only of sig expression and not dsig, because it is always executed instantaneously and therefore cannot be combined. On the other hand dsig expressions are allowed in await case and abort case statements. For more details about the Esterel grammar, especially about the Esterel signal expressions, see [9].

The signal delay is compiled into the KEPregister operation LOAD \_COUNT, n to initialize the KEPdelay count \_COUNT with the specific delay n, see Section 5.2 for further details. Case Expressions might contain an unlimited number of cases and Boolean operations could be arbitrarily nested, therefore an assembler syntax of fixed bit size cannot match such expressions in general.

The complex Esterel expressions are dismantled to appropriate statements with atomic expressions, if necessary, as described in the following.

(c) dismantling present case

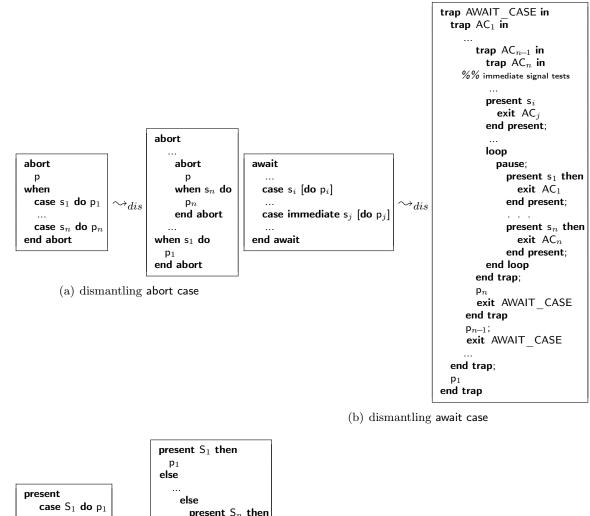

Figure 3.6: The dismantling of Esterel statements with case expressions. (a): The abort cases are nested and held the preemption order of the signal expressions  $s_i$ . (b): The await cases are tested each instant in a loop, which exits according to nested traps. (c): The present case results in the nesting of several simple present statements, the if case is analog dismantled to simple ifs.

#### 3.4.1 Case Expressions

Case expressions occur in conditional statements, namely present and if, and in await and abort constructs. In the following the dismantling of all case statements is described in detail.

The present case is semantically equivalent to an else if like expression:

present ... else present ... else present ... end,

and is accordingly dismantled into nested non-case present statements, see Figure 3.6 (c).

According to the Esterel semantics the present case expressions are tested in sequence from first to last as long as an expression is fulfilled, then the according bodies are executed or the next statement in sequence to the present case if no body exists. This behavior is matched by n statements for n cases, whereby each present statement is the else body of the previous present statement, except for the first, which has no predecessor. The last and most inner else body is the default body of the present case statement, see Figure 3.6 (c). If a one case of a present case expression has no body, it is dismantled to a present-else statement with no then body, the else body remains as previously explained.

The single case version of the present case is not dismantled, because it is equivalent to the present ... then ... [else ...] end version of the present. So the dismantling takes only place for the multiple cases. Note that the simple present statement is represented in the Abstract Syntax Tree (AST), after being parsed, as a single case present case statement. Therefore the dismantling process, which replaces a (multiple) present case through several nested simple presents, will result in nested single case present case statements.

The if case statement is very similar to the present case, they distinguish in the type of conditional expression, the if case tests for a standard Boolean expression instead of the Boolean signal expression as explained above. Apart from this, its dismantling works the same way and needs no further explanation.

The await case statement waits simultaneously with all its signal expressions till one occurs, then it stops and executes at least one do body. That one of the first active signal expression is executed, if it has no do body, no do body is executed at all for this await case. The dismantling will take this into account. The await case could be dismantled to an abort case with a halt as body, but for performance issues, it is separately dismantled.

The await case behavior is matched by a loop with a pause statement as body and several signal testing via present statements to this loop, see Figure 3.6 (b). The loop is exited by several exit statements of related trap statements, which are placed around the loop, one trap for each case. They are nested from outer to inner according to their case sequence from first to last. Their symbol names are named with AC followed by an integer for distinction. The case bodies are placed behind their specific trap statements. An additional trap of name AWAIT\_CASE[\_i] is positioned around the whole dismantle expression to exit the expression after the execution of a case body has taken place. If no body is specified for a given case, no trap label is needed

#### 3 Preprocessing: Esterel Dismantling

to jump for, the control flow can start directly at the next statement, so an exit statement is created to the most outer trap label AWAIT\_CASE[\_i] and no own trap  $AC_j$  is created for it. So it does not matter whether the cases have do bodies or not, this additional trap is always needed. The number of used traps statements is bounded to be at most the number of cases plus one, if each case has a body, and to be at least one if there are no case bodies at all.

The abort case prioritizes the various signal expressions according to their sequence within its case expression. The nesting of abort also allows prioritizing of signal expressions, the outer more an abort the higher the preemption. Thus the dismantling process converts the abort case into multiple nested abort statements, see Figure 3.6 (a).

### 3.4.2 Boolean Signal Expressions

Boolean signal expressions occur in the signal reading statements: await, abort, suspend and present. The Boolean signal expressions of the non-instantaneous statements await, abort and suspend can also be delayed or immediate. The present is instantaneously executed and therefore has no delay. The KEP does not support Boolean signal expressions directly in its instruction set architecture, so they have to be simplified to simple atomic expressions.

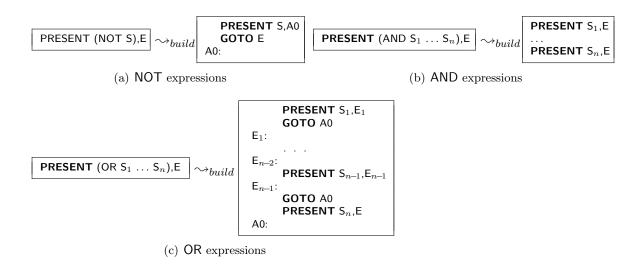

The present statement cannot be dismantled in general without duplicating one of its bodies, thus violating the Write Things Once (WTO) principle. The nesting of a present-or expression leads to a duplication of the *then* body, the present-and to a duplication of the *else* body. This may increase the code size exponentially for accordingly nested Boolean signal expressions of the present. Therefore expressions in present statements are handled later during the creation of the KEP assembler instructions and not at the Esterel level (see Section 5.2.1 and Figure 5.3).

The await statements that contain Boolean signal expression are handled the same way as the simple await with atomic signal expressions, they are dismantled to an abort statement of the same Boolean signal expression with a halt statement as body. This is done both for the delayed or immediate expressions.

The dismantling of abort statements with Boolean signal expressions is split in two cases, the non-zero and the zero delay case, both can be seen in Figure 3.5. In both cases a new local signal  $SIG\_ABORT$  is created to replace the original signal expression sig of the abort. If sig occurs, signal  $SIG\_ABORT$  should be present to abort the body p, this is realized by a parallel extension of p, where each instant is tested, whether sig is present, and if present, signal  $SIG\_ABORT$  is emitted. A delay n of sig is transferred to  $SIG\_ABORT$  without the need for further modifications.

In case of an immediate sig, the abort is made weak to allow the immediate abortion from within the (now) weak abort statement. The semantic of a weak abort recommends that all instantaneously executable statements are executed, especially p, even if  $SIG\_ABORT$  is present, which would violate the former behavior of an strong abortion. This problem is fixed by putting p into a suspend with trigger  $SIG\_ABORT$ .

# 4 The Concurrent KEP Assembler Graph (CKAG)

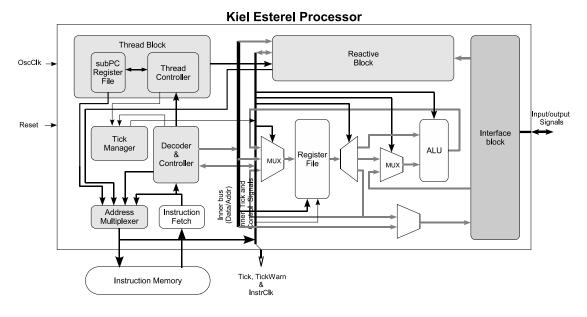

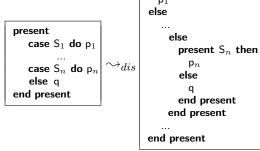

During the compilation from Esterel to KEP assembler, an intermediate graph structure is used that represents the control flow of the resulting KEP assembler. This structure, called the *Concurrent KEP Assembler Graph* (CKAG), is a directed graph with KEP assembler instructions as nodes and several edge types to match the normal composition of instructions, denoted by *control flow edges*, as well as preemptive control flow, denoted by *preemption edges*.

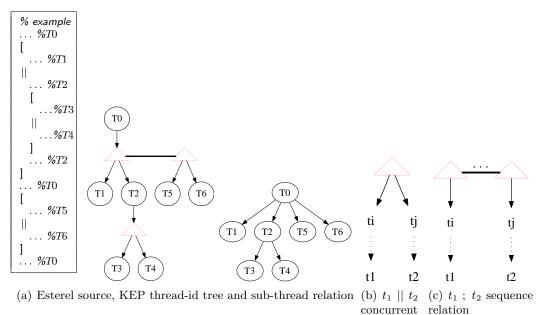

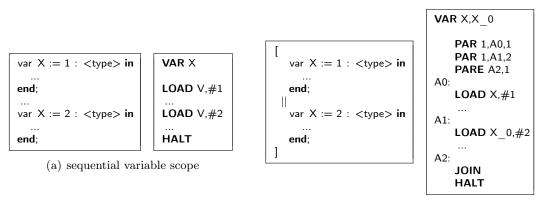

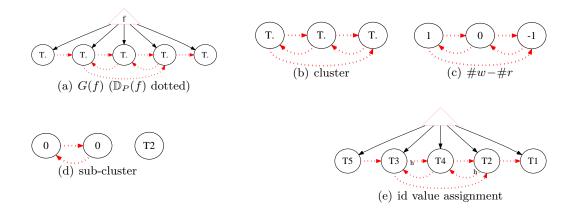

The graph structure is named *concurrent*, because it allows the representation of concurrent control flow by using so called *fork nodes*. This is an advancement in comparison to its predecessor version, the KAG [29], which was designed for sequential programs only. The CKAG additionally provides *join nodes* to join again the control after being forked, whereby the *fork nodes* and *join nodes* represent the PAR/PARE and JOIN instructions of the according KEP assembler program, respectively.

The CKAG is required to realize the priority assignment [28], needed to ensure the parallel semantics of Esterel, as well as for the Worst Case Reaction Time (WCRT) analysis [12]. The optimizations performed by the compiler like dead code elimination and the instruction collapsing, (see Chapter 7) are realized on the CKAG structure, too. It would be possible to implement these computations directly on the KEP assembler instructions, which are a list. However, it would be much less efficient to find the label addresses of, e. g., GOTO, PRESENT and ABORT instructions, because the next instruction in the control flow is in general not its successor in the instruction list. This is even worse for the preemptive control flow. In the CKAG the control flow successors are directly and efficiently accessible. Nevertheless the KEP assembler instructions and its CKAG are closely related and a change in the CKAG implies a change in the KEP assembler and vice versa. E.g., if a node in the CKAG is removed, the according instruction has to be removed from the KEP instructions.

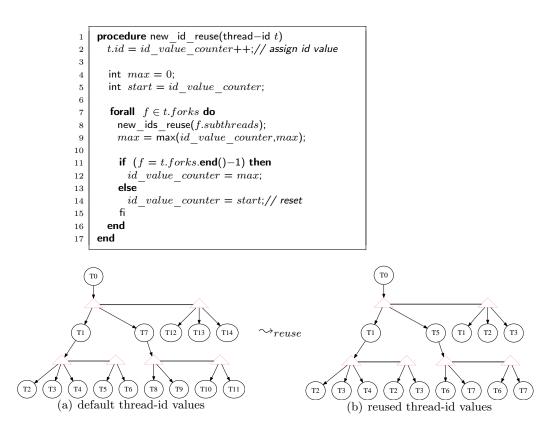

Each time PAR/PARE instructions are created the control flow is split into several sub-threads. As this can happen recursively, the resulting thread structure might be complex. To easily identify semantically dependent statements that might be executed concurrently, the subthread hierarchy induced by the *fork nodes* is made abstract as a tree structure (see Section 4.2). This structure can also be used to optimize the use of the thread-id values defined by PAR (see Section 7.5).

Before describing the graph building process from Esterel source, the CKAG with all related structures is defined and explained in detail. First are all node and edge types of the CKAG presented, followed by the according thread-id tree and some conditions about the scopes of all KEP signal, register and address names.

Figure 4.1: Nodes and edges of the Concurrent KEP Assembler Graph (CKAG).

We define the CKAG structure as a directed graph with nodes N and different types of edges E and P:

**Definition 4.1** (Concurrent KEP Assembler Graph (CKAG)). A CKAG C of a KEP program p is given by

$$C = C(p) = (N, E, P)$$

with node set N, edge set  $E \subseteq N \times N$  and preemption edges P. Each preemption edge is a tuple of preemption type  $k \in K := \{s, w, e\}$  and signal symbol  $s \in S$ , where S is defined as the set of signal symbols. The preemption type indicates whether the preemption results from strong abort, weak abort or an exit, and the signal symbol by which signal the preemption is triggered.