# A Generic Framework for the Topology-Shape-Metrics Based Layout

Paul Klose

Master Thesis October 2012

Christian-Albrechts-Universität zu Kiel Real-Time and Embedded Systems Group Prof. Dr. Reinhard von Hanxleden

Advised by: Dipl-Inf. Miro Spönemann

## Abstract

Modeling is an important part of software engineering, but it is also used in many other areas of application. In that context the arrangement of diagram elements by hand is not efficient. Thus, layout algorithms are used to create or rearrange the diagram elements automatically in order to free users from this. However, different types of diagrams require different types of layout algorithms.

Planarity and orthogonality are well-known drawing conventions for many domains such as UML class diagrams, circuit schemata or entity-relationship models. One approach to arrange such diagrams is considered by Roberto Tamassia and is called Topology-Shape-Metrics approach, which minimizes edge crossings and generates compact orthogonal grid drawings. This basic approach works with three phases: the planarization, the orthogonalization, and the compaction. The implementation of these phases are considered in this thesis in detail with respect to a generic, extensible architecture, such that every phase can be exchanged with different alternatives. This leads to a considerable amount of flexibility and expandability. Special handling of high-degree nodes has been implemented based on this architecture. Moreover, approach and implementation proposals for interactive planarization and for handling edge labels, hypergraphs and port constraints are presented.

## Eidesstattliche Erklärung

Hiermit erkläre ich an Eides statt, dass ich die vorliegende Arbeit selbstständig verfasst und keine anderen als die angegebenen Quellen und Hilfsmittel verwendet habe.

Kiel,

# Contents

| 1 | Intr | oduction 1                                                    |

|---|------|---------------------------------------------------------------|

|   | 1.1  | Related Work                                                  |

|   | 1.2  | Contributions                                                 |

|   | 1.3  | Overview                                                      |

| 2 | Prel | iminaries 7                                                   |

|   | 2.1  | Basics of Graph Drawing                                       |

|   |      | 2.1.1 Flow Networks                                           |

|   |      | 2.1.2 Drawing Conventions                                     |

|   |      | 2.1.3 Aesthetics Criteria 15                                  |

|   | 2.2  | Topology-Shape-Metrics Approach                               |

|   | 2.3  | Kiel Integrated Environment for Layout Eclipse Rich Client 18 |

|   |      | 2.3.1 KIELER Infrastructure for Meta Layout                   |

|   | 2.4  | KLay Architecture                                             |

|   |      | 2.4.1 KLay Planar Architecture                                |

| 3 | Plar | narization 23                                                 |

|   | 3.1  | Planarity Testing                                             |

|   | 3.2  | Edge Insertion                                                |

|   |      | 3.2.1 Face Calculation                                        |

| 4 | Ortl | hogonalization 31                                             |

|   | 4.1  | Preliminaries                                                 |

|   | 4.2  | Tamassia's Approach                                           |

|   |      | 4.2.1 Angles and the Orthogonal Representation                |

|   |      | 4.2.2 Orthogonalization Network Flow                          |

|   |      | 4.2.3 Compute Orthogonal Representation                       |

|   | 4.3  | Preprocessing                                                 |

|   |      | 4.3.1 The External Face                                       |

### Contents

| 5  | Con   | npaction                              | 41  |

|----|-------|---------------------------------------|-----|

|    | 5.1   | Tidy Rectangular Compaction           | 42  |

|    |       | 5.1.1 Again the Flow Network          | 43  |

|    |       | 5.1.2 Simple Flow Solving             | 45  |

|    | 5.2   | Preprocessing                         | 48  |

|    |       | 5.2.1 Insertion of Bend-Point Dummies | 48  |

|    |       | 5.2.2 Making Faces Rectangular        | 49  |

|    |       | 5.2.3 Face Sides                      | 61  |

|    | 5.3   | Postprocessing                        | 63  |

|    |       | 5.3.1 Grid Drawing                    | 63  |

|    |       | 5.3.2 Dummy Removal                   | 66  |

| 6  | Exte  | ensions                               | 71  |

|    | 6.1   | Node Degree Higher Than Four          | 71  |

|    |       | 6.1.1 Implementation                  | 74  |

|    | 6.2   | Interactive Planarization             | 79  |

|    | 6.3   | Optimal Embedding                     | 81  |

|    | 6.4   | Compaction                            | 81  |

|    | 6.5   | Planar Drawing Alternatives           | 82  |

|    | 6.6   | Handling Directed Edges               | 84  |

|    | 6.7   | Hypergraphs                           | 86  |

|    | 6.8   | Port-Constraints                      | 88  |

|    | 6.9   | Edge Enhancement                      | 88  |

|    |       | 6.9.1 Edge Labels                     | 89  |

|    |       | 6.9.2 Multi-Edges                     | 91  |

|    |       | 6.9.3 Self-Loops                      | 92  |

| 7  | Con   | clusion                               | 95  |

|    | 7.1   | Evaluation                            | 95  |

|    | 7.2   |                                       | 103 |

| Bi | bliog | raphy                                 | 105 |

# List of Figures

| 1.1  | Different layouts for the same diagram                               | 2  |

|------|----------------------------------------------------------------------|----|

| 1.2  | Entity-relationship diagram                                          | 3  |

| 2.1  | Directed graph with self-loop                                        | 8  |

| 2.2  | Subdivision example                                                  | 8  |

| 2.3  | Drawings of the smallest non-planar graphs                           | 9  |

| 2.4  | Different representations of a graph                                 | 10 |

| 2.5  | Different drawings illustrating upward planarity                     | 11 |

| 2.6  | Different drawings showing drawing conventions                       | 14 |

| 2.7  | Steps of the TSM approach                                            | 17 |

| 2.8  | KIML structure overview                                              | 19 |

| 2.9  | KLay architecture overview                                           | 20 |

| 2.10 | KLay Planar architecture                                             | 21 |

| 3.1  | DFS-tree creation                                                    | 24 |

| 3.2  | Back-edge insertion                                                  | 25 |

| 3.3  | Planar embedding of Figure 3.1a                                      | 26 |

| 3.4  | Edge insertion example                                               | 27 |

| 3.5  | Result of the edge insertion of Figure 3.4                           | 28 |

| 3.6  | Simple connected graph example                                       | 28 |

| 3.7  | Calculation of the left and right face                               | 29 |

| 4.1  | Flow network example with its corresponding residual network         | 32 |

| 4.2  | Vertex- and bend-angles of a planar orthogonal drawing               | 33 |

| 4.3  | Orthogonal drawing with four vertices and four bends                 | 34 |

| 4.4  | Illustration of the transportation problem                           | 35 |

| 4.5  | Transformation of a planar embedding to a flow network               | 36 |

| 4.6  | Angle mapping from network flow to original graph                    | 38 |

| 4.7  | Area discrepancy of the same embedding with different external faces | 40 |

| 5.1  | Example of orthogonal representation with rectangular faces          | 42 |

| 5.2  | Example for minimum cost flow in the context of the compaction       | 44 |

## List of Figures

| 5.3  | Flow increasing example                                                           | 47       |

|------|-----------------------------------------------------------------------------------|----------|

| 5.4  | Example for bend-point dummy node insertion                                       | 49       |

| 5.5  | Orthogonal representation containing faces with non-rectangular shape             | 50       |

| 5.6  | Refining the external face of the orthogonal representation of Figure 5.5         | 53       |

| 5.7  | Problems with the edge extensions                                                 | 55       |

| 5.8  | Refinement of the faces of an orthogonal representation with a cutvertex          | 58       |

| 5.9  | Two examples for orthogonal representations with cutedges                         | 60       |

| 5.10 | Representation with marked face sides                                             | 61       |

| 5.11 | Grid drawing of $K_{3,3}$ with marked edge lengths                                | 64       |

| 5.12 | Increasing of the grid positions                                                  | 65       |

| 5.13 | Removal of rectangular shape dummies                                              | 66       |

| 5.14 | Removal of bend dummies                                                           | 67       |

| 5.15 | Removal of planarization dummies                                                  | 68       |

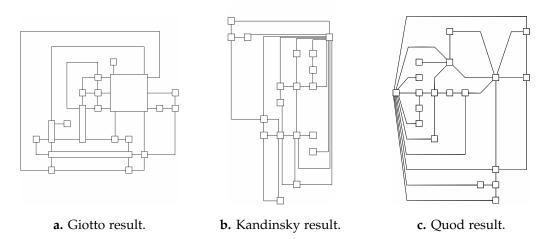

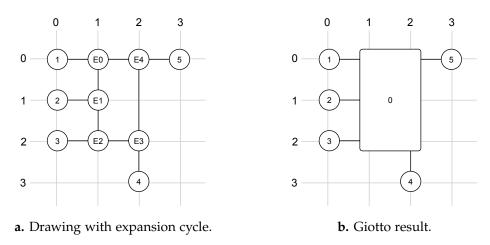

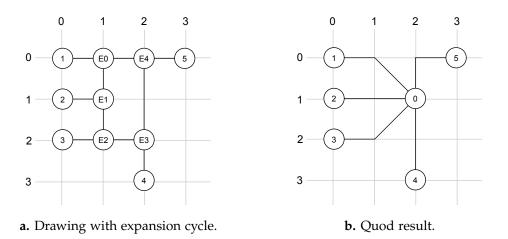

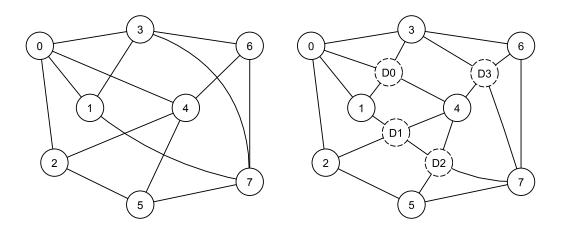

| 6.1  | Planar graphs drawn with different high degree approaches                         | 72       |

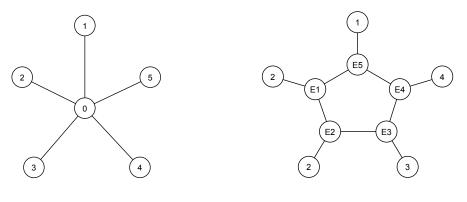

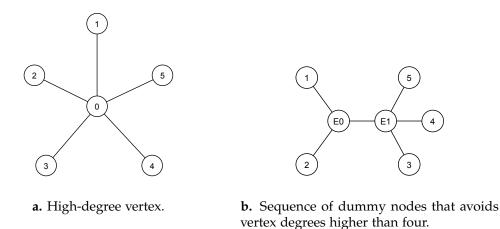

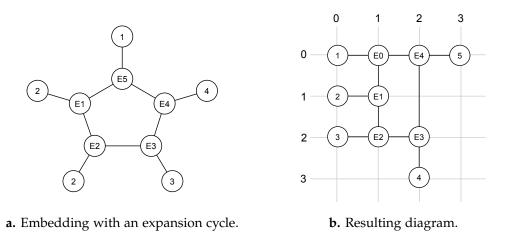

| 6.2  | Transformation of a high-degree node into an expansion cycle                      | 73       |

| 6.3  | Transformation of a high-degree node into an sequence of dummy                    | 74       |

| ( )  | nodes                                                                             | 74       |

| 6.4  | Performing orthogonalization and compaction on expansion cycle .                  | 75       |

| 6.5  | Back transformation to the high-degree node with Giotto approach .                | 77<br>78 |

| 6.6  | Back transformation to the high-degree node with Quod approach .                  |          |

| 6.7  | Planarization with preserving the given embedding                                 | 80       |

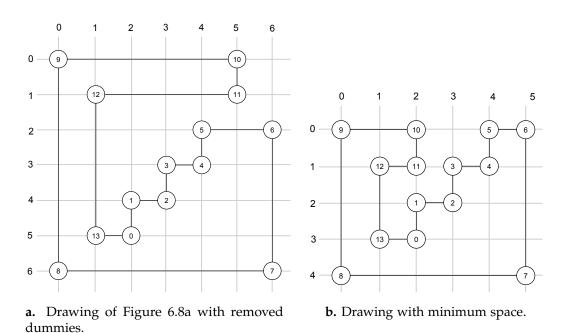

| 6.8  | Two drawings with different edge length, respectively different draw-<br>ing area | 82       |

| 6.9  | Triangulating a planar graph bases on the canonical ordering                      | 83       |

|      | An example of a planar straight-line drawing                                      | 83<br>84 |

|      | Snippet of KLay Planar class diagram                                              | 85       |

|      | Two representations with different layering strategies                            | 86       |

|      | Different representations of a hypergraph                                         | 87       |

|      | Example graph containing labeled multi-edges and labeled self-loops               | 89       |

|      | Different labeled drawings of the same orthogonal representation                  | 90       |

|      | 0 0 1                                                                             | 90<br>91 |

|      | Processing steps of handling multi-edges                                          |          |

| 0.17 | Handling of self-loops                                                            | 92       |

| 7.1  | Drawing $D_1$ computed with KLay Force                                            | 96       |

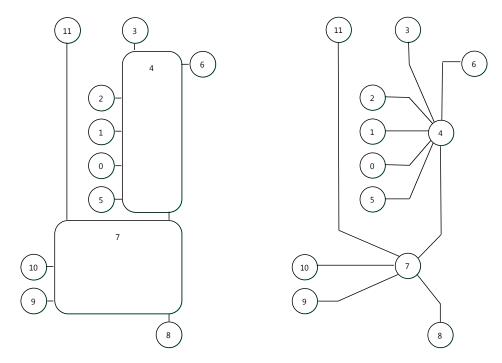

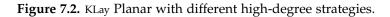

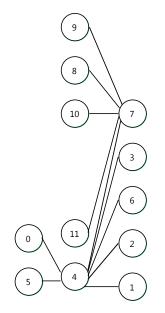

| 7.2  | KLay Planar with different high-degree strategies                                 | 96       |

| 7.3  | Drawing $D_1$ computed with KLay Layered                                          | 97       |

## List of Figures

| 7.4  | Drawing $D_2$ computed with KLay Force                | 98  |

|------|-------------------------------------------------------|-----|

| 7.5  | Drawing $D_2$ computed with KLay Layered              | 98  |

| 7.6  | Drawing $D_2$ computed with OGDF orthogonal algorithm | 99  |

| 7.7  | Drawing $D_2$ computed with KLay Planar               | 99  |

| 7.8  | Drawing $D_3$ computed with KLay Layered              | 100 |

| 7.9  | Drawing $D_3$ computed with OGDF upward planarity     | 101 |

| 7.10 | Drawing $D_3$ computed with KLay Planar               | 102 |

# List of Tables

| 4.1<br>4.2               | The architecture of the orthogonalization                                                                                                                                            |                      |

|--------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|

| 5.1<br>5.2<br>5.3<br>5.4 | The architecture of the compaction                                                                                                                                                   | 41<br>51<br>59<br>60 |

| 6.1<br>6.2<br>6.3        | Advantages and disadvantages of the different high degree approaches<br>The adjusted preprocessor list of the orthogonalization<br>The adjusted postprocessor list of the compaction | 75                   |

| 7.1<br>7.2<br>7.3        | Analysis of different drawings of $D_1$                                                                                                                                              | 99                   |

# Abbreviations

- тям Topology-Shape-Metrics

- KIEL Kiel Integrated Environment for Layout

- KIELER Kiel Integrated Environment for Layout Eclipse Rich Client

- **KIML** KIELER Infrastructure for Meta Layout

- KLay KIELER Layout Algorithms

- **OGDF** Open Graph Drawing Framework

- UML Unified Modeling Language

- MCF Minimum Cost Flow

- **SSP** Successive Shortest Path

- **BFS** Breadth First Search

- **DFS** Depth First Search

- DFI DFS Index

# Introduction

"The usefulness of a drawing of a graph depends on its readability that is, the capability of conveying the meaning of the graph quickly and clearly." Roberto Tamassia [Di +99].

Computer systems as well as the hard- and software development usually consist of large complex conceptual structures. In many cases, people that hold different experiences and knowledge backgrounds are involved in these processes. Thus, the design of such structures needs to be comprehensible to let all participants work in the same, desired direction.

Frequently, graphical representations are used to model relations in such areas of application. Especially graphs are used to represent relations between different objects in diagrams. Examples of such representations are circuit schematics, state diagrams, and database dependencies for application developers.

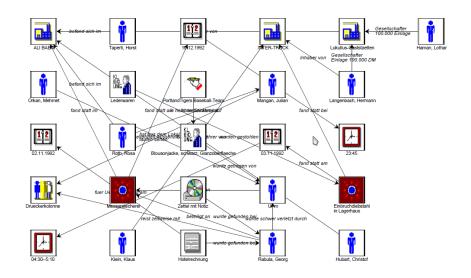

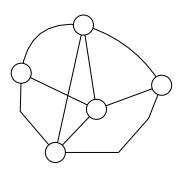

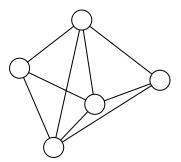

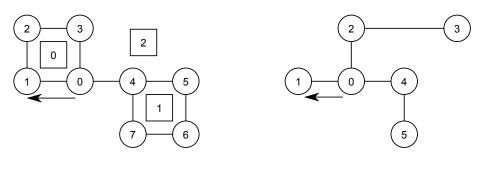

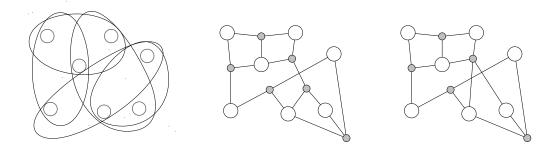

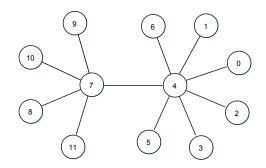

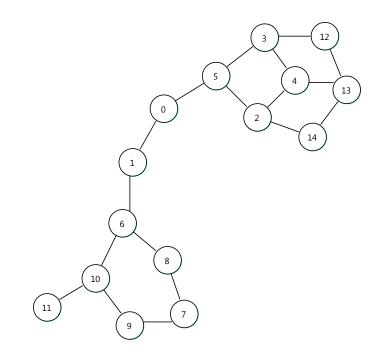

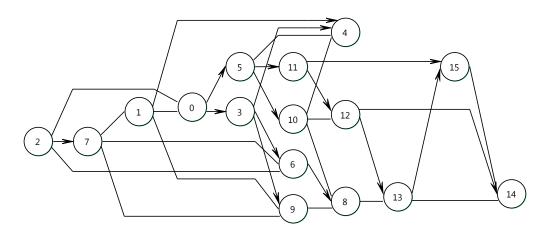

A readable drawing is important. Figure 1.1 shows the same diagram with different layouts. The first one in Figure 1.1a is hard to read because of the many edge crossings, though it is in compact shape. A force-based layout algorithm is applied to the drawing with the result that no crossings remain (see Figure 1.1b). The relations between the elements of the drawing are much clearer, but they need more drawing space. Usually these diagrams are two-dimensional, and they can become large quite fast. The manual maintenance and manual expansion of such diagrams is expensive, hence tools that are able to do the layout automatically are desired.

Different types of drawings require different types of layout algorithms. Each layout algorithm provides different aesthetics criteria. There are general criteria such as edge crossings and total edge lengths, and there are criteria that depend on the user preference and the use case. In this thesis, the considered layout algorithm provides orthogonal graph drawings. Orthogonality is ensured if all the segments of the edges in a graph are drawn horizontally or vertically. These types of drawings are widely used in circuit schematics and in software diagrams

## 1. Introduction

**a.** Result of a database query.

**b.** Same drawing with force-based layout.

Figure 1.1. Different layouts for the same diagram [Mut05].

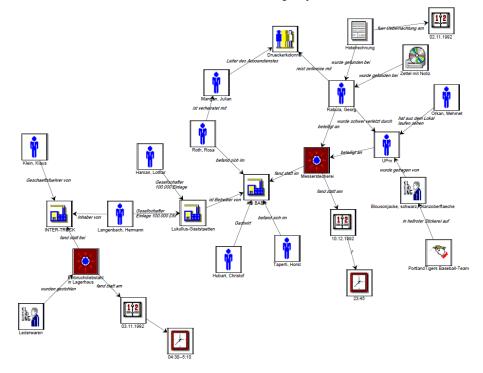

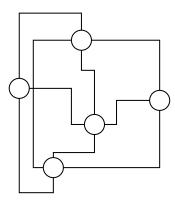

Figure 1.2. Entity-relationship diagram.

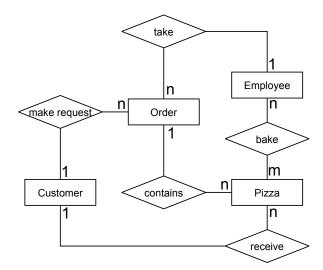

like the Unified Modeling Language (UML) class diagrams or entity-relationship models. Figure 1.2 shows an orthogonal drawing of an entity-relationship model. Every edge segment is bounded by a bend or an endpoint.

Orthogonal drawings can be realized with a basic layout algorithm, namely the Topology-Shape-Metrics (TSM) approach. Roberto Tamassia introduced this algorithm in 1987 [Tam87]. Its task is to compute compact orthogonal grid drawings with few edge crossings and a few number of edge bends.

To do that, firstly, the algorithm calculates a planar embedding of an input graph. If no planar embedding exists dummy nodes are introduced to obtain one. Then, the algorithm computes a bend-minimal and compact orthogonal grid drawing with respect to the input embedding. If it is allowed to change the embedding of the input graph, the problem becomes NP-hard [GT02]. The approach is divided into three parts, namely planarization, orthogonalization, and compaction. This allows a good exchangeability and expandability.

The completion of the implementation of that algorithm in a modeling tool as well as the consideration of extensions are the main contributions of this thesis.

#### 1. Introduction

### 1.1 Related Work

Kiel Integrated Environment for Layout Eclipse Rich Client (KIELER) is an academical research project that improves the graphical model-based design of complex systems with automatic layout [Fuh11]. Miro Spönemann et al. created a framework for the integration of different layout algorithms to support automatic layout for the diagrams modeled in KIELER [SFH09; Fuh+10].

Claußen, Döhring, and Kutschmar worked at the implementation of the TSM algorithm in 2010 [Cla10; Döh10; Kut10]. They realized the planarization part of the algorithm including two different planarity testing techniques. Moreover, Claußen implemented most parts of the orthogonalization phase of the TSM approach. In that context, the authors implemented various shortest path finding algorithms and the creation of flow networks together with a method to solve the minimum cost flow problem. Thus, they created some important foundations for this thesis.

Other related works are documents and workgroups that consider the TSM approach. Basics of orthogonal drawing and the TSM algorithm can be found in various publications of Tamassia et al. [TDBB88; Di +94; Di +99]. Besides these papers the institutes Technische Universität Dortmund, the Friedrich-Schiller-University Jena, the University of Cologne, the University of Sydney, and oreas GmbH developed and still support the Open Graph Drawing Framework (OGDF)<sup>1</sup>, which provides several layout algorithms. In particular, the TSM algorithm as well as a lot of extensions and variations of that are part of its library. Many ideas of their approaches were used in this thesis [Chi+07; GM04; JLM98; Ker07; KM98; MM96]. The OGDF provides a wide range of planarization algorithms. Their algorithms are suitable and efficient in generating and arrangement layouts. Thus, the following question comes up: Why implement an own TSM algorithm? Even if the framework is open, the algorithms of OGDF are written in C++, so that their source-code could not be integrated in the KIELER Layout Algorithms (KLay) which is a Java-based project. The goal is to research new variants and extensions of the different parts of the generic TSM approach. Hence, a new Java-based implementation is essential.

Eiglsperger et al. considered in 2003 the TSM approach with respect to different layout approaches of UML diagrams [EKS03]. In that context he considered mixed upward planarization to allow directed edges in the diagrams. Chimani, Gutwenger, Mutzel, and Wong et al. investigated upward planarization in 2008 as well [Chi+10]. Their approach produces much better results for upward crossing minimization.

<sup>&</sup>lt;sup>1</sup>http://www.ogdf.net/

## 1.2 Contributions

The focus of this work lies on the embedding of the existing parts of the TSM algorithm into a generic architecture and on the completion of the implementation of the algorithm as well as the evaluation and partial implementation of possible extensions.

In that context some changes are done to extend the implementation of the existing planarization and orthogonalization. Additionally, the implementation for finding a suitable external face was considered.

The compaction with all its intermediate processors was implemented to finalize the whole algorithm in order to layout first diagrams. In that context, the compaction phase itself was created. It consists of the creation of a flow network and its solution in order to achieve small edge lengths. Moreover, the technique for the creation of grids and the mapping of the graph elements on these grids were implemented.

An extension of the compaction was the realization of more general input graphs, especially graphs that are not in rectangular shape. A mechanism was introduced that adjusts input graphs with dummy nodes to be in rectangular face. Secondly, a process was considered that subdivides edges with bends into edges with dummy nodes at the positions of the bends. Furthermore, a method was implemented to remove all dummies of the graph correctly in order to ensure the graph represents its original.

In addition, the algorithms were extended to allow cutedges and cutvertices. Furthermore, methods to allow graphs with high-degree nodes are evaluated and two of them are implemented, namely the Giotto approach and the Quod approach. Additional possible extensions of that algorithm were evaluated like interactive planarization and planar drawing alternatives. Besides all that, the handling of directed edges, port-constraints and edge labels are considered. Implementation ideas for handling self-loops and multi-edges were investigated.

## 1.3 Overview

In Chapter 2 basics of graph theory are presented. Furthermore, flow networks are described as well as graph drawing conventions. Different aesthetics criteria of drawings are considered, and the TSM layout approach is presented. The implementation of that algorithm is embedded in the research project KIELER.

#### 1. Introduction

Finally, the general architecture of the layout algorithms implemented in KIELER is presented.

Afterwards the three parts of the TSM algorithm are considered. Firstly, the planarization is presented in Chapter 3. In that context, the planarity testing and the additional edge insertion phase are described. Chapter 4 forms the orthogonalization. Here, Tamassia's algorithm for setting angle- and bend-data to the graph is considered. In that process the creation of a flow network in the context of orthogonalization and its solution is presented. Finally, the step to calculate the external face of the input graph is discussed.

Chapter 5 considers among others the main contributions of the this thesis. First the compaction phase itself is discussed. The creation and the solving of flow networks to minimize the lengths of the graph edges are considered. Additionally, a lot of steps around that phase to allow more general input graphs are discussed. A part of these steps is to bring the input graph in rectangular shape. In that process the general method to transform the internal and external faces of a graph in rectangular shape is investigated. Moreover, the implementation of that method is presented. Additionally, the special case for handling cutvertices and cutedges is presented. After the compaction phase has calculated the relative edge length the technique for adding graph nodes on positions into a grid is shown. Afterwards the removal of the different dummies of the graph is discussed.

The second main chapter forms Chapter 6, which includes the evaluation and the presentation of the implementation of some extensions. Especially the evaluation and implementation of the Giotto approach and the Quod approach to allow graphs with higher degree than four are described. Besides that approach, some methods to draw planar graphs are presented, and the possible realization of the interactive planarization in the implemented algorithm is shown. Furthermore, the finding of an optimal embedding to let the external face be suited is presented. Some additional desired extensions are hyperedges, edge labels and port-constraints which are considered as well. Additionally, the possible implementation of some smaller basic extensions are discussed, such as multi-edges and self-loops.

Finally, a conclusion is given in Chapter 7 to complete the thesis. In that process an evaluation of the different layout algorithms of KLay is presented.

This chapter considers definitions to set the base for the graph drawing environment. The essentials are introduced here bases mainly on [Di +99] and [KW01]. Furthermore, flow networks are introduced. Then, aesthetics criteria of graph drawing are presented, and the TSM approach is discussed. Moreover, the KIELER as a platform for implementing and testing layout algorithms is introduced, which includes an implementation of the TSM algorithm. This chapter ends with the description of the generic architecture for the different layout algorithms used in KIELER with special focus on the TSM algorithm.

## 2.1 Basics of Graph Drawing

**Definition 2.1** (Graph, Subgraph). A graph G = (V, E) consists of a finite set of *vertices* V and a finite set of *edges* E. An edge  $e \in E$  with e = (v, w) represents a pair of nodes where  $v, w \in V$ . e is a denoted as a *self-loop* if v = w. A graph G' = (V', E') is a *subgraph* of G if  $V' \subseteq V$  and  $E' \subseteq E$ .

**Definition 2.2** (Degree). The *degree* of a vertex v, called deg(v), is the number of edges incident to the vertex. Self-loops count twice.

**Definition 2.3** (Directed, Undirected). A graph is *directed* if all pairs of *E* are ordered. v is called *source* and w is called *target* of a directed edge (v, w). If all edges are unordered the graph is called *undirected*. A *mixed graph* contains directed and undirected edges.

**Definition 2.4** (Completeness). An undirected graph *G* is *complete* if every pair of its distinct vertices is connected by an unique edge.

**Definition 2.5** (Bipartiteness). A graph is a *bipartite* if its vertices can be divided into two disjoint sets *U* and *V* such that every edge connects a vertex in *U* to one in *V*; that is, *U* and *V* are each independent sets.

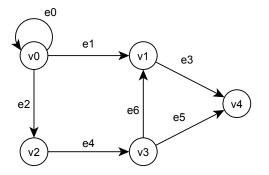

Figure 2.1. Directed graph with self-loop.

**Definition 2.6** (Drawing). A *drawing*  $\Gamma$  of a graph *G* is a mapping of each vertex *v* to a distinct point  $\Gamma(v)$  and each edge (v, w) to a simple open Jordan curve with endpoints  $\Gamma(v)$  and  $\Gamma(w)$ . A directed edge is often drawn with an arrow.

Figure 2.1 shows a drawing of a directed graph G = (V, E) with the described definitions where  $V = \{v_0, v_1, v_2, v_3, v_4\}$ ,  $E = \{e_0, e_1, e_2, e_3, e_4\}$ . For example,  $v_0$  is source and  $v_1$  is target of  $e_1$ .  $e_0 = (v_0, v_0)$  is a self-loop on  $v_0$  and e.g.,  $deg(v_0) = 4$  and  $deg(v_1) = 3$ .

**Definition 2.7** (Path). A (directed) *path* in a (directed) graph G = (V, E) is a sequence  $(v_0, v_1, ..., v_n)$  of distinct vertices of G with  $(v_i, v_{i+1}) \in E$  for  $i \in 0, ..., n-1$ . A path is a (directed) *cycle* if  $(v_n, v_1) \in E$ . A directed graph is *acyclic* if it has no directed cycles.

**a.** Simply connected edge.

**b.** Subdivision of the edge of Figure 2.2a.

Figure 2.2. Subdivision example.

In the following, an important term of the context of this thesis is introduced, the *planarity*.

**Definition 2.8** (Planarity). A drawing  $\Gamma$  is *planar* if no two distinct edges cross. A graph is planar if there is a planar drawing of *G*.

A graph is called to be maximal planar if it is planar but adding any edge would destroy that property.

**Definition 2.9** (Subdivision). A *subdivision* of a graph *G* is a graph resulting from the subdivision of edges in *G*. The subdivision of an edge e = (v, w) yields a graph containing one new vertex *s* with a set of edges replacing *e* with two new edges,  $e_1 = (v, s)$  and  $e_2 = (s, w)$ .

Figure 2.2 illustrates an example for a subdivision. The edge e = (v, w) can be subdivided into two edges,  $e_1 = (v, s)$  and  $e_2 = (s, w)$ , connecting to a new vertex *s*.

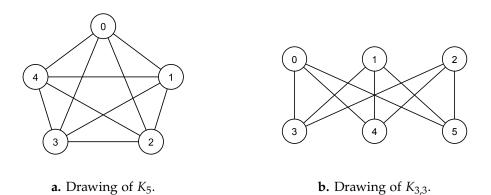

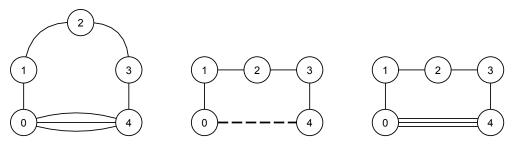

Figure 2.3. Drawings of the smallest non-planar graphs.

Figure 2.3 shows drawings of two special graphs, the  $K_5$  and the  $K_{3,3}$ .  $K_5$  is a complete graph with 5 vertices.  $K_{3,3}$  is a complete bipartite graph, which is divided into two sets. Each set consists of three elements. Both graphs are not planar, since there is no representation of that graph that is planar. They are even the smallest graphs that are not planar.

**Theorem 2.10** (Kuratowski<sup>1</sup>). A finite graph is planar if and only if it does not contain a subgraph that is a subdivision of  $K_5$  and  $K_{3,3}$ .

**Definition 2.11** (Embedding, Equivalent). A (planar) *embedding* of G is an equivalence class of drawings that is defined by the circular order of the adjacent edges of each vertex v of a graph. If each vertex v of G has drawings with same circular sequence of adjacent edges around v for two (planar) embeddings, they are called to be *equivalent*.

**a.** Non-planar drawing.

**b.** Planar drawing of Fig- **c.** The dual graph of the ure 2.4a with another embed- drawing of Figure 2.4b. ding.

Figure 2.4. Different representations of a graph.

An embedded planar graph is usually called *plane* graph. Figure 2.4a and Figure 2.4b present two different drawings for the same graph. The drawing of Figure 2.4a is not planar since the edges (0,1) and (2,5) cross. Changing the embedding of that graph leads to a planar drawing as shown in Figure 2.4b. The example graph is planar since there is at least one planar drawing.

**Definition 2.12** (Face). A planar drawing partitions the plane into regions called *faces*. The unbounded face is called *external face*.

**Definition 2.13** (Dual Graph). The *dual graph*  $G^*$  of an embedding of a planar graph G has a vertex for each face of G and an edge (f, g) connecting every two faces f and g that are adjacent by an edge in G.

Figure 2.4c shows the planar drawing of Figure 2.4b and its dual graph. The five faces of the original plane are the vertices of  $G^*$  that are connected with dashed lines. A graph can be divided into different levels of connectivity.

**Definition 2.14** (Connectivity). A graph is *connected* if there is a path between every vertex in that graph. A *cutvertex* is a node that divides the graph into two components if it is removed. A *biconnected* graph contains no cutvertices.

<sup>&</sup>lt;sup>1</sup>http://en.wikipedia.org/wiki/Planar\_graph

#### 2.1. Basics of Graph Drawing

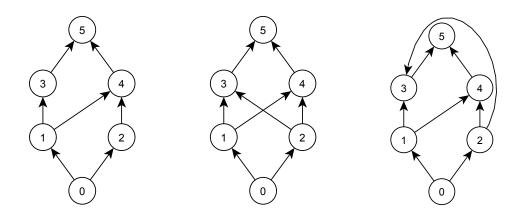

**a.** Upward planar drawing. **b.** Upward non-planar drawing. **c.** Non-upward planar drawing.

Figure 2.5. Different drawings illustrating upward planarity.

**Definition 2.15** (ST-Graph). A *st-graph* is an acyclic directed graph with a single source *s* and a single sink *t* with following properties:

- $\triangleright$  Given a topological numbering of *G*, every directed path of *G* visits vertices with increasing numbers.

- $\triangleright$  For every vertex *v* of *G*, there is a simple directed path from *s* to *t* containing *v*.

**Definition 2.16** (Planar ST-Graph). A *planar st-graph* is a st-graph which is planar and embedded with vertices *s* and *t* on the boundary of the external face.

**Definition 2.17** ((Mixed) Upward Drawing). A drawing of a directed / mixed graph is called (mixed) upward drawing if each (directed) edge is represented by a curve monotonically increasing in the vertical direction.

**Definition 2.18** ((Mixed) Upward Planarity). A (*mixed*) *upward planar drawing* of a mixed / directed graph is a (mixed) upward drawing with no edge crossing. A graph *G* is called (mixed) upward planar if it has a planar (mixed) upward drawing.

Figure 2.5 shows different drawings to make the definition of the upward planarity clearer. Figure 2.5a illustrates a drawing that is upward planar, while Figure 2.5b is not planar since the edges (1, 4) and (2, 3) cross. This drawing can

be adjusted to be planar as seen in Figure 2.5c, but then it looses the upwardness property.

#### 2.1.1 Flow Networks

In the following, the flow network is introduced. It leads to the minimum cost flow problem that is needed in the context of the orthogonalization and the compaction. A complete overview about network flows and especially solving minimum cost flow problems is presented by Ahuja et al. [AMO93].

**Definition 2.19** (Flow Network). A *flow network*  $\mathfrak{N} = (N, A)$  is a directed graph.

- ▷ Each *source node* has a production and respectively each *sink node* has a consumption.

- ▷ The sum of produced and consumed units of every node in the whole drawing is equal.

- $\triangleright$  An arc (*v*, *w*) contains the following properties:

- 1. A lower bound  $b_{vw} \in \mathbb{R}$ .

- 2. A capacity  $u_{vw} \in \mathbb{R}$ .

- 3. A cost  $c_{vw} \in \mathbb{R}$ .

For a better distinction to the original graph *G* we call vertices of  $\mathfrak{N}$  *nodes* and edges of  $\mathfrak{N}$  *arcs*.

**Definition 2.20** (Feasible Flow). A *feasible flow* x is a function  $x : A \to \mathbb{R}$  with following properties:

- $\triangleright$  Capacity:  $b_{vw} \leq x_{vw} \leq u_{vw} \forall (v, w) \in A$

- ▷ Mass balance:  $b(v) = \sum_{w:(v,w)\in A} x_{vw} \sum_{w:(w,v)\in A} x_{wv} \forall v \in N$

Each node of  $v \in N$  is associated with a number b(v) denoted *supply value*, such that

$\succ$  if  $b(v) > 0 \rightarrow v$  is a supply node,

$\triangleright$  if  $b(v) = 0 \rightarrow v$  is a transport node, and

$\triangleright$  if  $b(v) < 0 \rightarrow v$  is a demand node.

#### 2.1. Basics of Graph Drawing

The first property of the feasible flow definition states that the flow of an edge (v, w) cannot be less than the lower bound and cannot top the capacity border  $u_{vw}$ . The second property states that the subtraction of the total supply of a node minus the total demand of the node is b(v) (supply / transport / demand value) of this node. For each non-source node and non-target node the amounts of the flow of the incoming arcs and of the outgoing arcs have to be equal (flow conservation).

Next, the minimum cost flow problem is introduced. Such a calculation is one of the fundamental problems in the network flow theory and has been studied extensively in the past.

**Definition 2.21.** The *cost* of flow *x* in  $\mathfrak{N}$  is defined as  $c(x) = \sum_{(v,w) \in A} c_{vw} \cdot x_{vw}$ .

**Definition 2.22** (Minimum Cost Flow Problem). Minimize c(x) for a given flow network  $\mathfrak{N}$  with source  $s \in N$  and target  $t \in N$ , with required flow d such that the following constraints are satisfied:

- $\triangleright$  Capacity constraints:  $x_{vw} \leq u_{vw}$

- $\succ$  Required flow:  $\sum_{(v,w)\in A} x_{vw} = d$

- $\triangleright$  Skew symmetry:  $x_{vw} = -x_{wv}$

- $\triangleright$  Flow conservation:  $\sum_{(v,w)\in A} x_{vw} = 0$ , with  $v \neq s$  and  $w \neq t$

To work with minimum cost flow one has to assume that every node is reachable by another node and that there is at least one solution of the Minimum Cost Flow (MCF) problem.

#### 2.1.2 Drawing Conventions

As seen above, a graph can be drawn in many different ways. Thus, the concept of drawing conventions is introduced which defines basic rules for drawings that have to be satisfied to be admissible [Di +99].

- ▷ *Polyline Drawing:* Each edge is drawn as a polygonal chain.

- ▷ Straight-line Drawing: Edges are drawn as straight line connections between two vertices.

a. Polyline drawing.

**b.** Straight-line drawing.

c. Orthogonal drawing.

d. Grid drawing.

Figure 2.6. Different drawings showing drawing conventions.

- ▷ *Orthogonal Drawing:* Edges are polygonal chains that only consists of horizontal and vertical segments. A segment is bounded by a vertex or a bend of that edge.

- ▷ *Grid Drawing:* Each vertex, bend, and crossing of the graph get an integer coordinate on a grid.

#### 2.1. Basics of Graph Drawing

#### 2.1.3 Aesthetics Criteria

A good layout can be a picture worth a thousand words; a poor layout can confuse or mislead. Graphs are used to represent information and structure in various areas of the software engineering. To achieve the readability of the information presented, properties of a drawing are specified, the so called *aesthetics criteria* [Di +99].

- ▷ Minimization of edge crossings; Ideally, there is a planar drawing so that there is no edge crossing, but not every graph admits one. If there is no planar embedding the goal is to find a drawing with a minimal total number of crossings between edges.

- Minimization of the drawing area; It is essential in practical visualization systems to save screen space. Furthermore, it is relevant if one cannot arbitrarily scale the graph down.

- Minimization of the edge length; This criterion is divided into three similar minimization concepts:

- 1. Total edge length: Minimize the sum of the edge lengths.

- 2. *Maximum edge length:* Minimize the maximum edge lengths.

- 3. *Uniform edge length:* Minimize the variance of the edge lengths.

- ▷ Minimization of the bend number; This criterion contains three concepts likewise the criterion for the edge length:

- 1. *Total bend number:* Minimize the total number of bends along the edges.

- 2. Maximum bend number: Minimize the maximum number of bends on an edge.

- 3. *Uniform bend number:* Minimize the variance of the number of bends on an edge.

- ▷ Minimization of the aspect ratio; Aspect ratio is defined as the ratio of the length of the longest side to the length of the shortest side of the smallest rectangle with horizontal and vertical side covering the drawing. Drawings with high aspect ratio may not be conveniently placed on a screen, even if it has small area.

In the following, the TSM approach after Tamassia is described. This algorithm is suited for orthogonal grid drawings and hence useful in industrial plans like data flow modelings or in UML class diagrams.

## 2.2 Topology-Shape-Metrics Approach

Roberto Tamassia et al. introduced the TSM algorithm first in 1987 and in 1988, respectively [Tam87; TDBB88]. The idea behind that approach is that an orthogonal drawing can be described by three properties, defined in the terms topology, shape and metrics that are used as follows [Di +99]:

- ▷ *Topology:* Two orthogonal drawings are topologically equal if one can be obtained from the other by continuous deformation that does not alter the sequence of edges contouring the faces of the drawing.

- ▷ Shape: Two orthogonal drawings have the same shape if, firstly, they have the same topology and secondly, one can be obtained from the other by modifying only the length of edges without changing their angles.

- ▷ *Metrics:* Two orthogonal drawings have the same metrics if they are congruent, up to a translation and/or rotation.

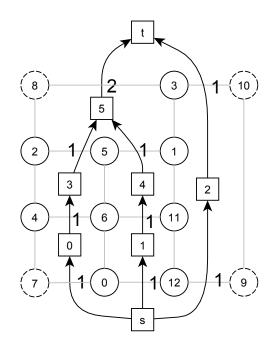

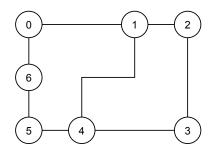

According to these three properties the TSM algorithm is divided into the following three steps:

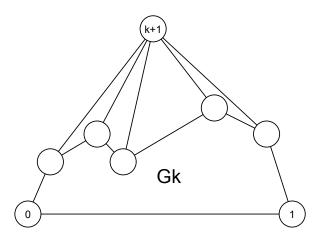

- 1. *Planarization:* This step determines the topology of the drawing which is described by a planar embedding. This step reduces the number of edge crossings as much as possible. One way is to find an embedding that is planar, if there is one. Otherwise, a maximal planar subgraph is built and all violating edges are removed, such that the result is planar. In a second step these violating edges are added to the graph again by inserting one dummy vertex for each edge crossing.

- 2. *Orthogonalization:* This step determines the shape of the plane by calculating the angles and the bends in the drawing. The goal of this step is to minimize the number of bends without changing the topology. This is done by creating a network flow model that has to be minimized to get the angles of edges around a node and the correct placement of bend-points.

- 3. *Compaction:* Final coordinates of the vertices and edge bends are determined, and additionally, the previously added dummies are removed. In this step the main goal is to minimize the drawing area, by minimizing the length of the edges.

#### 2.2. Topology-Shape-Metrics Approach

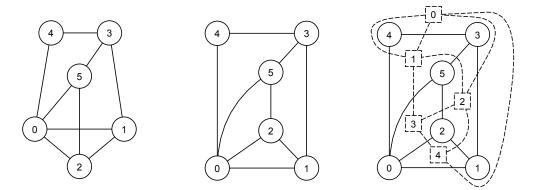

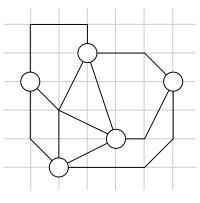

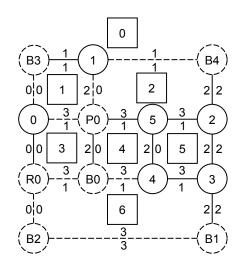

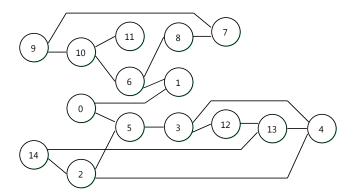

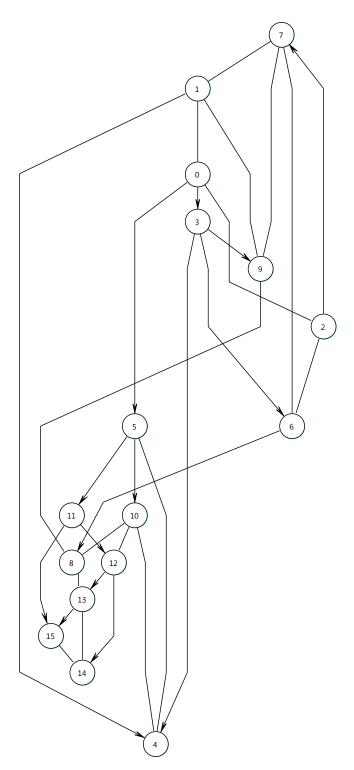

**a.** Result of planarization.**b.** Result of orthogonaliza-**c.** Result of compaction.

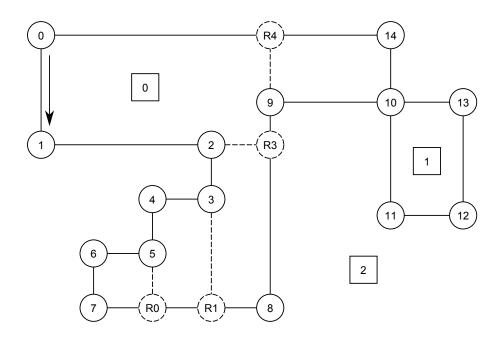

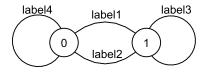

Figure 2.7. Steps of the TSM approach.

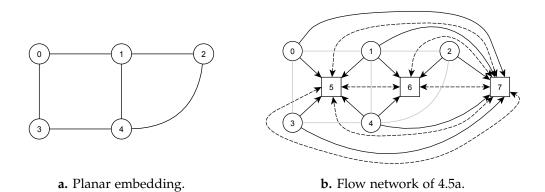

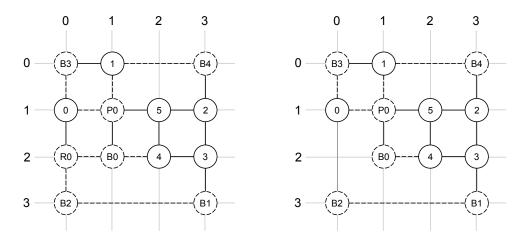

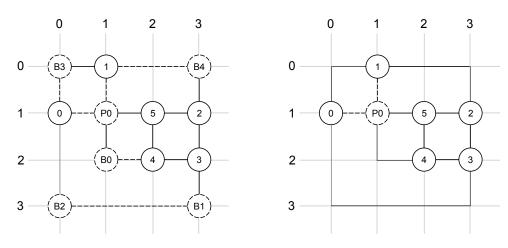

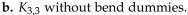

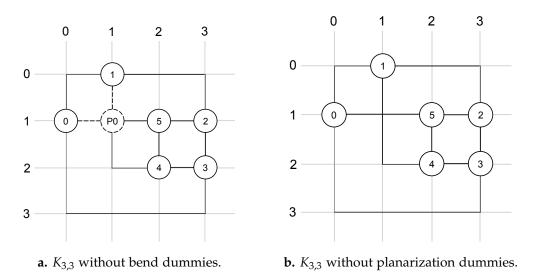

The result of processing these three steps on a graph is an orthogonal shape with few edge crossings and with small edge length respectively small area space. Figure 2.7 shows the results of every step of the algorithm with an example. The considered example is the  $K_{3,3}$  graph of Figure 2.3b that can not be drawn planar, and its concrete structure is  $(\{0, 1, 2, 3, 4, 5\}, \{(0, 1), (0, 3), (0, 5), (1, 2), (1, 4), (2, 3), (2, 5), (3, 4), (4, 5)\})$ . In the first phase a maximal planar subgraph is calculated, and the remaining violating edges are removed, here edge (1, 4). In a second phase, still part of the planarization, a dummy node is inserted at the place the edges would cross, and the removed violating edges are inserted again, such that the crossing edge (0, 5) and the violating edge (1, 4) are connected to the new dummy node. The result is a planar embedding of the original graph which contains dummy nodes that avoid edge crossings, see Figure 2.7a.

Such a plane is needed to process the orthogonalization phase. The result of this phase is presented in Figure 2.7b, that is a representation with angle-data around a node and minimum bend-data for each edge. Orthogonality is ensured because only multiples of 90° are assigned as angles and each edge consists of segments that are only horizontal or vertical. The resulting representation contains no real coordinates, it defines only the shape.

In order to set such coordinates to the graph elements the final compaction phase is used. This phase makes the drawing as compact as possible by minimizing the edge length. Additionally, the planar dummy nodes are removed and the edges are connected with their original source and original target nodes. The result, shown in Figure 2.7c, is an orthogonal and compact drawing of the given graph with few edge crossings.

The order of the steps taken represent an order of importance of aesthetics criteria as well. The planarization is the first step, such that the edge crossing minimization is the most important criterion. Then minimizing the number of bends with the orthogonalization is the second most important criterion, and least important is the minimization of the drawing area that is determined by the compaction. The result is that each phase affects the aesthetics criteria of its successor phase.

In addition, a drawing could consists of less bend-points if the orthogonalization would be processed first, and respectively, a drawing could be drawn with less space if the compaction would be processed before. Such a phase swapping is not possible, since each successor step requires the changed graph structure as input, as done by the preceding step. Without the preceding steps each phase would form a NP-hard problem.

An implementation of Tamassia's approach is part of the layout library of the following project.

## 2.3 Kiel Integrated Environment for Layout Eclipse Rich Client

KIELER<sup>2</sup> is an academical research project that aims to enhance the graphical modelbased design of complex systems [Fuh11]. The main idea is to consistently employ automatic layout in all graphical components of the diagrams within the modeling environment. This leads to new possibilities for diagram editing, browsing, and dynamic visualizations. This project continues the Kiel Integrated Environment for Layout (KIEL) project. While KIEL concentrates on a single modeling language, namely *Statecharts*, KIELER aims to integrate different modeling languages into the rich client platform Eclipse<sup>3</sup>. KIELER is licensed under the Eclipse Public License<sup>4</sup>,

<sup>&</sup>lt;sup>2</sup>http://www.informatik.uni-kiel.de/rtsys/kieler/

<sup>&</sup>lt;sup>3</sup>http://www.eclipse.org

<sup>&</sup>lt;sup>4</sup>http://www.eclipse.org/legal/epl-v10.html

#### 2.3. Kiel Integrated Environment for Layout Eclipse Rich Client

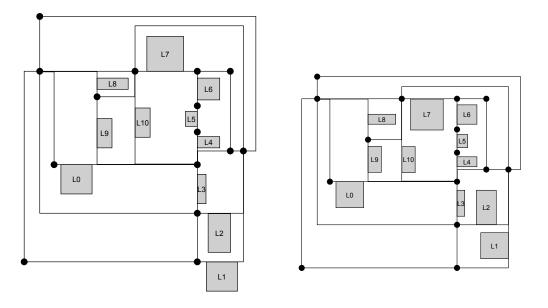

Figure 2.8. Overview of KIML structure [Fuh11].

an open source software license.

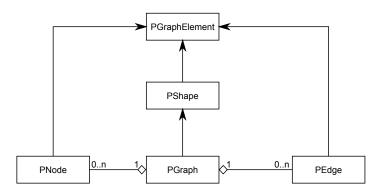

One of the main concepts of KIELER is to offer automatically generated layouts, to support the creation and maintenance of diagrams as well as modern dynamic visualization techniques. Thus, the user of KIELER is free from so-called *enabling steps*, which are things that have to be done to prepare the model for changes the user actually wants to make. Normally, these are things like making space for nodes by moving nodes of the diagram around, or taking care of the edge routing and so on. The KLay project provides Java-based implementations of layout algorithms for the automatic layout feature that can be used with any graphical editor. The core component of bridging the layout algorithms of KLay and graph editors is the KIELER Infrastructure for Meta Layout (KIML). KIML provides a bridge that puts the content of the editor in a data structure that can be understood by a layout algorithm. A brief overview of KIML is presented in the following subsection.

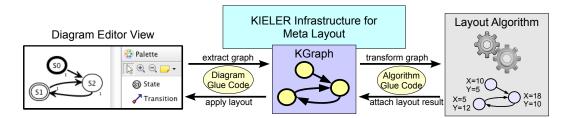

#### 2.3.1 **KIELER Infrastructure for Meta Layout**

Apart from layout algorithms themselves, the topic of automatic layout consists of the problem of getting the diagram in a format understandable by the layout algorithm and applying the resulting layout back to the diagram. KIML solves such problems as generically as possible, such that many algorithms can be used for many diagram editors. Furthermore, KIML allows layout algorithms to offer layout options for the user that affect the resulting layout, for instance, setting a minimum distance between the nodes. Figure 2.8 illustrates the structure of KIML.

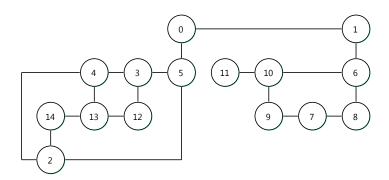

Figure 2.9. KLay architecture overview [Sch11].

A lot of existing layout algorithms are provided, libraries like Graphviz [Ell+02] and OGDF [Chi+07]. On the other hand the library of KLay includes implementations of own layout algorithms that are

▷ a force-based algorithm (*KLay Force*),

▷ a layerd-based algorithm (KLay Layered) [Spö09; Sch11; Car12], and

▷ the TSM algorithm (*KLay Planar*) [Kut10; Cla10]

which is considered in this thesis. The implementations of KLay base on a special architecture that is presented in the following section.

### 2.4 KLay Architecture

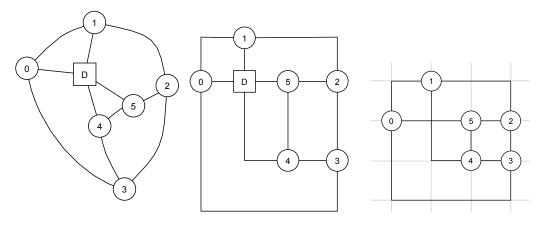

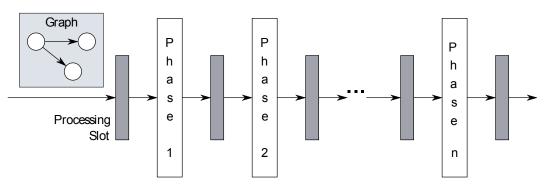

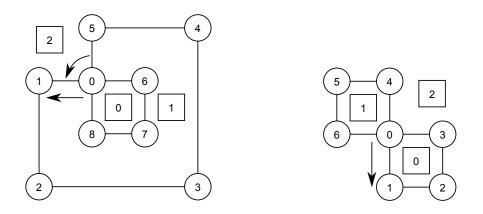

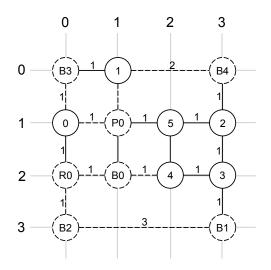

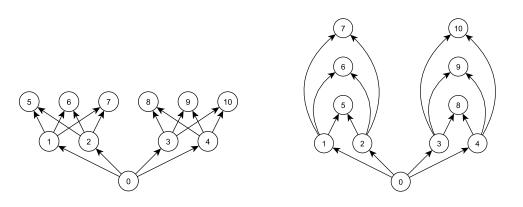

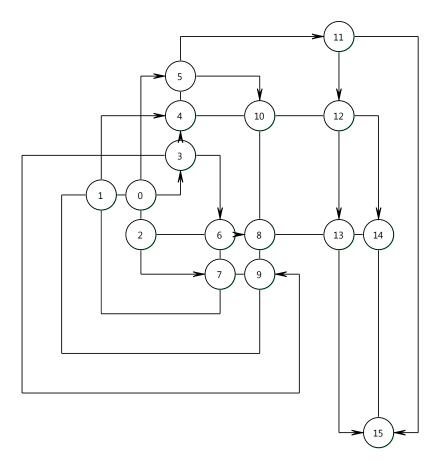

This architecture was presented first by Christoph Daniel Schulze [Sch11] in the KLay Layered implementation (see Figure 2.9). It is divided into main phases and several small intermediate processors.

A phase is basically an own part of the algorithm like the orthogonalization in the KLay Planar algorithm. There are empty slots before and after a phase that can be filled with intermediate processors, which solve tasks for each phase like bringing the data structure in readable form or cleaning up the data structure. This concept provides a high degree of exchangeability and extensibility, since each phase can be exchanged with another variant or can be extended with new features by changing the phase itself or introducing a new intermediate processor.

#### 2.4. KLay Architecture

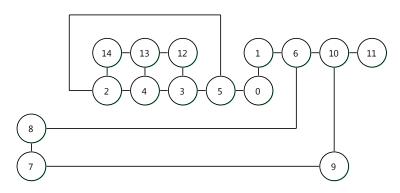

Figure 2.10. KLay Planar architecture.

In addition, the code is better readable since the complex layout algorithm is divided into smaller parts (phases), which taken by itself are easier to understand than the whole algorithm. Hence, the whole algorithm can be maintained easier.

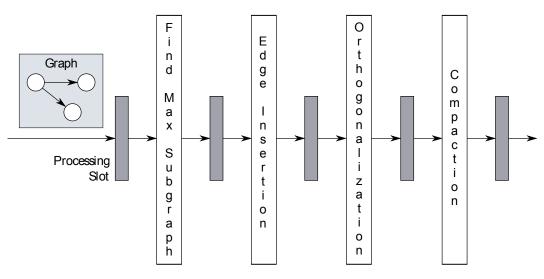

## 2.4.1 KLay Planar Architecture

The phases and intermediate processors concept is suitable for the implementation of the TSM algorithm because the TSM algorithm is also divided into different parts. The planarization step consists of two parts with own context and own functionality, building the maximal planar subgraph and the additional edge reinsertion. Both pieces are part of the planarization algorithm itself and hence, they are handled as phases. Additionally, the orthogonalization and the compaction form own sections of the algorithm, thus they are both handled as single phases in the implementation.

The graph structure has to be adjusted between these phases, e.g., the faces of a planar embedding are computed before processing the orthogonalization, or a grid drawing can be calculated for the result of the compaction, for a more comfortable and efficient processing on the drawing. For such tasks intermediate processors are created and are added to the corresponding slots between the phases.

In the following chapters different phases of the TSM algorithm and intermediate processors as well as their realizations are discussed.

# Planarization

The task of planarization is to find a planar embedding of a given graph g. If there is such a plane graph we are finished. Otherwise a planar subgraph of g is taken. In a second step the missing, violating edges are added again to the graph with a dummy node for every crossing such that the resulting graph is planar, but contains some dummy nodes.

The dummy nodes do not distort the subsequent phases of the TSM algorithm and can be kept until the compaction phase is finished. After this last phase of the algorithm the planarization dummies are removed. Additionally, the edges are connected back to its original vertices.

This chapter starts off with an introduction of an algorithm for planarity testing. in addition, the strategy for inserting dummy nodes is described.

# 3.1 Planarity Testing

The presented technique bases on the work of Ole Claußen, who implemented the algorithm of Boyer and Myrvold [Cla10]. This algorithm checks a graph for planarity, and if the graph is not planar, it is able to find a planar subgraph of the given graph in linear time to the number of vertices [BM04]. The calculated planar representation contains a fixed order of edges on each vertex in counter-clockwise direction and therefore defines a topology for the given graph.

The general computation of planar subgraph with minimum edge crossings is known to be NP-hard [Yan78]. Among others, the reason is that a given graph can have exponentially many planar embeddings. Thus, testing algorithms compute a *maximal* planar subgraph, such that adding any missing edge of the subgraph would break the planarity property. Hopcroft and Tarjan presented the first linear time planarity testing algorithm, and several extensions and improvements have emerged until today [HT74; BM04; MM96; JLM98].

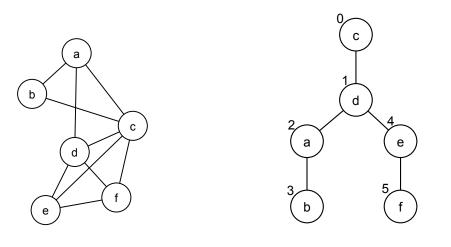

Boyer and Myrvold's algorithm first calculates a Depth First Search (DFS) on the given graph, which results in a spanning tree, generally known as the DFS-tree.

## 3. Planarization

Figure 3.1. Creation of a DFS-tree.

**Definition 3.1** (DFS-Tree). A DFS-tree of a graph is a spanning tree emerged by a DFS. Nodes that have been visited before are not visited again. Each node is ordered by an index, called DFS Index (DFI).

Since visited nodes are not visited again not all edges of a given graph might be part of the tree. It is immediate that every DFS-tree is planar. These edges are called *back-edges*. In the following, the algorithm of Boyer and Myrvold is described, which is implemented in KLay Planar. Listing 3.1 illustrates the steps of that algorithm.

Listing 3.1. Algorithm of Boyer and Myrvold.

```

Procedure(g : Graph){

calculate a DFS-tree;

2

order its nodes according DFI (v_0, v_1, ..., v_n)

3

for (v_i : v_n, ..., v_1, v_0)

4

embed v_i planar, together with all back-edges (v_i, v_i), j > j;

if (embedding of a back-edge is not possible) {

6

return g is not planar;

7

8

ļ

Q

}

return g is planar;

10

11

}

```

a. Back-edge insertion.

**b.** Swapping of the wrong back-edge of Figure 3.2a.

Figure 3.2. Back-edge insertion.

First, an arbitrary DFS-tree is calculated with an arbitrary start node, such that each node can be identified by a DFI. Then, the nodes of the tree are processed in the opposite order in which they have been added. Thus, the graph rebuilding is started with the leaves of the DFS-tree, and the graph is processed upward to the root. In that process all back-edges are planar embedded. With every cycle of the algorithm, the invariant ensures that nodes that are involved in later embeddings are part of the external face. To ensure this invariant there is a possibility that the biconnected components need to be turned around prior to their embedding. If an embedding fails, meaning there are crossings in the tree, the given graph g is not planar. If all edge embeddings are complete, it is a planar embedding of g.

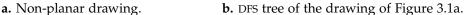

An example for this algorithm can be seen in Figure 3.1. The graph of the drawing of Figure 3.1a is checked to be planar. The first step is to create the DFS-tree with arbitrary root, here c (see Figure 3.1b). Its node list is (c, d, a, b, e, f). The DFI of each node is labeled with a small number next to the node.

Afterwards, the back-edges are reinserted to the graph (see Figure 3.2). A problem exists at the embedding of (c, f). Hence, the embeddings of f are swapped, such that the counter-clockwise order of the edges is changed and the problem is solved. This is illustrated with the blue non-crossing edge in Figure 3.2b.

## 3. Planarization

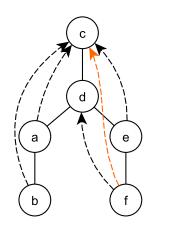

Figure 3.3. Planar embedding of Figure 3.1a.

Since all back-edges are embedded correctly, the graph is planar, hence the embedding can be used to do the next phases of the TSM algorithm.

A more detailed description of that algorithm is presented in the thesis of Ole Claussen [Cla10]. The example graph of Figure 3.3 is planar. If a given graph is not planar, the algorithm calculates an embedding of a planar subgraph and a set of violating edges. As described before, each violating edge is inserted again by adding a dummy node to the position where the edges would cross. This process is described in the following section.

# **3.2 Edge Insertion**

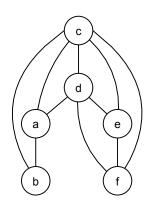

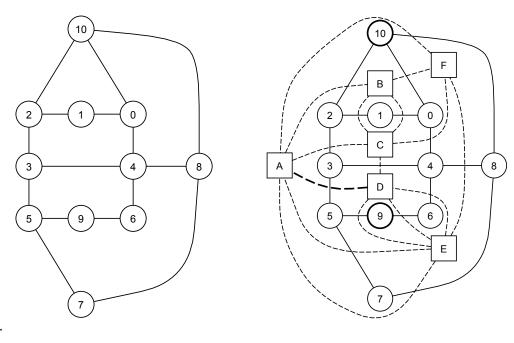

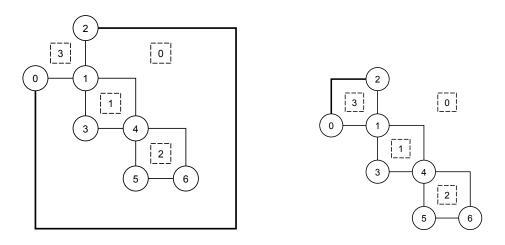

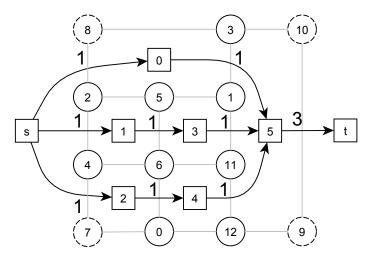

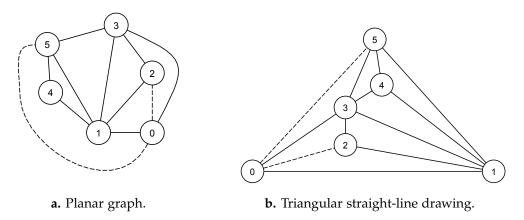

The task of this algorithm is to embed violating edges back into the planar graph, while creating a minimum number of dummy vertices. This is done by calculating a path for the new edge that crosses a minimum number of faces. The shortest edge path in the dual graph corresponds to this path.

The algorithm to embed the remaining edges (v, w) is as follows. First, the dual graph  $G^*$  of the input graph G is processed. Then, Dijkstra's algorithm is used to calculate the shortest path in  $G^*$  for every face adjacent to v and every face adjacent to w. Afterwards, the edge (v, w) is added to the graph along this path. In that process for every edge in  $G^*$  a dummy vertex is inserted in G. Then, this dummy vertex is connected with edges, crossing the involved faces to avoid edge crossings between these edges and the inserted edge (v, w).

### 3.2. Edge Insertion

**a.** Example of a planar embedding. **b.** Dual graph of Figure 3.4a.

Figure 3.4. Edge insertion example.

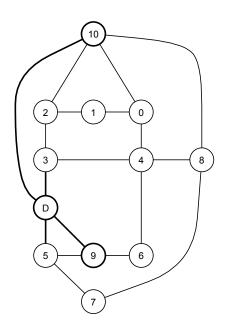

An example for the described algorithm is presented in Figure 3.4. It is assumed that an edge (9, 10) is desired to be inserted into the embedding of Figure 3.4a. The dual graph of the embedding is calculated, which is illustrated in Figure 3.4b. Then, the source of the path would be  $s \in \{D, E\}$  and the target would be  $t \in \{A, B, F\}$ . A shortest path, calculated by Dijkstra's algorithm, would be (D, A), such that the edge (9, 10) would be placed along that path. The edge (3, 5) is adjacent to the faces *A* and *D*. To avoid the crossing of edge (3, 5) and (9, 10), a dummy node is inserted to subdivide the two edges, as in Figure 3.5.

The determination of the faces of an embedding is assumed in the previously described algorithm. This process is explained in the following section.

# 3.2.1 Face Calculation

Christian Kutschmar implemented a method to determine the faces of a planar embedding [Kut10]. The aim of that processor is to walk along the edges. In that

# 3. Planarization

Figure 3.5. Result of the edge insertion of Figure 3.4.

process the adjacent faces of each edge in the planar embedding are calculated. The correct behavior is ensured since the edges of a planar embedding around a vertex are ordered counter-clockwise (see Section 4.2). Hence, each successor edge, whether clockwise (last counter-clockwise) or counter-clockwise, of an edge at a vertex can be calculated uniquely.

Figure 3.6. Simple connected graph example.

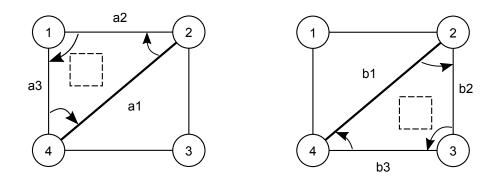

The algorithm starts by checking all edges whether the left or right face of that edge is unknown. If the left face of the edge is unknown a circular walk-through is

## 3.2. Edge Insertion

triggered, which can be seen in Figure 3.7a. Each found edge is added to the face until the start node is reached. The resulting face of the example consists of the edges  $a_1$ ,  $a_2$ , and  $a_3$ . Respectively, for an unknown face on the right hand side of an edge a walk-through in counter-clockwise order is started which is presented in Figure 3.7. The resulting face in the example contains the edges  $b_1$ ,  $b_2$ , and  $b_3$ .

Listing 3.2. A snippet of the face calculation.

```

Procedure(g : Graph)

1

{

2

for (e \in E) {

3

if left face of e is unknown then

create new face f

4

set left face of e = f

5

set n_0 = start node of e

6

set n_1 = n_0

7

set e_0 = e

8

set e_1 = e

9

10

. . .

11

do {

add f to e_1 and vice versa

set n_1 = other adjacent node of e_1

13

set e_1 = next clockwise edge of n_1

14

} while n_1 \neq n_0 or e_1 \neq e_0

15

16

. . .

17

1

}

18

```

## 3. Planarization

Kutschmar's code works only for biconnected graphs, but not for all simple connected graphs. His code goes clockwise around the adjacent faces until the start node is reached again. However, a tree as in Figure 3.6 requires more time passing a node, such that the break condition of the do-while loop does not work for this case and has to be extended, which is a contribution of this thesis.

Even if the edges are passed until the current edge is equal to the starting edge, it would lead to the same result. For instance, let  $e_1$  be the start edge in the tree example and the algorithm passes the other edges in clockwise direction, then the next edge again would be  $e_1$  and the loop would break.

To solve this problem the break condition of the do-while loop is adjusted in a way that the start node has to be equal to the current node and the start edge has to be equal to the current edge to break the loop (see Listing 3.2). The resulting walk-through around a face passes the edges until the start edge and start node are reached. Now trees are processed correctly.

# Orthogonalization

As mentioned before, the orthogonalization works on a planar embedding produced by the planarization step and changes the shape of the graph. The result of that step is an orthogonal representation including angle- and bend-data. This chapter bases on the approach of Tamassia [Di +99].

For a start, some preliminaries are presented to extended the definitions of the flow network context. Furthermore, the orthogonalization phase, bases on Tamassia's consideration, is discussed. In that context the technique for minimizing the number of bends in the flow model is considered, and the final mapping of that result on the original graphs elements is briefly described. Additionally, the intermediate processors FaceDetermination and the ExternalFaceProcessor are discussed.

Table 4.1. The architecture of the orthogonalization.

| Тур            | Name                      | Description                                  |

|----------------|---------------------------|----------------------------------------------|

| Preprocessing  | FaceDetermination         | Determining the faces of a planar embedding. |

|                | ExternalFaceProcessor     | Choice of an external face.                  |

| Phase          | TamassiaOrthogonalization | Orthogonalization of TSM algorithm.          |

| Postprocessing | -                         | ~                                            |

# 4.1 Preliminaries

In Section 2.1.1 the flow network was introduced. In that context the MCF problem is defined, which has to be solved to set angles to vertices and bends to edges. The established algorithms to solve the MCF problem take the so called *residual network* into account.

#### 4. Orthogonalization

**a.** Example of an flow network with arc labeling  $x_{vw}$ , cap(v, w), cost(v, w). **b.** Residual network of Figure 4.1a with arc labeling  $r_{vw}$  and cost(w, v).

Figure 4.1. Flow network example with its corresponding residual network.

**Definition 4.1** (Residual Network). In the *residual network* G(x) with flow x each arc  $(v, w) \in A$  is replaced by two arcs (v, w) and (w, v) with the following properties:

ightarrow Arc (v, w) has costs  $c_{vw}$  and a residual capacity  $r_{vw} = c_{vw} - x_{vw}$ .

ightarrow Arc (w, v) has costs  $c_{wv} = -c_{vw}$  and a residual capacity  $r_{wv} = x_{vw}$ .

Furthermore, arcs with a residual capacity of zero are removed so that the residual network consists only of arcs with positive residual capacity.

Figure 4.1b shows the residual network of the flow network of Figure 4.1a. Arc (a, b) is split into two edges (a, b) and (b, a). Two of three possible units of flow run from node a to node b. Thus, the residual capacity is 1 and the edge costs of arc (a, b) remain consistent. Arc (b, a) of the residual network has a residual capacity of the original flow naming 2 and negative costs. Both edges are accepted in the residual network. In addition, arc (a, c) of the flow network has only the edge (a, c) in the residual network since the flow is zero. Furthermore, arc (b, c) of the flow network has only a back-edge in the residual network because the residual capacity is zero.

**Definition 4.2** (Reduced Cost). For each node  $i \in N$  the number  $\pi_i$  is the *potential* of node *i*. The *reduced cost*  $c_{ij}^{\pi}$  of an edge  $(i, j) \in E$  is defined as  $c_{ij}^{\pi} = c_{ij} + \pi_i - \pi_j$ .

**Theorem 4.3** (Reduced Cost Optimality). A feasible flow x is optimal if and only if there is a potential  $\pi$  such that all edges  $(i, j) \in G(x)$  yield:  $c_{ij}^{\pi} \ge 0$ .

#### 4.2. Tamassia's Approach

Figure 4.2. Vertex- and bend-angles of a planar orthogonal drawing.

# 4.2 Tamassia's Approach

Roberto Tamassia et al. [Di +99] considered a technique where the construction of a flow network is used to minimize the number of bends and to determine the relative position of the incident edges around each vertex by angles. This approach allows a maximal node degree of four, since it assumes that edges adjacent to a node can only lie on the right, top, left, or bottom of a node. In the following, some essentials are introduced to understand this approach.

# 4.2.1 Angles and the Orthogonal Representation

**Definition 4.4** (Angle). A *vertex-angle* is defined by the counter-clockwise angle between two consecutive edges adjacent to a vertex. The angle which is formed by a bend is called *bend-angle*.

**Theorem 4.5.** *The sum of the measures of the vertex-angles around a vertex in an orthogonal plane is equal to* 360°.

**Theorem 4.6.** The sum of the measures of the vertex- and bend-angles inside an internal face f of a planar orthogonal drawing is  $(2n - 4)90^{\circ}$  and  $(2n + 4)90^{\circ}$  for the external face respectively, where n is the number of edges.

The theorem can be understood easily with Figure 4.2. Each arbitrary vertex has an angle measure of exactly  $4 \cdot 90^{\circ}$  around it. An orthogonal representation *H* for a graph *G* is an extension of the planar representation and describes, in addition to the topology, the shape of a drawing for *G* by specifying the angles inside a face and the bends, including bend-angles of the edges. Each edge (v, w) gets a list of angles that form the bends in the final drawing. In addition, each vertex *v* is equipped with a list of adjacent edge and angle pairs. Furthermore, an orthogonal 4. Orthogonalization

Figure 4.3. Orthogonal drawing with four vertices and four bends.

representation can be regarded as an equivalence class for drawings with similar shapes.

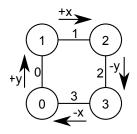

For a better orientation the counter-clockwise angle directions are mapped on identifiers:

$\triangleright$  A 90° angle is called *left*.

$\triangleright$  A 180° angle is called *straight*.

$\triangleright$  A 270° angle is called *right*.

$\triangleright$  A 360° angle is called *full*.

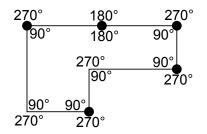

A drawing of the orthogonal representation is presented in Figure 4.3, and the angle-data of that representation is stated as follows:

Table 4.2. Angle-data of Figure 4.3.

| Node | Angles (edge; angle direction)                  |

|------|-------------------------------------------------|

| 0    | ((0,2); straight), ((0,3); left), ((0,1); left) |

| 1    | ((0,1); left), ((1,3); left), ((1,2); straight) |

| 2    | ((1,2); left), ((2,3); straight), ((0,2); left) |

| 3    | ((0,3); straight), ((2,3); left), ((1,3); left) |

For example, let us consider node 0. The edge (0, 2) has as counter-clockwise successor edge (0, 3). The angle between these edges is straight  $(180^\circ)$ . Respectively, the successor of edge (0, 3) is edge (0, 1) with an angle of  $(90^\circ)$  positioned at its left hand side. Meaning if one looks along edge (0, 3) from node 0 to node 3, the edge (0, 1) is the counter-clockwise next angle and lies on the left hand. The same yields for the last entry ((0, 1); left) of the orthogonal representation.

In the following, the transportation problem is described as an illustration in the context of network flow minimization.

#### 4.2. Tamassia's Approach

**Figure 4.4.** Drawing of a directed graph with source *A* and target *B* illustrating the road plan of a transportation problem.

#### **Transportation Problem**

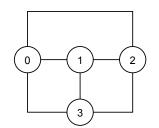

The transportation problem considers the problem of finding an optimal distribution plan for a single commodity. Assuming there is a company which produces commodity in a factory at location A that needs to be transported to a warehouse at location B. An one way road plan is given in Figure 4.4, and a maximal workload of the different roads is the goal. A single road consists of the tuple  $(x_{vw}, c(x), u_{vw})$ and has a lower bound of zero.

Instead of determining the maximal workload, the goal of this part of Tamassia's algorithm is to calculate the minimum workload of the different roads under the condition that each road has to be passed at least one time. This leads to the next subsection.

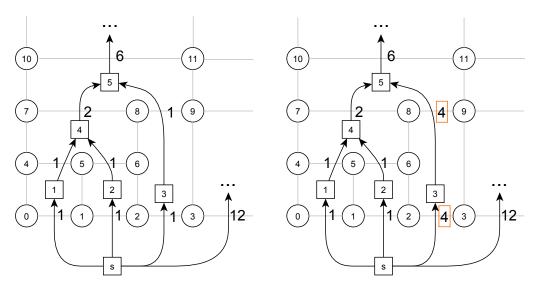

# 4.2.2 Orthogonalization Network Flow

In the context of the orthogonalization, arc properties are only integer variables, and the flow function *x* produces only non-negative values. A *network flow model* for orthogonalization is a directed graph such that the nodes of that model are the vertices and faces of the original graph. Angles can be seen as commodity of the transportation problem that are supplied by the vertices and transported between the faces. The roads of the transportation problem illustrate the arcs of the network. Listing 4.1 shows a brief overview of Tamassia's orthogonalization algorithm which begins with the construction of the flow network. Afterwards, a minimum cost

## 4. Orthogonalization

Figure 4.5. Transformation of a planar embedding to a flow network.

flow is computed for the constructed network. The used minimum cost flow solver in our implementation is the Successive Shortest Path (SSP) algorithm [AMO93]. Finally, the calculated minimum cost flow is used to determine the angle- and bend-data to generate an orthogonal representation.

Listing 4.1. Steps of Tamassia's approach.

- 1 Construct the flow network N;

- Compute flow x of minimum cost for  $\mathfrak{N}$ ;

- 3 Compute orthogonal representation with respect to x;

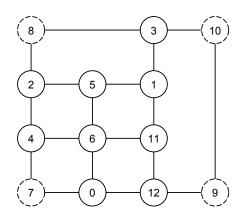

## **Constructing the Flow Network**

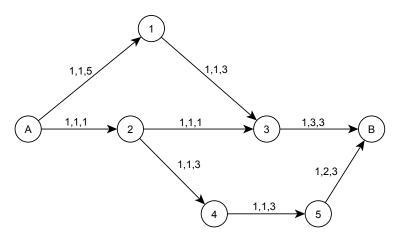

The result of the edge insertion phase 3.2 is a plane graph. To convert a graph into a flow network the following steps have to be done.

- $\triangleright$  Creating a node *v* in  $\mathfrak{N}$  for every vertex and every face of the original graph *G*.

- $\triangleright$  Connecting each vertex node v of N with the face node w of N, if the face is adjacent with the vertex in the original graph G.

- $\triangleright$  Connecting each face node v of N with another face node w of N for every edge in G that is adjacent to both faces.

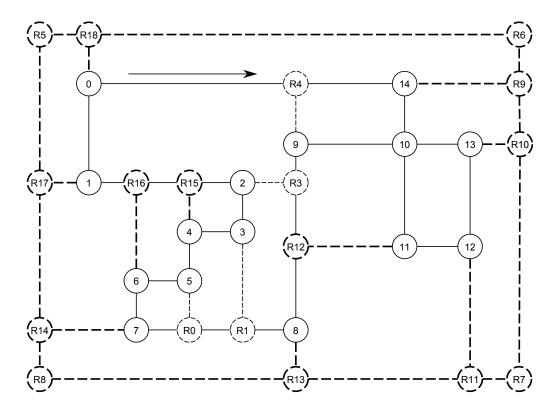

The example of Figure 4.5b shows the creation of the network flow model of a planar embedding. The network flow model consists of 8 nodes in which the round ones are the vertex nodes and the rectangular ones are face nodes. Black

#### 4.2. Tamassia's Approach

solid lines describe the node adjacent face arcs and the black dashed lines are the arcs between adjacent faces. The grey connections correspond to the edges of the original planar embedding 4.5a and illustrate the crossings of the face arcs.

The idea behind the flow network model is as follows. The flow in an arc (v, f) represents the measure of an angle formed at vertex v inside face f bounded by the lower bound  $b_{vf} = \pi/2$  and the capacity  $u_{vf} = 2\pi$ . The cost is zero since such an angle is at a vertex and not at a bend. The flow in arc (f, g) represents the number of bends with  $\pi/2$  angle in face f along an arc between faces f and g. Each unit of cost along such an arc is equal to a bend-point.

#### **Minimum Cost Flow**

The next step is to compute the flow x of minimum cost for  $\mathfrak{N}$  (Listing 4.1). In the following, the SSP algorithm is discussed. It is a popular minimum cost flow solver that utilizes the residual network to find the shortest path.

This algorithm is based on the repeated usage of a shortest path algorithm. Starting with an optimal pseudo flow that ensures the condition of capacity and non-negativity but violates the condition of mass balancing, the algorithm tries to reach the mass balancing without breaking the conditions of optimality and capacity. This SSP algorithm can be viewed as a generalization of the Ford–Fulkerson algorithm [EK72].

| Listing 4.2. | Processing | of the S | SP minimizer. |

|--------------|------------|----------|---------------|

|--------------|------------|----------|---------------|

| 1  | Procedure(n : Network){                                     |

|----|-------------------------------------------------------------|

| 2  | Transform n by adding source and sink                       |

| 3  | Set initial flow $x = 0$                                    |

| 4  | Establish potentials $\pi$ with Bellman & Ford's algorithm. |

| 5  | Reduce cost of $\pi$                                        |

| 6  | while $(G(x)$ contains a path from s to t) {                |

| 7  | Find shortest path P from s to t with Dijkstra's algorithm. |

| 8  | Reduce cost of $\pi$                                        |

| 9  | Get minimal capacity along P                                |

| 10 | Increase current flow x along P with minimal capacity       |

| 11 | Update the residual network $G(x)$                          |

| 12 | }                                                           |

| 13 | }                                                           |

The functionality of the algorithm is described by Listing 4.2. In the first step source and target nodes are added to the network, such that each start node of the network is now successor of the source node and each final node of the

#### 4. Orthogonalization

Figure 4.6. Mapping of the angles from network flow to original graph.

network is now ancestor of the target node. On the one hand, Bellman and Ford's shortest path finder calculates the node potentials, which defines the distance from a node to the source on the shortest path. On the other hand, Bellman and Ford's algorithm is able to detect negative cycles in the network and make all edge costs non-negative. Now, Dijkstra's algorithm<sup>1</sup> with better performance can be used to find shortest paths. In order to keep the edge costs non-negative on each iteration the node potentials are updated and the edge costs are reduced like in Definition 4.2. Additionally, the residual network is updated, and if that network does not contain a path from source to target the algorithm is finished.

Bellman and Ford's algorithm needs O(nm) time, where *n* is the number of arcs and *m* is the number of nodes. The number of iterations is at most *nU*, where *U* is the largest supply, and Dijkstra's shortest path finder needs  $O(n^2)$ . Summing up  $O(n^3U)$  complexity is received for the SSP algorithm.

# 4.2.3 Compute Orthogonal Representation

The minimum cost flow can be computed by the methods introduced in the preceding subsection. Now the question is how to get an orthogonal representation from that minimum cost flow solution. The angles and the bends are derived

<sup>&</sup>lt;sup>1</sup>http://en.wikipedia.org/wiki/Dijkstras\_algorithm

from the minimum flow, separately. To add edge angles to the vertices one has to consider the node arcs of the flow network.

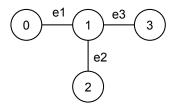

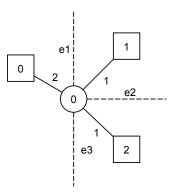

Figure 4.6 illustrates the mapping of the flow of a node arc to its corresponding angle. The round node is the original vertex that has node arcs to the angular adjacent face nodes. The MCF solver calculates a flow value of 2 for arc (0,0), 1 for arc (0,1), and 1 for arc (0,2). The flow is directly mapped to the angle between the adjacent face and a flow value, where

$\triangleright$  0 forms a left angle,

> 1 forms a straight angle,

$\triangleright$  2 forms a right angle, and

$\triangleright$  3 forms a full angle.

In the presented example the angle between *e*1 and *e*3 is a straight one, the one between *e*3 and *e*2 is a left angle, and the one between *e*2 and *e*1 is left as well.

Bends are the units of the flow of face arcs. Hence, to add the bends to the original graph edges means to iterate over all face arcs of the network and furthermore adding the bends to the corresponding original edges in the original graph. Depending on the left and right face of an edge the bends are added with left or right angle.

# 4.3 **Preprocessing**

The orthogonalization phase uses the faces of the given planar embedding to create the flow network. After the planarization step, there is a possibility that these faces are unknown, especially other preprocessors are able to insert dummies that lead to another faces environment. Hence, an own intermediate processor is implemented for the determination of the faces, denoted as FaceProcessor. That algorithm is the same as the one in Section 3.2.1.

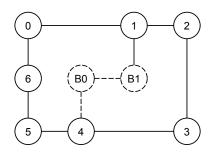

## 4.3.1 The External Face

An extension of the face calculation is the choice of a maximal external face. A face is maximal if its number of adjacent edges is higher or equal to the number of adjacent edges of any other face. Every face of the graph embedding can be treated as external, by simply turning inside out. Additionally, this ensures the embedding

## 4. Orthogonalization

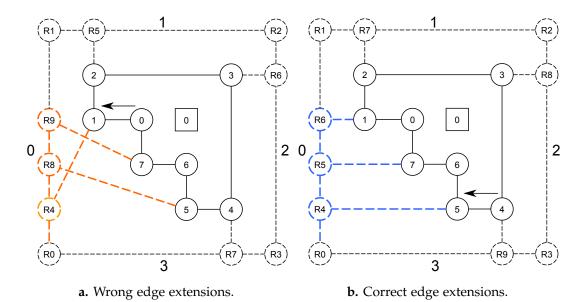

a. Embedding with an external face with few adjacent edges.b. Embedding with an external face with most adjacent edges.

since the counter-clockwise order of edges around every node of Figure 4.7a is equal to the order of edges around every node of Figure 4.7b.

Even if the embedding of the presented example on the left side is equal to the one on the right side, the external faces are different. Using a non-maximal external face (Figure 4.7a) results in a representation with the undesired edge (0, 2) marked bold since the algorithm has to lay this edge around the remaining elements of the graph drawing. Figure 4.7b shows a drawing of the same embedding with a maximal external face. The length of the edge (0, 2) is less than the length of the same edge in Figure 4.7a whereas all other edges have same edge lengths. Reflecting the aesthetics criteria of Section 2.1.3 the minimal total edge length of the graph drawing should be ensured to let the used area be minimal. Hence, it is meaningful to use a maximal face as external.