## Hardwaresynthese aus SCCharts

Gunnar Johannsen

Master Thesis eingereicht im Jahr 2013

Christian-Albrechts-Universität zu Kiel Real-Time and Embedded Systems Group Prof. Dr. Reinhard von Hanxleden

Betreut durch:

Dipl.-Inf. Ass. iur. Insa Marie-Ann Fuhrmann Dipl.-Inf. Christian Motika

| Eidesstattliche Erklärung                                                                                                                                                |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Hiermit erkläre ich an Eides statt, dass ich die vorliegende Arbeit selbstständig verfasst und keine anderen als die angegebenen Quellen und Hilfsmittel verwendet habe. |

| Kiel, 19.10.2013                                                                                                                                                         |

|                                                                                                                                                                          |

|                                                                                                                                                                          |

### Zusammenfassung

Sequentially Constructiveness Charts (SCCharts) ist eine grafische synchrone Modellierungssprache zum Modellieren deterministischer reaktiver Systeme. Damit Programme, die mit synchronen Sprachen erzeugt wurden, auf solchen Systemen ausgeführt werden können, werden sie zum Beispiel in C oder Java übersetzt. Ebenfalls ist die Synthese nach Hardware möglich.

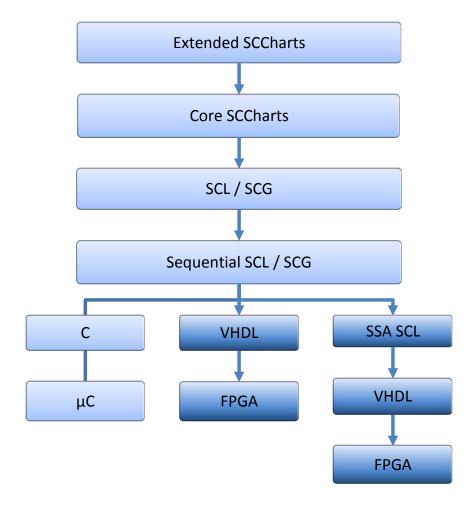

Diese Masterarbeit präsentiert zwei Synthesen um aus SCCharts Hardwareschaltkreise zu synthetisieren. Vorbereitend werden SCCharts in eine sequentielle Repräsentation übersetzt [Smy13]. Ausgehend von dieser Repräsentation wird in der ersten Transformation direkt aus der sequentiellen Repräsentation sequentieller VHDL-Code generiert, der nachfolgende in Hardware transformiert werden kann. Bestehende Datenabhängigkeiten in der sequentiellen Repräsentation werden dabei vom VHDL-Compiler aufgelöst. In der zweiten Transformation werden die bestehende Datenabhängigkeiten mit Hilfe einer Transformation aufgelöst, um nachfolgend parallelen VHDL-Code zu erzeugen. Dieser kann wiederum in einen Schaltkreis synthetisiert werden.

Die vorgestellten Synthesen wurden in dem Forschungsprojekt Kiel Integrated Environment for Layout Eclipse Rich Client (KIELER) implementiert. Auf dieser Grundlage wurden die Synthesen im Rahmen dieser Arbeit evaluiert.

Weiterhin wird eine Beispielimplementierung auf einem FPGA und ein Regressionstest vorgestellt, mit dem die korrekte Funktionsweise synthetisierter Schaltkreise überprüft wurde.

## Inhaltsverzeichnis

| 1 | Ein | leitung                                                    | 1  |

|---|-----|------------------------------------------------------------|----|

|   | 1.1 | Synchrone Sprachen                                         | 2  |

|   |     | 1.1.1 SyncCharts                                           | 3  |

|   |     | 1.1.2 Sequentiell konstruktives Ausführungsmodell          | 6  |

|   |     | 1.1.3 SCCharts                                             | 6  |

|   | 1.2 | Aufgabenstellung                                           | 7  |

|   | 1.3 | Aufbau der Arbeit                                          | 8  |

| 2 | Ver | wandte Arbeiten                                            | 11 |

|   | 2.1 | Softwaresynthese aus SyncCharts                            | 11 |

|   | 2.2 | Hardwaresynthese                                           | 12 |

|   |     |                                                            | 12 |

|   |     | 2.2.2 Esterel                                              | 13 |

|   |     |                                                            | 15 |

|   | 2.3 | -                                                          | 16 |

|   |     |                                                            | 16 |

| 3 | Ver | wendete Technologien                                       | 19 |

|   | 3.1 | Eclipse                                                    | 19 |

|   |     | 3.1.1 Eclipse Modeling Framework                           | 21 |

|   |     | 3.1.2 Xtend                                                | 22 |

|   | 3.2 | Das JUnit Framework                                        | 23 |

|   | 3.3 | Kiel Integrated Environment for Layout Eclipse Rich Client | 23 |

|   | 3.4 | Die Hardwarebeschreibungssprache VHDL                      | 25 |

|   |     | 3.4.1 Die Programmierung mit VHDL                          | 26 |

|   |     | 3.4.2 Simulation von Hardwarebeschreibungen                | 26 |

|   | 3.5 | ISE Design Umgebung                                        | 27 |

|   |     | 3.5.1 ISE Simulator                                        | 28 |

| 4 | Tra | nsformation                                                | 29 |

|   | 4.1 | Die verwendeten Sprachkonzepte                             | 29 |

|   |     | ±                                                          | 30 |

|   |     | 4.1.2 SCCharts                                             | 32 |

|   |     | 4.1.3 Sequentially Constructive Language                   | 36 |

|   | 4.2 | SCCharts Transformation                                    | 38 |

|   |     | 4.2.1 Extended SCCharts zu Core SCCharts Transformation    | 39 |

|   |     | 4.2.2 Core SCCharts zu SCL Transformation                  | 39 |

#### Inhaltsverzeichnis

|   |            | 4.2.3 Der SC-Graph                                            | . 41  |

|---|------------|---------------------------------------------------------------|-------|

|   |            | 4.2.4 Analysen auf dem SCG                                    | 42    |

|   |            | 4.2.5 SCL zu sequentiellem SCL Transformation                 | . 44  |

|   | 4.3        | Naive VHDL Transformation                                     | 46    |

|   |            | 4.3.1 Das VHDL Prozess Konstrukt                              | . 47  |

|   |            | 4.3.2 Interface Deklaration                                   | 49    |

|   |            | 4.3.3 Sequentielles SCL zu VHDL Transformation                | 49    |

|   |            | 4.3.4 Das ABO Beispiel                                        | 50    |

|   | 4.4        | Zweiter Transformationsansatz                                 | 50    |

|   |            | 4.4.1 Das Static Single Assignment                            | 52    |

|   |            | 4.4.2 SCL zu SSA SCL Transformation                           | . 54  |

|   |            | 4.4.3 SSA SCL zu VHDL Transformation                          | 59    |

|   |            | 4.4.4 Das Starten und Rücksetzen von transformierten SCCharts | 70    |

|   |            | 4.4.5 Ein vollständiges Beispiel in VHDL                      | . 77  |

| _ |            |                                                               |       |

| 5 |            | comatischer Test                                              | 81    |

|   | 5.1        | Testen vom Modellen                                           |       |

|   |            | 5.1.1 Das ESI/ESO Format                                      |       |

|   |            | 5.1.2 Das Core ESO Format                                     |       |

|   |            | 5.1.3 ESO zu Core ESO Transformation                          |       |

|   | <b>-</b> 2 | 5.1.4 ESO zu VHDL Testbench Transformation                    |       |

|   |            | ISE Simulator                                                 |       |

|   | 5.3        | Regressionstest                                               |       |

|   |            | 5.3.1 Funktionsweise des automatischen Regressionstests       |       |

|   |            | 5.3.2 Implementierung                                         | . 97  |

| 6 | Imp        | olementierung                                                 | 101   |

|   | 6.1        | Details zur Eclipse Implementierung                           | . 101 |

|   |            | 6.1.1 Naive VHDL Transformation                               | 102   |

|   |            | 6.1.2 Sequentielles SCL zu SSA SCL Transformation             | 102   |

|   |            | 6.1.3 SSA SCL zu VHDL Transformation                          | 102   |

|   |            | 6.1.4 ESO zu Core ESO Transformation                          | 103   |

|   |            | 6.1.5 Core ESO zu VHDL Testbench Transformation               | 103   |

|   |            | 6.1.6 Automatischer JUnit Test                                | 103   |

|   | 6.2        | Hardwaresynthese                                              | 103   |

|   |            | 6.2.1 Aufbau eines FPGAs                                      | . 104 |

|   |            | 6.2.2 Place and Route Algorithmus                             | 105   |

|   |            | 6.2.3 Implementierung von ABO auf einem FPGA                  | 106   |

| 7 | Evo        | luierung                                                      | 113   |

| • | Eva        |                                                               |       |

|   |            | Testverfahren                                                 |       |

#### Inhaltsverzeichnis

|    | 7.3   | Evaluierung von Core SCCharts ohne Hierarchie und nebenläufige Re- |       |

|----|-------|--------------------------------------------------------------------|-------|

|    |       | gionen                                                             | 115   |

|    | 7.4   | Evaluierung hierarchischer Core SCCharts                           | 116   |

|    | 7.5   | Fazit der Evaluation                                               | 118   |

| 8  | Faz   | it                                                                 | 121   |

|    | 8.1   | Zusammenfassung                                                    | . 121 |

|    | 8.2   | Weiterführende Arbeiten                                            | 122   |

|    |       | 8.2.1 Datentypen                                                   | 122   |

|    |       | 8.2.2 Terminierung                                                 | 123   |

|    |       | 8.2.3 SSA Optimierungen                                            | 123   |

|    |       | 8.2.4 Optimierte Transformation                                    | . 124 |

| D  | anks  | sagungen                                                           | 127   |

| Bi | iblio | graphy                                                             | 129   |

# Abbildungsverzeichnis

| 1.1 | Ein eingebettetes reaktives System [MvHH13]                            | 1  |

|-----|------------------------------------------------------------------------|----|

| 1.2 | Die Synchronizitätsshypothese (G. Luettgen, 2001)                      | 3  |

| 1.3 | Das "Hello World" der SyncCharts — ABRO [Smy13]                        | 4  |

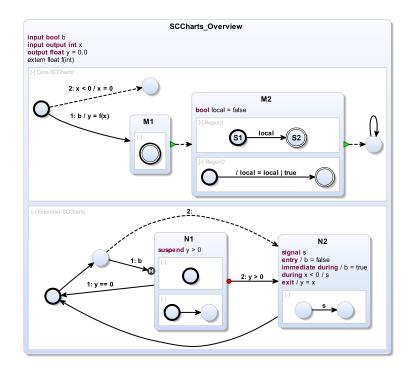

| 1.4 | Das ABO Beispiel modelliert als Core SCChart                           | 7  |

|     |                                                                        | 14 |

| 2.2 |                                                                        | 15 |

|     | (a) Esterels emit Befehl in Software                                   | 15 |

|     | (b) Esterels emit Befehl in Hardware [Ber02]                           | 15 |

| 2.3 | Der Esterel pause Befehl in Soft- und Hardware                         | 15 |

|     | (a) Esterels pause Befehl in Software                                  | 15 |

|     | (b) Esterels pause Befehl in Hardware [Ber02]                          | 15 |

| 2.4 | EDIF Codeausschnitt eines NAND-Gatters inkl. der logischen und physi-  |    |

|     | kalischen Sicht des Gatters [Cra84]                                    | 17 |

|     | (a) EDIF Codeausschnitt                                                | 17 |

|     | (b) Logische Sicht                                                     | 17 |

|     | (c) Physikalische Sicht                                                | 17 |

| 3.1 | Eine Perspektive einer Eclipse Workbench [Har13]                       | 20 |

| 3.2 | Beispiel eines Meta Modells — SCL Meta Modell                          | 21 |

| 3.3 | Beispiel für das Xtend Template                                        | 22 |

|     | (a) Xtend Template Code                                                | 22 |

|     | (b) Erzeugter VHDL Code                                                | 22 |

| 3.4 | Übersicht des KIELER Projektes [RK13]                                  | 24 |

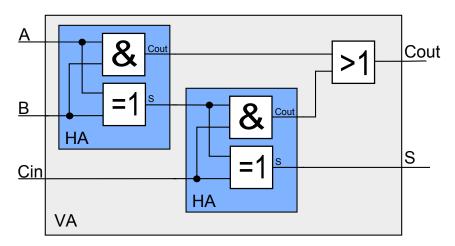

| 3.5 | Komponenten Sicht eines 2 Bit Addierers                                | 26 |

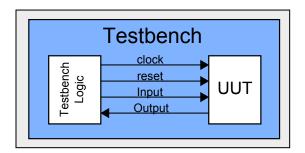

| 3.6 | Abstrakte Sicht auf eine VHDL Testbench, mit Testbench Logik und dem   |    |

|     | Unit Under Test                                                        | 27 |

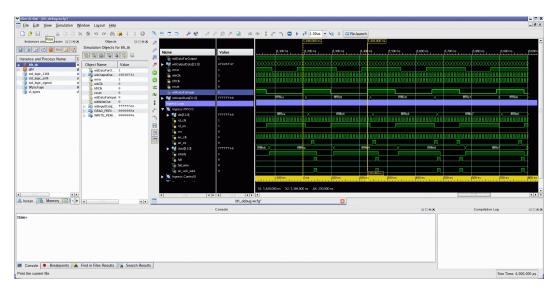

| 3.7 | ISE-Simulator mit einem Signaldiagramm                                 | 28 |

| 4.1 | Transformationsschritte von extended SCCharts zu Hard- und Software    | 30 |

| 4.2 | Eine Variable die eventuell zwei Werte in einem Tick besitzt           | 33 |

|     | (a) Variable mit möglichweise zwei verschiedenen Werten                | 33 |

|     | (b) SCChart mit einer Variablen die eventuell zwei Werte in einem Tick |    |

|     | besitzt                                                                | 33 |

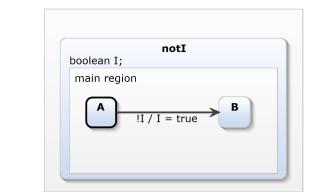

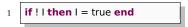

| 4.3 | SCCharts Übersicht [MSvHM13]                                           | 33 |

| 4.4 | Das ABO Beispiel als SCChart modelliert                                | 35 |

| 4.5 | Übersicht der SCL und SCG Befehle [vHMA <sup>+</sup> 13b]              | 36 |

## Abbildungsverzeichnis

| 4.6  | Tran    | sformationsbeispiel von SCL zu sequentiellen SCL                     | 38 |

|------|---------|----------------------------------------------------------------------|----|

|      | (a)     | Einfaches SCL-Programm                                               | 38 |

|      | (b)     | Einfaches SCL-Program in sequentiellen SCL                           | 38 |

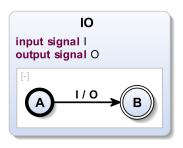

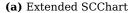

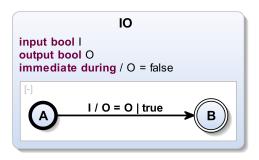

| 4.7  | Beis    | piel einer Transformation von Extended SCCharts zu Core SC-          |    |

|      | Cha     | rts [MSvHM13]                                                        | 40 |

|      | (a)     | Extended SCChart                                                     | 40 |

|      | (b)     | Extended SCCharts mit During Actions                                 | 40 |

|      | (c)     | Core SCChart                                                         | 40 |

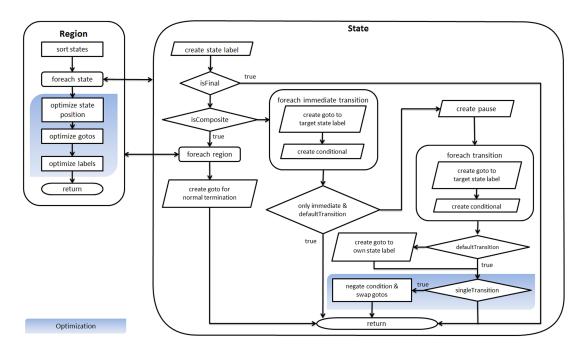

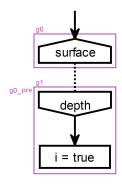

| 4.8  | Core    | e SCChart zu SCL — Transformationsübersicht für Zustände [Smy13]     | 41 |

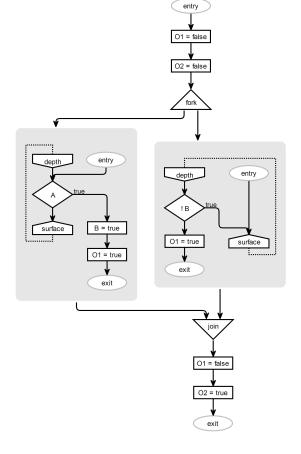

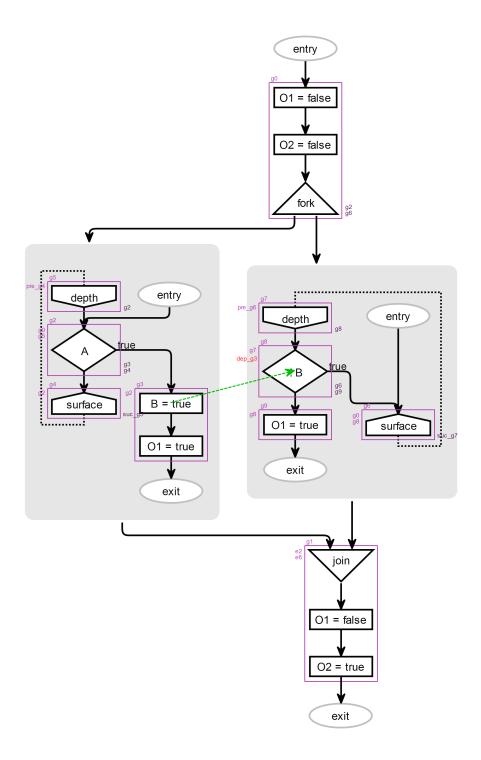

| 4.9  | ABO     | als SCG visualisiert                                                 | 42 |

| 4.10 | )ABO    | als SCG mit Basic Blocks und Abhängigkeitskanten                     | 45 |

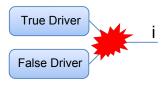

| 4.11 | l Ein I | Kurzschluss in Hardware durch zwei parallele Zuweisungen zu einem    |    |

|      | _       |                                                                      | 47 |

| 4.12 | 2Tran   | •                                                                    | 48 |

|      | (a)     | 1 3                                                                  | 48 |

|      |         | 3                                                                    | 48 |

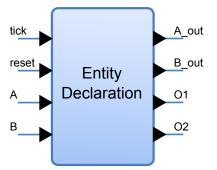

| 4.13 |         | piel einer Entity Deklaration in SCL und dem passenden VHDL-         |    |

|      | Bloc    |                                                                      | 49 |

|      | (a)     | 1                                                                    | 49 |

|      |         | 3                                                                    | 49 |

| 4.14 |         | omatisch generierter VHDL Code von ABO mit der naiven Transfor-      |    |

|      |         | on                                                                   | 51 |

| 4.15 | -       | chetisierter Schaltkreis von ABO aus dem mit der naiven Transfor-    |    |

|      |         |                                                                      | 52 |

| 4.16 |         | einer einfachen Variablen Zuweisungen zu Variablen Zuweisungen       |    |

|      |         | er SSA-Form                                                          | 53 |

|      | (a)     | Einfache Zuweisungen zu veschiedenen Variablen                       | 53 |

|      | (b)     | Einfache Zuweisungen zu verschiedenen Variablen in der SSA Form      |    |

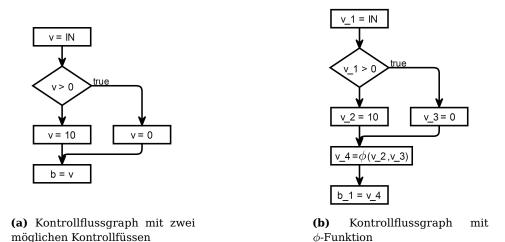

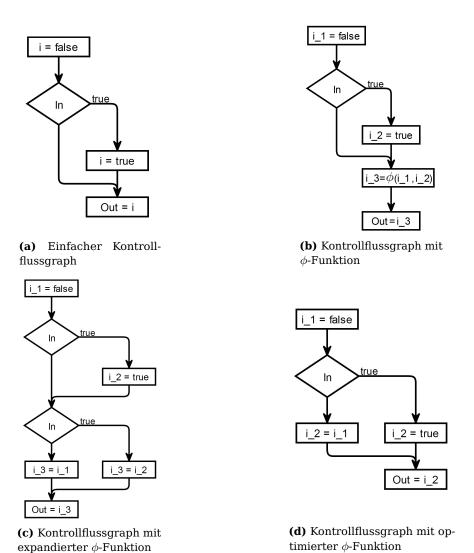

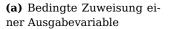

| 4.17 |         | SSA - $\phi$ -Funktion angewendet auf einen einfachen Kontrollfluss  |    |

|      | (a)     | Kontrollflussgraph mit zwei möglichen Kontrollfüssen                 |    |

|      | (b)     | Kontrollflussgraph mit $\phi$ -Funktion                              | 54 |

| 4.18 |         | $\phi$ -Funktion angewendet auf einen einfachen Kontrollflussgraphen |    |

|      |         | Umsetzung und Optimierung der $\phi$ -Funktion                       | 55 |

|      | (a)     | Einfacher Kontrollflussgraph                                         | 55 |

|      | (b)     | Kontrollflussgraph mit $\phi$ -Funktion                              | 55 |

|      | (c)     | Kontrollflussgraph mit expandierter $\phi$ -Funktion                 | 55 |

|      | (d)     | Kontrollflussgraph mit optimierter $\phi$ -Funktion                  | 55 |

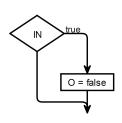

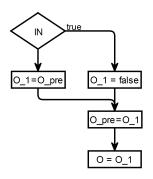

| 4.19 |         | SSA Form angewandt auf ein bedingtes Schreiben einer Ausgabeva-      |    |

|      |         |                                                                      | 57 |

|      | (a)     | Bedingte Zuweisung einer Ausgabevariable                             |    |

|      | (b)     | Bedingte Zuweisung zu einer Ausgabevariable in SSA Form              | 57 |

| 4.20 Die SSA Form angewandt auf ein bedingtes Schreiben einer Ein-Ausgabe- |    |

|----------------------------------------------------------------------------|----|

| variable                                                                   | 58 |

| (a) Bedingte Zuweisung einer Ein-Ausgabevariable                           | 58 |

| (b) Bedingte Zuweisung einer Ein-Ausgabevariable in SSA Form               | 58 |

| 4.21 Die SSA Form angewendet auf eine Pause Anweisung unter Verwendung     |    |

| der Basic Blocks                                                           | 59 |

| (a) Kontrollflussgraph einer Pause Anweisung mit Basic Blocks              | 59 |

| (b) Kontrollflussgraph einer Pause Anweisung in SSA Form                   | 59 |

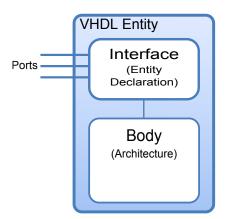

| 4.22 Struktur einer VHDL Entity                                            | 61 |

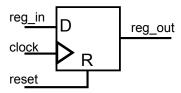

| 4.23Ein einfaches Register beschrieben in VHDL und dessen grafische Re-    |    |

| präsentation                                                               | 64 |

| (a) VHDL Code zum Erzeugen eines Registers mit taktsynchronen Reset        | 64 |

| (b) Register als Schaltsymbol                                              | 64 |

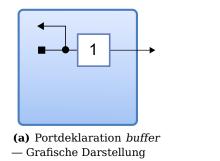

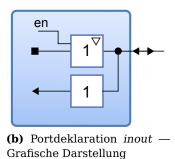

| 4.24Besondere Portdeklarationen in VHDL                                    | 65 |

| (a) Portdeklaration buffer — Grafische Darstellung                         | 65 |

| (b) Portdeklaration inout — Grafische Darstellung                          | 65 |

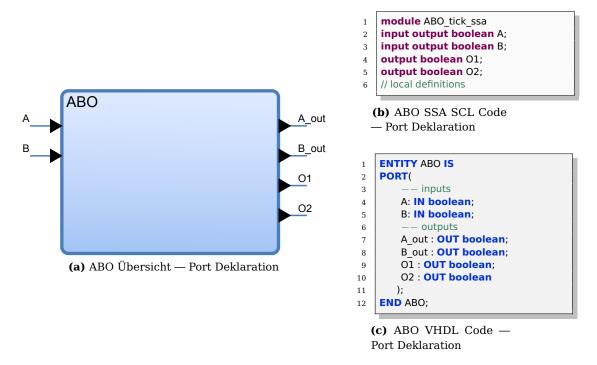

| 4.25ABO - Interface Deklaration                                            | 66 |

| (a) ABO Übersicht — Port Deklaration                                       | 66 |

| (b) ABO SSA SCL Code — Port Deklaration                                    | 66 |

| (c) ABO VHDL Code — Port Deklaration                                       | 66 |

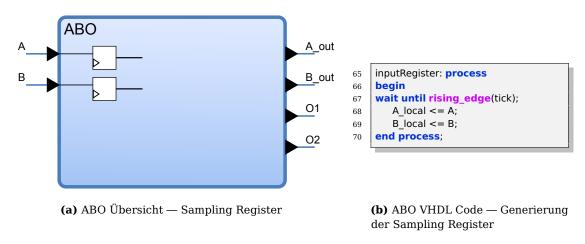

| 4.26ABO - Generierung der Sampling Register                                | 66 |

| (a) ABO Übersicht — Sampling Register                                      | 66 |

| (b) ABO VHDL Code — Generierung der Sampling Register                      | 66 |

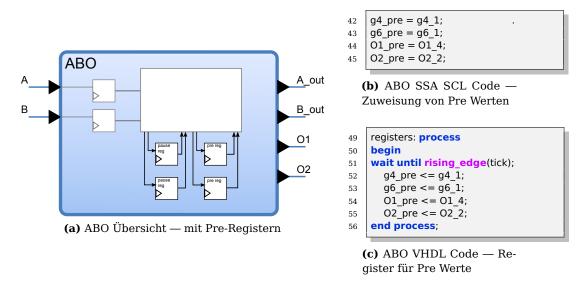

| 4.27ABO — Generierung von Pre Registern                                    | 67 |

| (a) ABO Übersicht — mit Pre-Registern                                      | 67 |

| (b) ABO SSA SCL Code — Zuweisung von Pre Werten                            |    |

| (c) ABO VHDL Code — Register für Pre Werte                                 |    |

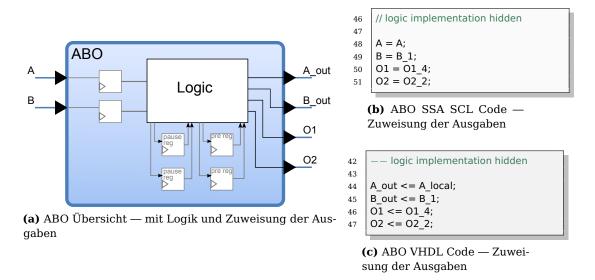

| 4.28ABO - Zuweisen der Ausgaben                                            | 68 |

| (a) ABO Übersicht — mit Logik und Zuweisung der Ausgaben                   | 68 |

| (b) ABO SSA SCL Code — Zuweisung der Ausgaben                              | 68 |

| (c) ABO VHDL Code — Zuweisung der Ausgaben                                 | 68 |

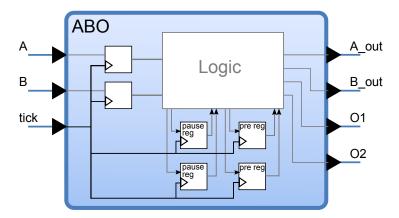

| 4.29ABO Übersicht — mit Tick-Signal                                        | 69 |

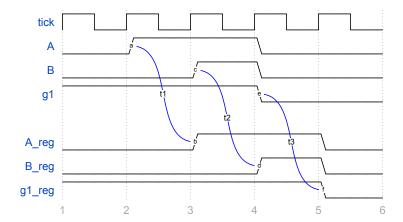

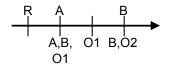

| 4.30Tick Signal Diagramm — Wann werden Werte in Registern gespeichert      | 69 |

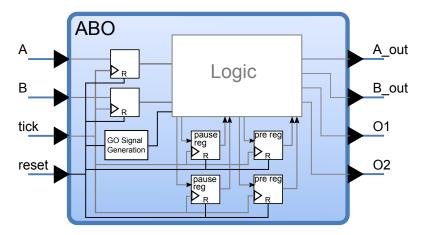

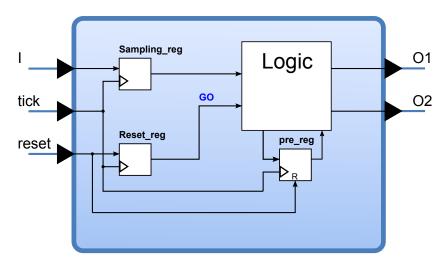

| 4.31ABO Übersicht — mit Reset und GO Signal                                | 70 |

|                                                                            | 71 |

| 4.33 Schaltplan der ersten Reset-Variante                                  |    |

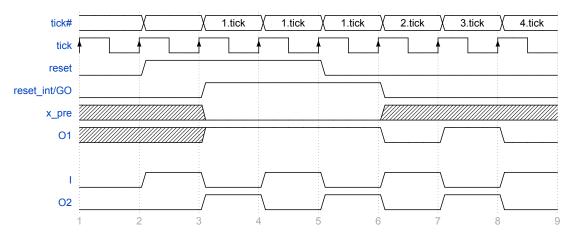

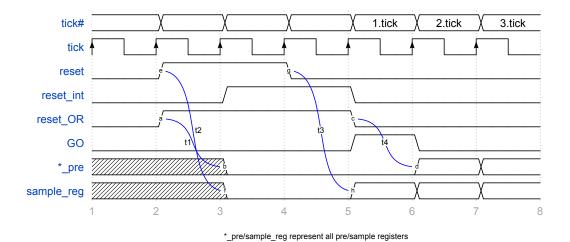

| 4.34 Signalverlauf der ersten Reset-Variante                               | 72 |

| 4.35ABO Ausführungspfad — Zweite Reset-Variante                            | 73 |

| 4.36 Schaltplan der zweiten Reset-Variante                                 |    |

| 4.37 Signalverlauf der zweiten Reset-Variante mit GO- und Reset-Signal     | 75 |

| 4.38 Vollständiger ABO VHDL Code — erzeugt mit der SSA SCL Transformation  |    |

## Abbildungsverzeichnis

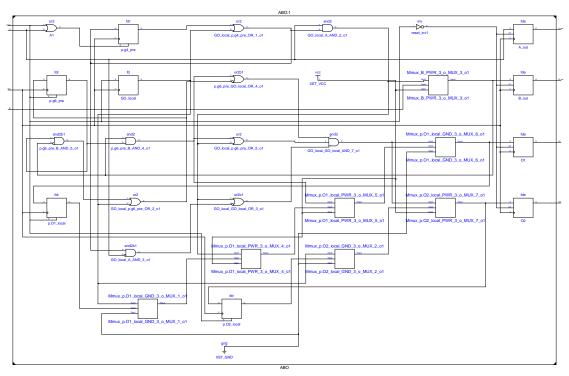

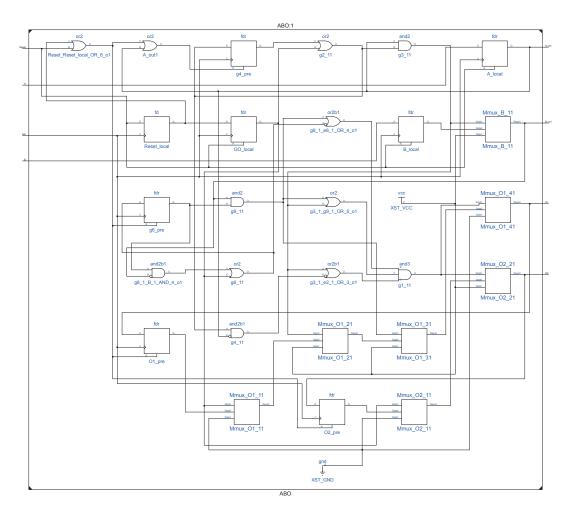

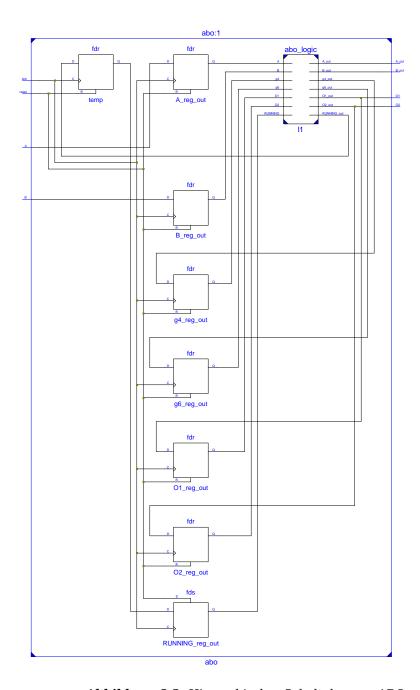

| 4.39 | OABO Schaltplan generiert aus dem VHDL Code der SSA SCL Transformation              | 79             |

|------|-------------------------------------------------------------------------------------|----------------|

| 5.1  | Transformation eines ESO zu Core ESO Traces mit wertbehafteten Signalen             | 85<br>85<br>85 |

| 5.2  | Vollständige ABO VHDL Testbench                                                     | 89             |

| 5.3  | Xtend Quellcodeausschnitt der Transformationsmethode zum Erzeugen                   |                |

|      | der Testbench Entity mit Hilfe von Rich Strings                                     | 92             |

| 5.4  | Xtend Methode die den Tick Prozess mit Hilfe vom Rich Strings erzeugt               | 93             |

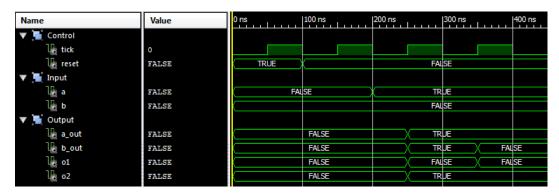

| 5.5  | Signalverlauf von ABO im ISE Simulator                                              |                |

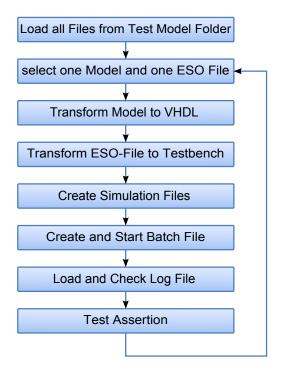

| 5.6  | Die einzelnen Schritte des Regressionstests                                         | 96             |

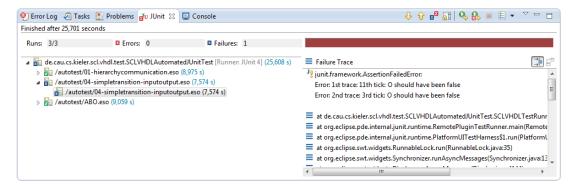

| 5.7  | Ergebnisse eines Regressionstests                                                   | 97             |

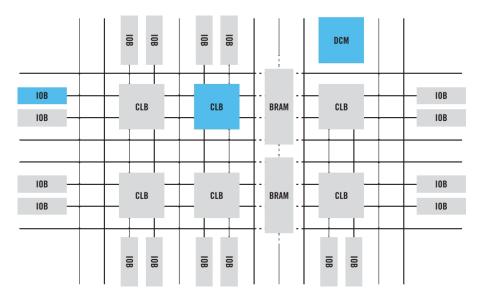

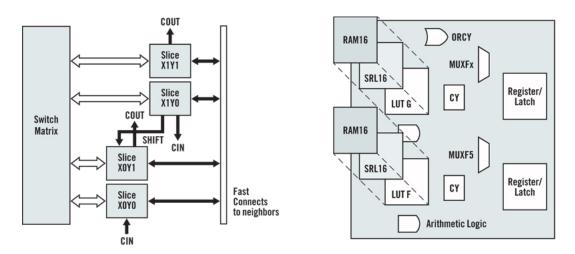

| 6.1  | Block Struktur eines FPGAs [Inc13]                                                  | 105            |

| 6.2  | Struktur zweier CLBs (links) und einer Slice (rechts) [Inc13]                       | 106            |

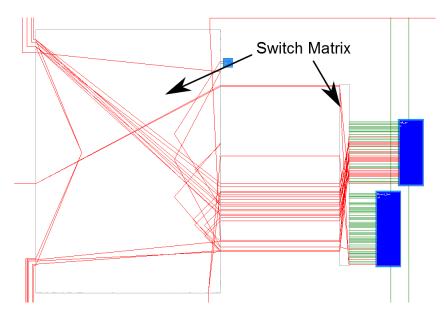

| 6.3  | Sicht auf eine FPGA mit zwei gerouteten Slices                                      | 107            |

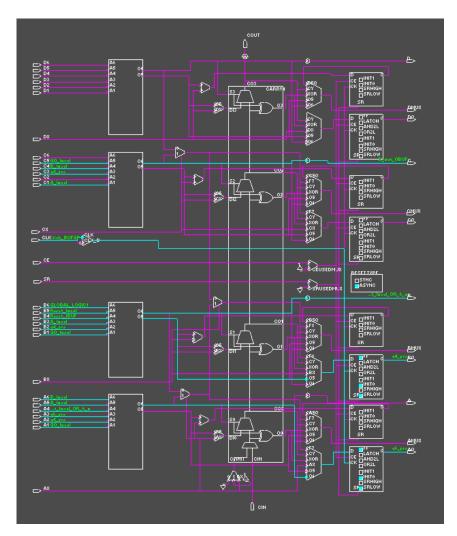

| 6.4  | Die interne Sicht einer konfigurierten Slice                                        | 108            |

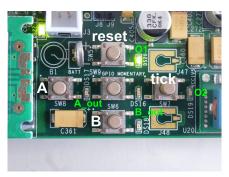

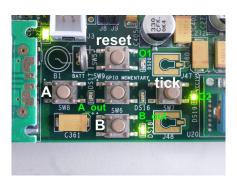

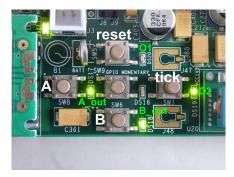

| 6.5  | 51                                                                                  | 109            |

|      | 1 0                                                                                 | 109            |

| 6.7  | ABO auf Hardware — zwei Ausführungspfade                                            |                |

|      | (a) ABO auf Hardware — Ausführungspfad A                                            |                |

|      | (b) ABO auf Hardware — Ausführungspfad A — erster Tick                              |                |

|      | (c) ABO auf Hardware — Ausführungspfad A — zweiter Tick                             |                |

|      | (d) ABO auf Hardware — Ausführungspfad A — dritter Tick                             |                |

|      | (e) ABO auf Hardware — Ausführungspfad B                                            |                |

|      | (f) ABO auf Hardware — Ausführungspfad B — erster Tick                              |                |

|      | (g) ABO auf Hardware — Ausführungspfad B — zweiter Tick                             | 111            |

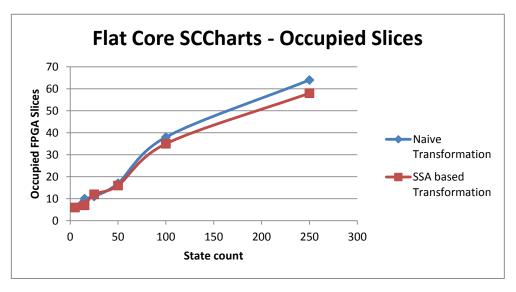

| 7.1  | Evaluationsergebnis flacher Core SCCharts — belegte Slices                          | 115            |

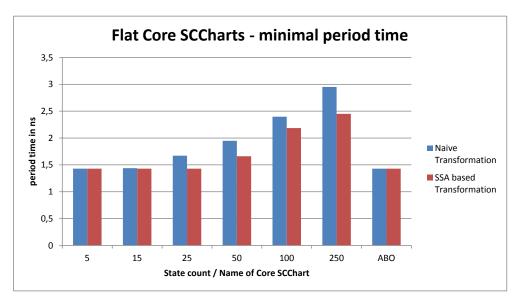

| 7.2  | Evaluationsergebnis flacher Core SCCharts — minimale Periodendauer                  | 116            |

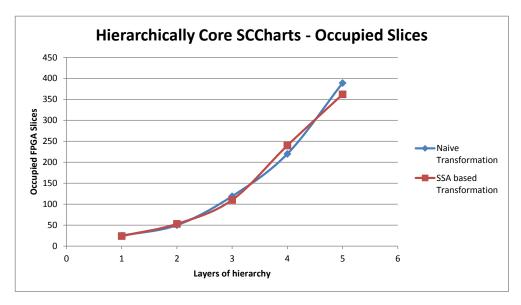

| 7.3  | ${\bf Evaluation sergebn is\ hierarchischer\ Core\ SCCharts-belegte\ Slices} . \ .$ | 117            |

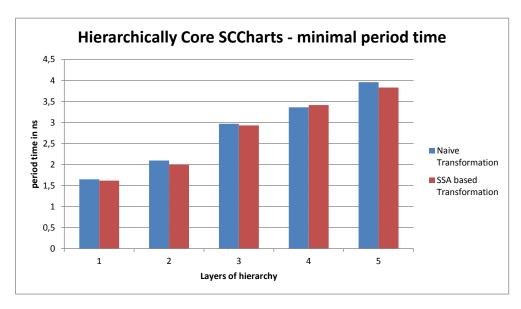

| 7.4  | Evaluationsergebnis hierarchischer Core SCCharts — minimale Periodendauer           | 118            |

| 8.1  | Hierarchischer SCL Code mit zwei Modulen                                            | 125            |

|      |                                                                                     | 126            |

# Listings

| 2.1        | Esterel Software Modul                                          | 4      |

|------------|-----------------------------------------------------------------|--------|

| 4.1        | ABO — mit optimiertem SCL Code Code                             | 2      |

| 4.2        | ABO — sequentieller SCL Code                                    | 6      |

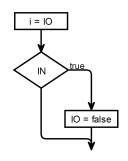

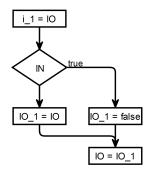

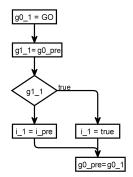

| 4.3        | Sequentielle Zuweisungen zu einer Variablen i                   | 7      |

| 4.4        | ABO in sequentiellen SSA SCL Code 6                             | 0      |

| 5.1        | Ein ESO Trace für ABO                                           | 2      |

| 5.2        | Core ESO Trace für ABO                                          | 3      |

| 5.3        | Pseudo Code der Methode zum Generieren von Core ESO Dateien aus |        |

|            | ESO Dateien                                                     | 6      |

| 5.4        | VHDL Testbench — Struktureller Aufbau                           | 8      |

|            |                                                                 |        |

| 5.5        | Eine Log Datei vom ISE Simulator                                | 4      |

|            | Eine Log Datei vom ISE Simulator9Eine Projekt Datei für ABO9    |        |

| 5.6        |                                                                 | 8      |

| 5.6<br>5.7 | Eine Projekt Datei für ABO                                      | 8<br>9 |

## **Tabellenverzeichnis**

| 4.1 | Übersicht der Eigenschaften der beiden Reset-Varianten           | 76  |

|-----|------------------------------------------------------------------|-----|

| 5.1 | Simulations- und Compiler-Optionen von ISE [Inc09]               | 100 |

| 6.1 | Übersicht der Transformationen und der passenden Eclipse Plugins | 101 |

## Abkürzungsverzeichnis

$\it KIELER$  Kiel Integrated Environment for Layout Eclipse Rich Client

UML Unified Modeling Language

EMF Eclipse Modeling Framework

GMF Graphical Modeling Framework

MoC Model of Computation

XML Extensible Markup Language

IDE integrated design environment

KIEM KIELER Execution Manager

M2M model-to-model

RCP Rich Client Platform

IEEE IEEE

MDE Model-Driven Engineering

EDIF Electronic Design Interchange Format

SSA Static Single Assignment

VHDL Very High Speed Integrated Circuit Description Language

Verilog Verilog

ISE Integrated Software Environment

ISim ISE Simulator

Xtend Xtend

Xtext Xtext

IDE integrierte Entwicklungsumgebung

UML Unified Modeling Language

IBM International Business Machines Corporation

#### **Tabellenverzeichnis**

XMI XML Metadata Interchange

MtM Model zu Model

SCL Sequentially Constructive Language

KSbasE KIELER Structure-based Editing

KLighD KIELER Lightweight Diagrams

KIML KIELER Infrastructure for Meta Layout

KLay KIELER Layouters

**UUT** Unit Under Test

ISE Integrated Software Environment

RTL Register Transfer Logic

ISim ISE Simulator

IEC International Electrotechnical Commission

SCG Sequentially Constructive Graph

DCM Digital Clock Manager

CLB Configurable Logic Block

KEP Kiel Esterel Processor

## **Einleitung**

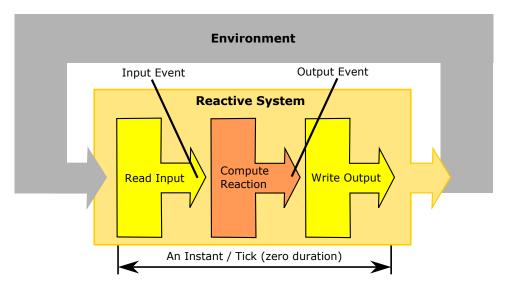

Systeme, die kontinuierlich mit der Umwelt interagieren, nennt man reaktive Systeme, wie zum Beispiel das Motorsteuergerät eines Autos, die Airbagsteuerung oder mobile Telefone. Ein solches System durchläuft für eine Reaktion drei Phasen. In der ersten Phase werden die Eingaben der Umgebung gelesen, danach folgt die Berechnung der Reaktion auf die Eingaben, und zum Schluss werden die berechneten Ausgaben zurück an die Umgebung gegeben. Der zeitliche Ablauf reaktiver Systeme ist von der Umgebung abhängig und wird nicht durch das System selber bestimmt. Die Abbildung 1.1 zeigt ein reaktives System.

Da solche Systeme oft gleichzeitig auf mehrere Eingaben aus der Umwelt reagieren, bestehen sie aus mehreren nebenläufigen Teilsystemen. In der Regel wird für reaktive Systeme dieser Art ein deterministisches Verhalten vorausgesetzt. Solche Systeme lassen sich nur bedingt mit Sprachen wie Java oder C programmieren, da bei diesen Sprachen schwer nebenläufiger Determinismus erreicht werden kann.

So ist für die Verwendung von eingebetteten reaktiven Systemen in Bereichen der Automobil-, Flugzeug- oder medizinischen-Industrie eine deterministische nebenläufige Ausführung unerlässlich. Auftretende Fehler können gerade in diesen

**Abbildung 1.1.** Ein eingebettetes reaktives System [MvHH13]

#### 1. Einleitung

Bereichen im schlimmsten Fall Menschen das Leben kosten. Für die deterministische Programmierung von reaktiven Systemen, speziell für sicherheitskritische Systeme, wurden synchrone Sprachen entwickelt, die den Anforderungen nachkommen.

### 1.1 Synchrone Sprachen

Synchrone Sprachen sind speziell für die deterministische nebenläufige Programmierung von reaktiven Systemen entwickelt. Sie unterbinden nichtdeterministische Ausführungen nebenläufiger Threads, im Gegensatz zu C oder Java, welches einer der Hauptgründe für deren Nichtdeterminismus ist. Die synchronen Sprachen stellen Konstrukte zur Programmierung von deterministischer Nebenläufigkeit zur Verfügung. Bei synchronen Sprachen wird von der Zeit abstrahiert, was eine Trennung zwischen der eigentlichen Funktion und des zeitlichen Verhaltens zulässt. Zu den synchronen Sprachen gehören unter anderem Esterel [BC84], Lustre [HCRP91], SCADE [Est08], SyncCharts [And96] und SCCharts [vHMA+13a].

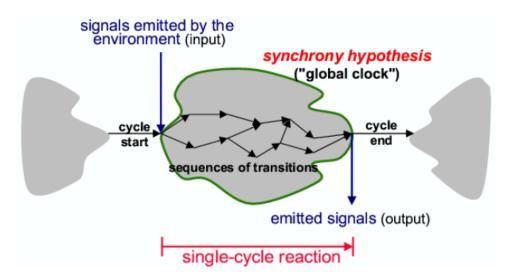

Synchrone Sprachen basieren auf synchronen Ausführungsmodellen, die die deterministische Ausführung von Programmen sicherstellen. Dem synchronen Ausführungsmodell liegt die Synchronizitätshypothese zugrunde, die folgende Eigenschaften beschreibt [PBdST05]:

#### ⊳ Perfekte Synchronizität

Ein System läuft in perfekter Synchronizität, wenn alle Prozesse gleichzeitig ablaufen und für die Berechnungen keine Zeit verbraucht wird. Das bedeutet, dass in dem selben Moment, in dem Eingaben gelesen werden, die Ausgaben berechnet und ausgegeben werden.

####

Zero-delay besagt, dass bei einem Zustandswechsel innerhalb eines Programms, von einem Zustand in seinen Folgezustand, keine Zeit verbraucht wird.

#### > Multiform notion of time

Bei der *Mutiform notion of time* wird von der physikalischen Zeit abstrahiert. Die Zeit wird durch eine Reihenfolge von Ereignissen bestimmt. Soll die Zeit durch die physikalische Zeit modelliert werden, können periodische Ereignisse gewählt werden, die zum Beispiel jede Sekunde auftreten.

Im synchronen Ausführungsmodell wird die Zeit in diskrete *Ticks* eingeteilt. Dabei werden zu Beginn des Ticks die Eingaben gelesen und am Ende eines Tick die Ausgaben produziert. Ein solcher Tick heißt *Makrotick* oder einfach *Tick*. Einem solchen Tick wird zunächst keine Ausführungszeit zugeschrieben, siehe Abbildung 1.1

**Abbildung 1.2.** Die Synchronizitätsshypothese (G. Luettgen, 2001)

(zero duration). Die Berechnung kann in einzelne Berechnungsschritte, sogenannte *Mikroticks* aufgeteilt, in denen die Ausgaben berechnet werden. In Abbildung 1.2 ist die Berechnung eines Ticks dargestellt.

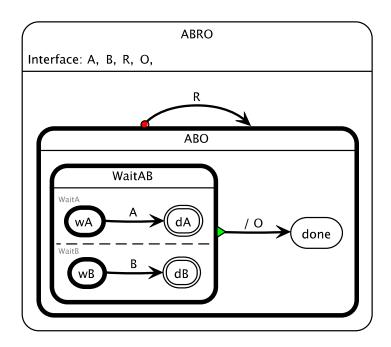

#### 1.1.1 SyncCharts

SyncCharts basieren auf den Statecharts von David Harel [Har87] und erweitern diese um die synchronen Eigenschaften wie Determinismus. Bei Statecharts handelt es sich im Grunde um hierarchische Mealy-Automaten mit Preemption und Kommunikationsmechanismen für nebenläufige Threads zur nebenläufigen Modellierung. Diese sind jedoch nicht deterministisch. SyncCharts hingegen basieren, wie Esterel, auf dem synchronen Ausführungsmodell von Berry, welches den Determinismus sicherstellt, und auf der Synchronizitätshypothese. SyncCharts ist eine grafische Modellierungssprache für synchrone Sprachen. Sie wurde 1996 von Charles André [And96] als ein grafisches Pendant von Esterel [BC84] vorgestellt. Um das Verständnis von SynchCharts zu erleichtern, ist in Abbildung 1.3 ein SyncChart gezeigt, welches nun näher erklärt werden soll.

Es handelt sich hierbei um das "Hello World" der synchronen Sprachen, das ABRO-Beispiel. ABRO verwendet die typischen Modellierungskomponenten von SyncCharts.

####

Bei Zuständen kann zwischen einfachen und *Makrozuständen* unterschieden werden. Einfache Zustände sind zum Beispiel der Zustand done in der Abbildung 1.3. Makrozustände beinhalten weitere SyncCharts Elemente, wie zum Beispiel der

#### 1. Einleitung

Abbildung 1.3. Das "Hello World" der SyncCharts — ABRO [Smy13]

Zustand WaitAB. Es können eine oder mehrere parallele Regionen in einem Makrozustand enthalten sein (siehe Zustand WaitAB). Ein Zustand kann optional als initialer Zustand (siehe Zustand wA) markiert sein (dicker Rand) oder als Endzustand (siehe Zustand dA) (doppelter Rand).

#### □ Transition

Transitionen werden verwendet, um von einem Zustand in einen Folgezustand zu wechseln, dabei können drei Transitionstypen unterschieden werden. Weak Transitions werden zum einfachen Zustandswechsel verwendet. Normal termination Transitions werden verwendet, um nebenläufige Regionen zusammenzuführen. Die normal termination Transition wird genommen, wenn alle Regionen terminiert sind. Sie werden durch einen grünen Pfeil gekennzeichnet. Strong abort Transitions unterbrechen sofort die Ausführung des Makrozustands und setzen die Ausführung an ihrem Zielzustand fort (Preemption). Sie sind mit einem roten Punkt gekennzeichnet. Transitionen können einen Trigger und ein Effekt besitzen, beide sind optional. Eine Transition kann nur genommen werden, wenn in einem Tick der Zustand aktiv ist von dem sie ausgeht und wenn der Trigger wahr ist. Damit sie genommen wird, muss sie weiterhin die höchste Priorität haben und darf nicht preemted werden. Prioritäten entscheiden, welche Transition genommen wird, wenn ein aktiver Zustand mehr als eine ausgehenden Transition besitzt die

wahr ist. Der Effekt wird ausgeführt, wenn die Transition genommen wird. So wird zum Beispiel die Transition vom Zustand wA zum Zustand dA genommen, wenn ein A registriert wurde. Ein O wird emittiert wenn die normal termination Transition von Zustand WaitAB genommen wird.

#### Signale

In SyncCharts werden Signale zur Kommunikation verwendet. Signale werden im äußersten Zustand, dem *Main State*, im Interface deklariert. Signale in SyncCharts unterliegen dem *Signalkohärenz Gesetz*, siehe Unterkapitel 1.1.1. Sie haben einen Signalstatus der in einem Tick entweder present oder absent ist (*pure Signals*), wertbehaftete Signale (*valued Signals*) haben darüber hinaus noch einen zusätzlichen Wert, der als Zustand über Tickgrenzen hinweg erhalten bleibt. Der Status eines Signals wird auf present gesetzt, wenn es emittiert wird. Wertbehaftete Signale besitzen einen Typ, zum Beispiel Integer oder Boolean. Signale können als Ein- und Ausgangssignale definiert werden, um mit der Umgebung zu interagieren. Ein Signal kann auch ein lokales Signal sein, diese können im jeweiligen Zustand deklariert werden.

####

Regionen dienen zu Spezifikation von Nebenläufigkeit in SyncCharts. Sie müssen einen initialen Zustand besitzen. Regionen können Endzustände besitzen. Ist ein Endzustand einer Region aktiv, ist die Ausführung der Region beendet und sie terminiert.

In der Abbildung 1.3 sind einfache Zustände und hierarchische Zustände mit nebenläufigen Regionen zu sehen. Nachdem das SyncChart gestartet wurde, sind die beiden initialen Zustände wA und wB sowie WaitAB und ABO aktiv. Der Zustand WaitAB terminiert, wenn die beiden internen Regionen terminiert sind. Die beiden Regionen terminieren, wenn jeweils die Eingaben A beziehungsweise B registriert wurden. Wenn die Region WaitAB terminiert, wird die ausgehende Transition von WaitAB genommen und O emittiert. Im Zustand done bleibt die Ausführung stehen. ABO kann erneut gestartet werden, wenn das Signal R present ist. Das SyncChart kann zu jedem Zeitpunkt, unabhängig davon, in welchem Zustand sich das SyncChart befindet, mit dem Signal R neu gestartet werden.

Die Sprachen Esterel und SyncCharts basieren auf dem synchronen Ausführungsmodell von Berry [Ber02]. Die Berry Konstruktivität legt die Synchronizitätsshypothese und das Signalkohärenz Gesetz zugrunde. Das Signalkohärenz Gesetzt definiert, welche Status Signale in einem Tick besitzen dürfen:

#### 1. Einleitung

#### Signalkohärenz Gesetz

Ein Signal, ist in einem Tick nur present (vorhanden) und nur dann, wenn es in diesem Tick emittiert worden ist. Ein Signal ist im Normalfall absent (nicht vorhanden). Weiterhin kann ein Signal niemals in einem Tick beide Zustände annehmen.

#### 1.1.2 Sequentiell konstruktives Ausführungsmodell

Das synchrone Ausführungsmodell von Berry stellt Determinismus in einer nebenläufigen Programmierung zur Verfügung, jedoch mit einigen Einschränkungen. Es ist in der Berry Konstruktivität aufgrund des Signalkohärenz Gesetzes verboten, dass Signale in einem Tick mehrere unterschiedliche Status besitzen.

Das Signalkohärenz Gesetz beschränkt die Klasse der gültigen Programme. Eine Auflockerung des Gesetzes würde die Klasse gültiger Programme vergrößern. Durch diese Änderung müssten, um den Determinismus zu erhalten, weitere Ausführungseigenschaften eingehalten werden. Das Sequentiell Konstruktive Ausführungsmodell, vorgestellt in "Sequentially Constructive Concurrency — A conservative extension to the synchronous model of computation" [vHMA+13b] von von Hanxleden et al., löst die Einschränkungen der Berry Konstruktivität auf. In diesem Ausführungsmodell werden Variablen anstelle von Signalen für die Kommunikation verwendet. Variablen können mehrere Werte in einem Tick führen, solange für das Programm mindestens ein sequentielles statisches Schedule existiert und alle existierenden Schedules das gleiche Ausgabeverhalten nach sich ziehen. Es handelt sich dabei um eine Erweiterung der klassischen Berry Konstruktivität. Es werden weiterhin Signale unterstützt, so dass SyncCharts mit diesem Ausführungsmodell ebenfalls ausgeführt werden können. Eine deterministische Ausführung von Programmen ist durch das sequentiell konstruktive Ausführungsmodell weiterhin gewährleistet.

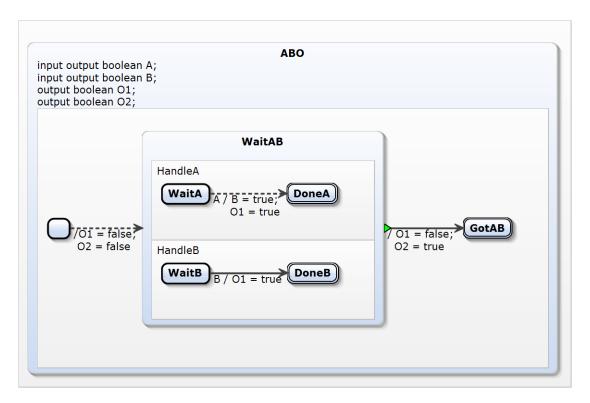

#### 1.1.3 SCCharts

Sequentially Constructive Charts (SCCharts) [vHMA<sup>+</sup>13a] stellen eine grafische Modellierungssprache dar, die auf dem sequentiell konstruktiven Ausführungsmodell beruht. Im Gegensatz zu SyncCharts werden in einem SCChart Variablen verwendet. Variablen können mehrere Werte in einem Tick besitzen. Ein SCChart ist konstruktiv, wenn es syntaktisch korrekt ist und mindestens ein sequentielles Schedule existiert. Alle existierenden Schedules müssen in jedem Tick das selbe deterministische Verhalten aufweisen.

SCCharts bestehen, wie SyncCharts, aus Zuständen, Transitionen und Regionen. Es gibt eine minimale Anzahl an Modellierungskomponenten, die sogenannten Core SCCharts, mit denen vollständige SCCharts modelliert werden können. In einer erweiterten Version, den extended SCCharts, stehen syntaktisch angereicherte Elemente zur Verfügung, mit denen komplexere Sachverhalte einfacher modelliert werden können. Eine detailliertere Erklärung der SCCharts wird in Abschnitt 4.1.2 gegeben.

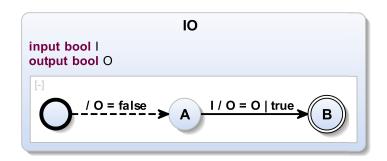

Abbildung 1.4. Das ABO Beispiel modelliert als Core SCChart

In Abbildung 1.4 ist ein Core SCCharts Beispiel gezeigt. Es werden in SCCharts ähnliche Modellierungskomponenten verwendet wie in SyncCharts. Eine genaue Erklärung zum Beispiel ist in Abschnitt 4.1.2 zu finden.

## 1.2 Aufgabenstellung

Die Programmierung eingebetteter reaktiver Systeme ist, aufgrund der Anforderung, dass trotz Nebenläufigkeit der Determinismus garantiert sein muss, eine Herausforderung. Sprachen wie Esterel oder SCCharts sind dem Programmierer behilflich, Systeme mit solchen Anforderungen zu entwickeln. Die entwickelten Programme können zum Beispiel mit Hilfe von Transformationen von synchronen Sprachen zu C oder Java auf Mikrocontroller programmiert werden. Bei reaktiven Systemen muss es sich jedoch nicht nur um Mikrocontroller gesteuerte Systeme handeln. Gerade, wenn schnelle oder massiv parallele Anforderungen an ein reaktives System gestellt werden, kommen FPGAs zu Einsatz. An die Entwicklung hochintegrierter paralleler Schaltkreise für FPGAs, werden spezifische Anforderungen gestellt. Ein Problem besteht darin, dass gerade in der VHDL Programmierung "echte" Parallelität vorherrscht und sequentielle Ausführungen abgebildet werden müssen. Ebenso ist die deterministische Programmierung von Schaltkreisen eine sehr komplexe Aufgabe, da

#### 1. Einleitung

neben der allgemeinen Schwierigkeit der parallelen Programmierung, noch zeitliche Aspekte wie Signallaufzeiten auftreten.

Für die Hardwaresynthese von SCCharts gibt noch keine direkte Transformation. In dieser Arbeit soll eine Lösung präsentiert werden, mit der SCCharts in einen Hardware Schaltkreis übersetzt werden können, der das selbe deterministische Verhalten aufweist wie das SCChart. SCCharts werden in einem ersten Schritt, mit den von Steven Smyth entwickelten Transformationen [Smy13], in ein sequentielles Programm übersetzt. In der Hardwareprogrammierung handelt es sich jedoch überwiegend um eine parallel Programmierweise. Damit die sequentielle Ausführung des Programms in Hardware umgesetzt werden kann, müssen die Datenabhängigkeiten zwischen einzelnen sequentiellen Anweisungen aufgelöst werden. Des Weiteren ist eine gesonderte Betrachtung der Ein- und Ausgabevariablen eines SCCharts bei der Hardwaresynthese notwendig. Für Ein- und Ausgabewerte müssen Mechanismen entwickelt werden, damit VHDL-Signale zum richtigen Zeitpunkt gelesen und geschrieben werden. Da Signalwerte bei Schaltkreisen flüchtig sind, muss eine Möglichkeit geschaffen werden, den Zustand, in dem sich ein SCChart befindet, in Hardware persistent abzubilden. Ebenso werden Techniken benötigt, die die Berechnungen des Schaltkreises starten und gegebenenfalls auch zurücksetzen. Diese Arbeit stellt für die vorgestellten Problemstellungen Lösungen bereit, um somit SCCharts auf Hardware auszuführen zu können. Da die Validierung von Schaltkreisen äußerst komplex ist, müssen Möglichkeiten geschaffen werden, diese zu validieren. Die Arbeit stellt einen Regressionstest vor, mit dem automatisch eine beliebige Anzahl an SCCharts-Transformationen getestet werden kann, um eine korrekte Transformation von SCCharts zu Hardware sicherzustellen.

#### 1.3 Aufbau der Arbeit

Die vorliegende Arbeit, die im weiteren Verlauf vorgestellt wird, ist wie folgt organisiert:

In Kapitel 2 werden verschiedene Konzepte der Codegenerierung vorgestellt. Das Hauptaugenmerk liegt dabei auf Transformationen von sequentiellen textuellen Sprachen, wie C oder Java, und synchronen Sprachen, wie Esterel und SyncCharts, zu einer Hardwarebeschreibungssprache. Die Konzepte werden vorgestellt und Unterschiede zur vorliegenden Arbeit genannt.

Kapitel 3 beschreibt die in dieser Arbeit verwendeten Technologien. So wird das auf Eclipse basierende Projekt KIELER vorgestellt und die Technologien Xtend, JUnit und VHDL eingeführt. Ebenso werden das Entwicklungswerkzeug ISE und die Simulationsumgebung ISim präsentiert.

Die Konzepte und Ideen zweier möglicher Lösungsansätze werden in Kapitel 4 präsentiert. Dazu werden zu Beginn das sequentiell konstruktive Ausführungsmodell sowie die Sprachen SCChart und SCL vorgestellt. Nachfolgend werden zwei Ansätze

für die Transformation von SCCharts zu VHDL präsentiert.

In Kapitel 6 werden Details zur Implementierung in dem KIELER-Projekt vorgestellt. Dies umfasst die Organisation der benötigten Transformationen in die verschieden Java und Xtend basierten Plugins in Eclipse, sowie eine allgemeine Beschreibung der Transformationen.

Eine automatische Validierung der Transformationsergebnisse wird in Kapitel 5 vorgestellt. Nachdem ein Format zum Testen von SCCharts dargelegt wurde, wird eine Möglichkeit zum Testen synthetisierter Schaltkreise mit dem Xilinx Tool ISim erläutert. Nach der Vermittlung der Idee des Tests, wird ein automatischer Test zum Überprüfen mehrerer Modelle präsentiert.

Ein Vergleich der beiden in Kapitel 4 vorgestellten Lösungsansätze wird in Kapitel 7 durchgeführt. Dort werden neben der Chipauslastung des FPGAs auch die Ausführungsgeschwindigkeiten der beiden Ansätze miteinander verglichen.

Im letzten Kapitel, Kapitel 8, wird die Arbeit in einer kurzen Zusammenfassung rekapituliert und weiterführende Ideen werden vorgestellt.

## **Verwandte Arbeiten**

Die Synthese von Hardware aus den unterschiedlichsten Programmiersprachen ist ein beliebtes Forschungsumfeld. Die Verwendung bekannter Programmiersprachen oder abstrakter Modellierungssprachen zur Synthese von Hardware, erleichtert es Programmierern aus dem Softwareumfeld Schaltkreise zu entwickeln. In diesem Abschnitt der Arbeit werden Sprachen, die sich für die Hardwaresynthese eignen, vorgestellt und mit dem hiesigen Ansatz verglichen.

## 2.1 Softwaresynthese aus SyncCharts

Der Statechart Dialekt SyncCharts ist speziell für die Entwicklung und Programmierung deterministischer reaktiver eingebetteter Systeme entwickelt worden. Bei eingebetteten Systemen handelt es sich meistens um Systeme die von einem Mikrocontroller oder einer sonstigen Hardware gesteuert werden. Sie werden in der Regel mit der Programmiersprache C programmiert. Die grafische Repräsentation von SyncCharts muss zuvor in ein äquivalentes C Programm transformiert werden, bevor der Controller das Programm ausführen kann. Dabei müssen deterministische Nebenläufigkeit und Preemption erhalten bleiben. Von Hanxleden stellt *SyncCharts in C (SC)* [vH09] vor, um diese Eigenschaften zu erhalten. Ein leichtgewichtiger Ansatz mit dem C Programme mit Determinismus, Nebenläufigkeit und Preemption realisiert werden können. SC besteht dabei aus einer kleinen Anzahl an C Makros.

Traulsen, Amende und von Hanxleden stellen einen Weg vor, SyncCharts zu SC zu transformieren [TAvH11]. Der Vorteil der Transformation spiegelt sich in der Lesbarkeit und in der Strukturerhaltung zwischen dem SyncChart und dem C Code wider.

Ebenso können SyncCharts in Java abgebildet werden. Da mit Java nur schwer deterministische Nebenläufigkeit realisiert werden kann, stellen Motika, von Hanxleden und Heinold *Synchronous Java (SJ)* [MvHH13] vor, mit dem deterministische Nebenläufigkeit umgesetzt werden kann. SyncCharts können somit in SJ realisiert werden.

SC und SJ stellen die Möglichkeit bereit, mit den Programmiersprachen C und Java, ein deterministisches Verhalten zu programmieren, sie sind dabei keine eigenständigen Sprachen. Damit die vorgestellten Ansätze für die Hardwaresynthese verwendet werden könnten, müssen SyncCharts in einer weiteren Transformation

#### 2. Verwandte Arbeiten

von C bzw. Java in Hardware übersetzt werden. Es gibt Übersetzungen von Sprachen wie C oder Java zu Hardware. Einige Ansätze werden in den folgenden Kapiteln präsentiert.

### 2.2 Hardwaresynthese

Die Herstellung hochintegrierter Schaltkreise ist aus der heutigen Elektronikbranche nicht wegzudenken. Früher wurden Schaltungen von Hand erstellt. Mit der Entwicklung von Hardwarebeschreibungssprachen wie VHDL und Verilog können Schaltungen in Software erstellt, simuliert und getestet werden. Ein großer Vorteil dabei ist die Verkürzung von Entwicklungs- und Produktionszyklen.

Die Programmierung schneller und komplexer Schaltungen für Hardware birgt besondere zeitliche Anforderungen. Bei der herkömmlichen Programmierung muss in der Regel das Zeitverhalten eines Programms nicht berücksichtigt werden und Nebenläufigkeiten werden in Form von Threads programmiert. In der Hardwaresynthese hingegen wird der Quellcode parallel ausgeführt. Um Programmierern den Einstieg und die Programmierung in der Hardwarebeschreibung zu erleichtern oder ihn sogar zu umgehen, wird an verschiedenen Möglichkeiten geforscht, C, Java und andere Programmiersprachen zu synthetisieren. Des Weiteren werden Beschreibungssprachen entwickelt, die sich wie C programmieren lassen, jedoch direkt in Hardware übersetzt werden können. Die Forschung ist ebenfalls interessant für Hardware-Software-Co-Design [DMG97]. Im folgenden Verlauf werden einige Ansätze zur Hardwaresynthese aus den Sprachen C und Java vorgestellt.

#### 2.2.1 Hardwaresynthese aus den Sprachen C und Java

Die Programmiersprache C ist unter anderem dafür ausgelegt, Code für Ein- und Mehrkernprozessoren zu programmieren. C ist nicht dafür entwickelt worden, um Schaltkreise zu erstellen. In Hardware werden strukturelle Informationen wie Pin/Port-Beschreibungen benötigt. Ebenso ist die Hardwareprogrammierung eine überwiegend parallele Programmierweise, welche C nicht direkt zur Verfügung stellt. Weiterhin fehlen in solchen Sprachen Konstrukte, um Zeitverhalten abbilden zu können, wie zum Beispiel das einer Variablen, nach einer Zeit t, ein Wert zugewiesen wird. De Michile beschreibt in seinem Artikel "Hardware Synthesis from C/C++ Models" [DM99] solche fehlenden Eigenschaften und Probleme.

Stephen A. Edwards stellt in seinem Artikel "The Challenges of Hardware Synthesis from C-like Languages" [Edw05] einige Sprachen vor, welche C sehr ähnlich sind, sich jedoch zur Hardwarebeschreibung eignen. Stroud et al. präsentieren die Sprache Cones [SMP88], die jede C-Funktion in einen kombinatorischen Block in Hardware übersetzt. Cones implementiert unter anderem bedingte Sprünge, Schleifen und Arrays.

HardwareC [KLM90] ist eine Beschreibungssprache für das Verhalten von Hardware. Es können strukturelle und hierarchische Beschreibungen vorgenommen werden. HardwareC basiert auf der Programmiersprache C und wurde unter anderem, um Beschreibungen für nebenläufige Prozesse, Message Passing und das explizite Erstellen von Prozeduren, erweitert.

C2Verilog [SP98b, SP98a] stellt Transformationen von C zu Verilog bereit. Es wird ein Großteil des ANSI C-Standards unterstützt. Beispielsweise werden Pointer, Rekursionen, dynamische Speicherallozierung und weitere C-Konstrukte transformiert.

Java ist heutzutage eine der am weit verbreitetsten Programmiersprachen und es liegt nahe, ebenfalls Hardwaresynthese aus Java zu betreiben.

T. Kuhn und W. Rosenstiel [KR00] verwenden die objektorientierte Sprache Java, mit der Erweiterung *JavaBeans*. Sie analysieren iterativ alle Threads in einem Java Quellcode. Jeder Thread wird in einem Kontrollflussgraphen abgebildet, der wiederum in einen VHDL-Prozess transformiert wird. Die generierten VHDL-Prozesse können anschließend synthetisiert werden.

Cardoso und Neto [CN99] analysieren hingegen Java-Byte-Code und generieren Quellcode für Hardware-Software-Co-Design. Aus dem Byte-Code heraus werden alle Abhängigkeiten innerhalb des Quellcodes und die parallelen Programmregionen ermittelt. Programmteile, die in Hardware ausgeführt werden sollen, werden synthetisiert und auf einer rekonfigurierbaren Hardware ausgeführt.

Die Transformation von herkömmlichen Programmiersprachen zu Hardware wurde hier nicht verwendet, da bei der Transformation zur Hardware Probleme wie Zeitverhalten und Parallelität gesondert betrachtet werden müssen [DM99]. Weiterhin gehen über diesen Weg, SCCharts zum Beispiel nach SC und anschließend mit einer der vorgestellten Möglichkeiten zu synthetisieren, die strukturelle Ähnlichkeit verloren, was eine Validierung zusätzlich erschwert.

#### 2.2.2 Esterel

Esterel [Ber00, BC84] ist eine synchrone imperative Programmiersprache. Sie ist dafür konzipiert, reaktive Systeme mit deterministischem Verhalten zu programmieren. Entwickelt wurde sie, um kontrolldominierte Software bzw. Hardware zu entwerfen. Esterel basiert auf einem streng formalen Modell und auf der synchronen Hypothese [BC84]. Das synchrone Ausführungsmodell zerlegt die Zeit in diskrete Schritte, die sogenannten *Ticks*. Das zeitliche Verhalten und die Funktionalität können so voneinander getrennt werden. Die Esterel Befehle lassen sich in zwei Gruppen einteilen. Es gibt instantane und verzögerte Befehle. Verzögerte Befehle wie zum Beispiel pause beschreiben Tickgrenzen. Ein *Tick* endet an solchen Befehlen. Während loop, emit (setzt ein Signal) oder present (testet, ob ein Signal vorhanden ist) instantane Befehle sind. Esterel-Programme werden durch Eingaben gesteuert. Ein Esterel-Programm wartet somit auf Eingabesignale und berechnet daraufhin die

#### 2. Verwandte Arbeiten

zugehörigen Ausgabesignale. Der folgende Text soll eine Idee darüber vermitteln, wie Schaltkreise aus Esterel-Programmen transformiert werden können.

#### Schaltkreissemantik

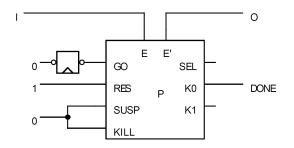

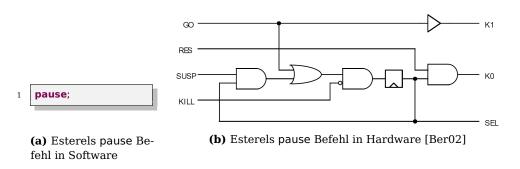

Esterel ist so konzipiert, dass aus einem Esterel-Programm sowohl Software als auch Hardware generiert werden kann. Für die Esterel-Semantik gibt es mehrere Formalisierungen [BC84]. Für die Hardwareentwicklung ist die Schaltkreissemantik von Bedeutung. Die Transformation ist strukturell, d.h. für jeden Basisbefehl wird zunächst ein äquivalenter Schaltkreis erzeugt. Die einzelnen Schaltkreise werden mit Hilfe von zusätzlichen Gattern und Schaltdrähten, siehe Abbildung 2.1, zu einem funktionierenden Schaltkreis verbunden [Ber02], der das Verhalten des Programms in Hardware widerspiegelt.

Jedes beliebige Esterel-Programm P, ein Beispiel ist in Listing 2.1 gezeigt, wird in einen Programmblock übersetzt. Ein Block besteht aus der folgenden Schnittstellenbeschreibung: E sind Eingaben von der Umgebung, E' sind Ausgaben an die Umgebung, RES setzt die Ausführung des Blocks fort, SUSP suspendiert die Ausführung des Blocks, KILL setzt die internen Register auf Grund eines Abbruchs zurück und SEL signalisiert, dass ein Block auf eine Weiterausführung wartet (zum Beispiel pause). Der Eingang GO startet die Ausführung eines Blockes und Kn,  $n \in \mathbb{N}$  signalisieren, wie der Block beendet wurde, der sogenannte *Completions Code*. Die verschiedenen Completions Code zeigen an, wie der Block terminiert, K0: der Block terminiert, K1: eine pause terminiert, Kn mit n>1: die Ausführung des Blockes wurde abgebrochen.

**Abbildung 2.1.** Allgemeiner Esterel Hardware Block [Ber02]

**Listing 2.1.** Esterel Software Modul

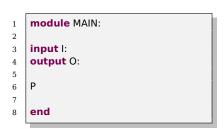

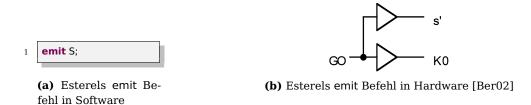

Die Abbildung 2.2 zeigt, wie ein Signal in Esterel emittiert wird. Das GO Signal startet die Ausführung und setzt das Signal s' auf true, es wird emittiert. Da der emit Befehl instantan ist, wird der *Completion Code* KO ebenfalls gesetzt. Abbildung 2.3 zeigt die Umsetzung eines pause Befehls in Hardware. Das Besondere an einem pause Befehl ist das Register, welches nach Erreichen der pause gesetzt wird, damit die Ausführung im nächsten *Tick* entsprechend fortgesetzt wird. Die Befehle eines

Abbildung 2.2. Der Esterel emit Befehl in Soft- und Hardware

Abbildung 2.3. Der Esterel pause Befehl in Soft- und Hardware

Esterel-Programms werden in die einzelnen Schaltungen übersetzt und im nächsten Schritt zu einem vollständigen Schaltkreis verbunden.

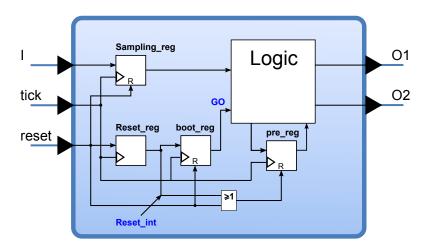

Mit Esterels Schaltkreissemantik ist es möglich, konstruktive Esterel-Programme in verzögerungsunabhängige Hardware zu übersetzen [Ber00]. Mit Esterel können SyncCharts abgebildet werden. Da SCCharts auf einem anderem Ausführungsmodell beruhen, wurde die Schaltkreissemantik nicht für die Synthese von SCCharts verwendet. Die Idee, dass für pause-Anweisungen Register verwendet werden, um Tickgrenzen zu beschreiben, wurde allerdings in dieser Transformation verwendet.

#### 2.2.3 Hardwaresynthese aus Statecharts

An der Hardwaresynthese von *Statecharts* [Har87] wurde ebenfalls geforscht. D. Harel und D. Drusinsky verwenden Statecharts zur Hardwarebeschreibung und zur Synthese von digitalen Schaltungen [DH89]. Sie verwenden dabei einzelne Automaten, die in Hardware umgesetzt werden. Zusammengeschlossen in einem Automaten-Baum bilden die einzelnen Automaten das Verhalten des Statecharts ab. Da Statecharts ein nichtdeterministisches Verhalten besitzen, eignet sich diese Synthese nicht für die Transformation von SCCharts.

### 2.3 Kiel Esterel Processor

Die Modellierungssprache Esterel kann nach Software oder Hardware übersetzt und ausgeführt werden. Dabei handelt es sich um zwei herkömmliche Ansätze. Ein weiterer Ansatz ist es, Esterel auf einem spezialisierten Prozessor, einem reaktiven Prozessor, auszuführen. Xi und von Hanxleden stellen den reaktiven Kiel Esterel Processor (KEP) [LvH06, LvH05] vor, dessen Befehlssatz eng an Esterel angelehnt ist. Basierend auf dem Prozessor hat sich Starke in seiner Diplomarbeit [Sta09] damit auseinander gesetzt, Safe State Machines (SyncCharts) auf diesem Prozessor auszuführen.

Für den KEP können nur eine bestimmte Teilmenge an zykelfreien Esterel Programmen verwendet werden [Gäd07]. Da der Prozessor an die Esterelbefehle angelehnt ist, können Esterel Befehle selbst direkt auf dem Prozessor ausgeführt werden. Die Auswertung komplexer Ausdrücke stellt sich als aufwändiger heraus. Gädtke, Traulsen und von Hanxleden präsentieren einen HW/SW Co-Design Ansatz [GTvH07] in dem komplexe Ausdrücke in Hardware transformiert und zur Ausführung ausgelagert werden.

Bei dem KEP handelt es sich um eine spezialisierte Hardware, die stark an Esterel angelehnt ist. Um eine möglichst große Flexibilität der späteren Hardware zu wahren, hat sich dieser Ansatz nicht als eine Möglichkeit herausgestellt. Ebenso können aufgrund dessen, dass die Berry Semantik im KEP zugrunde liegt, Variablen in SCCharts nicht mehrere Werte in einem Tick besitzen, wenn sie ausgeführt werden.

## 2.4 Das Electronic Design Interchange Format

Das Electronic Design Interchange Format (EDIF)<sup>1</sup> ist ein standardisiertes, maschinenlesbares Format, welches zum Austausch von Netzlisten und Schaltplänen verwendet wird. Es wurde zuletzt in der Version 4 0 0 im August 1996 durch die International Electrotechnical Commission (IEC) standardisiert. 1980 besaß die Industrie eine Reihe von Formaten, in denen die Unternehmen ihre Daten vorhielten. Das EDIF-Format wurde als neutrales Format entwickelt, um die Anzahl der Konvertierungen der Daten, die zum Austausch nötig waren, zu minimieren. Das EDIF-Format hat bis heute Bestand und wird zum Beispiel von der Firma Xilinx unter anderem zur Synthese [Inc12a] und zur Analyse des Stromverbrauchs synthetisierter Schaltkreise [SKB02] verwendet.

Die Informationen, die EDIF bereitstellt, können in zwei Gruppen eingeteilt werden [LK93]: allgemeine Design-Informationen und Informationen zur Repräsentation einer Zelle. Die Design-Informationen stellen Daten zur hierarchischen Sicht, zur grafischen Repräsentation, zur Verbindung von Einzelkomponenten und zum Hersteller/Eigentümer bereit. In den Zell-Informationen werden Verbindungsinformationen und Informationen zum Zeitverhalten gespeichert, sowie Daten zum Schaltplan

<sup>&</sup>lt;sup>1</sup>http://www.edif.org

```

(Cell NAND2

(View Topological Logic

2

(Interface

3

(Declare (INPUT PORT a b) (OUTPUT PORT z))

4

5

(Body

6

(Figure Group SchematicSymbol

(shape (20 0) (arc (40 0) (60 20) (40 40)) (20 40))

8

(circle (60 2]) (70 20))

9

10

(PortImplementation a (Figure Group SchematicPort

11

(Path (0 30) (20 30))))

12

(PortImplementation b (Figure Group SchematicPort

13

(Path (0 10) (20 10))))

14

(PortImplementation z (Figure Group SchematicPort

15

16

(Path (70 20) (90 20))))

17

(Permutable a b)

18

19

(Contents

20

21

(Instance Nand2Primitive)

22

23

(View Physical

24

25

(Interface

(Declare (INPUT PORT a b) (OUTPUT PORT z))

26

(Body (Figure Group MetalBlockage (Rectangle .... )))

27

(PortImplementation b (Figure Group Poly . . . . . ))

28

29

(Permutable a b)

30

)

31

32

33

(Figure Group Metal (Path ...) (Polygon ...) ...)

34

35

(Figure Group Poly (Path ...) (Path ...) ...)

36

37

38

)

39

```

(a) EDIF Codeausschnitt

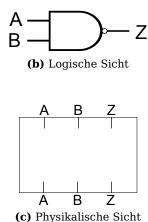

**Abbildung 2.4.** EDIF Codeausschnitt eines NAND-Gatters inkl. der logischen und physikalischen Sicht des Gatters [Cra84]

selbst. Mittels EDIF können somit elektronische Schaltungen abgebildet, gespeichert und ausgetauscht werden. Aus dieser Beschreibung kann nachfolgend Hardware synthetisiert werden.

Abbildung 2.4 zeigt einen Ausschnitt aus einer EDIF-Beschreibung eines *NAND2*-Gatters, ebenso wie die logische und physikalische Repräsentation. Auf die genaue Erläuterung wird hier verzichtet, die Abbildung soll die niedrige Abstraktionsebene und die Komplexität von EDIF darstellen.

EDIF dient zum Erzeugen von Schaltkreisen auf einem niedrigen Abstraktionsniveau. Ziel dieser Arbeit ist es jedoch, auf höheren Abstraktionsebenen zu arbeiten. VHDL bietet ein solches Niveau, weshalb diese Hochsprache zur Beschreibung von digitalen Schaltkreisen verwendet wurde und nicht das EDIF.

# Verwendete Technologien

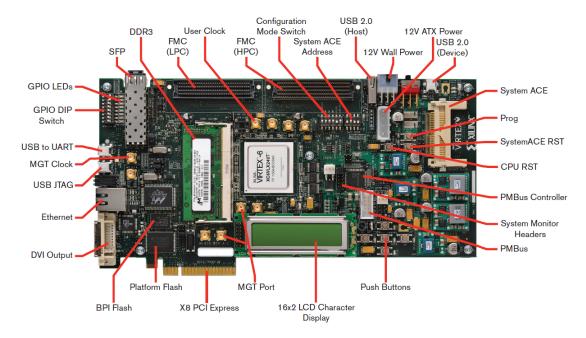

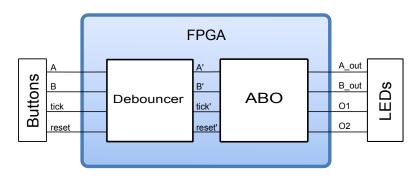

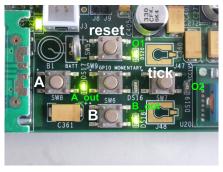

Im folgenden Kapitel werden die verwendeten Technologien für die Implementierung vorgestellt. Das auf Eclipse basierende Projekt Kiel Integrated Environment for Layout Eclipse Rich Client (KIELER), welches am Lehrstuhl Echtzeitsysteme und Eingebettete Systeme der Christian-Albrecht-Universität zu Kiel entwickelt wird, dient hierbei als Projektgrundlage. Das KIELER-Projekt stellt Funktionen und Transformationen bereit, die im Laufe der Arbeit verwendet wurden. Die Entwicklungsumgebungen Eclipse wurde verwendet, da die Entwicklung von KIELER auf Eclipse basiert. Die benötigten Transformationen von SCCharts zur Hardwarebeschreibung wurden in Xtend geschrieben und zum KIELER Projekt hinzugefügt. Als Hardwarebeschreibungssprache wurde die Very High Speed Integrated Circuit Description Language (VHDL) verwendet. Der von den Transformationen erzeugte VHDL Code wurde mit dem Xilin $x^1$ Tool Integrated Software Environment (ISE) nach Hardware übersetzt. Für Simulationszwecke und zum Sicherstellen der Richtigkeit der Transformationen, wurde das Simulationstool ISE Simulator (ISim), ebenfalls von der Firma Xilinx, verwendet. Die Tools der Firma Xilinx wurden verwendet, da am Lehrstuhl eine Evaluationsboard von Xilinx vorhanden war, auf dem Test durchgeführt werden konnten.

# 3.1 Eclipse

Eclipse<sup>2</sup> ist eine quelloffene Entwicklungsumgebung. Sie ist der Nachfolger von Visual Age for Java 4.0, dessen Quellcode im Jahr 2001 von IBM freigegeben wurde. Seit 2004 ist die Eclipse Foundation eine eigenständiges Unternehmen. Die wohl bekannteste Java integrierte Entwicklungsumgebung (IDE) Eclipse unterstützte ursprünglich nur die Entwicklung Java basierter Programme. Mittlerweile ist Eclipse jedoch vielseitig einsetzbar und unterstützt weitere Programmiersprachen wie C oder visuelle Sprachen wie die Unified Modeling Language (UML). Das Plugin Konzept von Eclipse trägt zur Vielseitigkeit bei. Eclipse selbst stellt nur eine Kernkomponente zur Verfügung, die die einzelnen Plugins lädt und verwaltet. Geladene Plugins erweitern die Funktionalität. Die Plugins und Eclipse sind in Java programmiert. Grafische Oberflächen werden mit SWT erstellt und für die Darstellung der GUI-Komponenten wird auf die nativen Komponenten des jeweiligen Betriebssystems zurückgegriffen.

<sup>1</sup>http://www.xilinx.com/

<sup>&</sup>lt;sup>2</sup>http://www.eclipse.org/

# 3. Verwendete Technologien

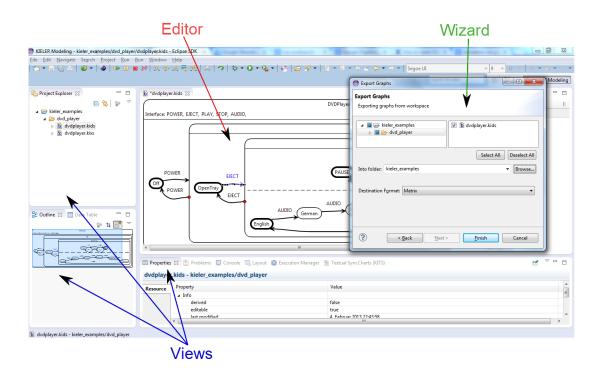

Abbildung 3.1. Eine Perspektive einer Eclipse Workbench [Har13]

Somit stellt Eclipse eine Rich Client Platform (RCP) zu Verfügung, die durch gezieltes Laden verschiedener Plugins auf die Lösung verschiedenster Probleme zugeschnitten werden kann. Durch eine wohldefinierte Schnittstellenbeschreibung ist es ebenfalls möglich, Plugins anderer Hersteller zu laden und zu verwenden. Eclipse besteht dabei im Wesentlichen aus Sichten (Views), Editoren und Perspektiven, die in einer Workbench zusammengefasst werden. Eine Eclipse Workbench ist in Abbildung 3.1 zu sehen.

Bei Views handelt es sich um Fenster, die Informationen zum aktuellen Projekt liefern. Zu den Views zählen unter anderem der Projekt-Navigator, der Klassenexplorer und das Suchfenster. Die Editoren stellen die Möglichkeit bereit, Quellcode anzuzeigen und zu modifizieren. Eclipse stellt in der Regel für jede Programmiersprache einen eigenen textuellen oder grafischen Editor zu Verfügung. Die Anordnung und Auswahl angezeigter Views und Editoren kann frei gewählt werden. Diese Anordnung und Sichtbarkeit wird in Eclipse als Perspektive bezeichnet. Perspektiven können beliebig gespeichert und geladen werden. Der in Abbildung 3.1 gezeigte Workbench stellt gleichzeitig eine Perspektive dar. In der Abbildung ist ebenfalls ein Wizard dargestellt. Benutzer können in einen Wizard strukturiert Informationen eingeben um eine bestimmte Aufgabe auszuführen. Der gezeigt Wizard ist zum Exportieren von Graphen.

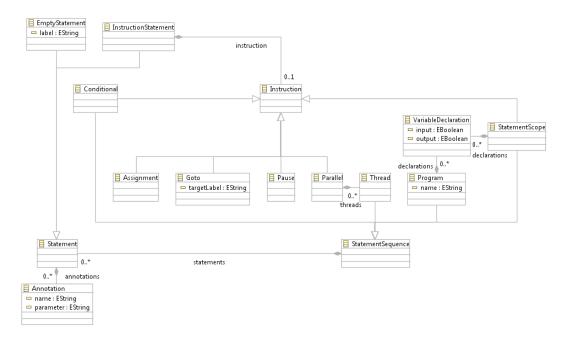

Abbildung 3.2. Beispiel eines Meta Modells — SCL Meta Modell

# 3.1.1 Eclipse Modeling Framework

Das Eclipse Modeling Framework (EMF)<sup>3</sup> ist ein Plugin für Eclipse. Es stellt in Eclipse die Möglichkeit bereit, modellgetrieben zu entwickeln. Das EMF wird verwendet, da SCCharts und die verwendeten Programmiersprachen in Modellen abgebildet sind.

Bei modellgetriebener Entwicklung handelt es sich um Techniken, die aus einem formal beschriebenen Model automatisch Software oder Hardware generiert. Das EMF generiert aus einem in XML Metadata Interchange (XMI) spezifiziertem Modell Java Code. Die erzeugten Klassen spiegeln das Modell in Java wider. Es wird ebenso Quellcode zum Anzeigen und zum Editieren das Modells generiert. Dabei besteht EMF im Wesentlichen aus drei Komponenten: core EMF framework, EMF.Edit und EMF.Codegen.

In EMF muss jedes Modell einem Meta-Modell entsprechen. Ein Meta-Modell ist eine abstrakte Syntax mit der Modelle beschrieben werden können. In Abbildung 3.2 ist ein Meta-Modell von SCL gezeigt. SCL ist eine textuelle Sprache zum Beschreiben von SCCharts. Die *core EMF framework* Komponente stellt unter anderem das Meta-Modell, eine effiziente API zum Manipulieren, sowie eine Serialisierung im XMI Format zum persistenten Speichern von Modellen bereit. Editoren für ein Modell können mit *EMF.Edit* erstellt werden. Ein Editor mit grafischer Oberfläche und vollem Funktionsumfang kann mit *EMF.Codegen* erzeugt werden.

<sup>&</sup>lt;sup>3</sup>http://www.eclipse.org/modeling/emf/

# 3. Verwendete Technologien

```

3⊖ class Templates {

{\tt def} \ {\tt createVhdlComponent(String} \ {\tt componentName,} \ {\tt boolean} \ {\tt setReset)} \{

COMPONENT HALBADDIERER

component «componentName»

PORT( A: IN std logic;

2

B: IN std_logic;

reset: IN std logic;

10

«IF(setReset)»

4

reset: in std_logic;'''»

S: OUT std logic:

5

«ENDTE»

Cout: OUT std logic );

S: out std_logic;

Cout: out std_logic );

END COMPONENT

end component;

16

18 }

```

Abbildung 3.3. Beispiel für das Xtend Template

(b) Erzeugter VHDL Code

(a) Xtend Template Code

# 3.1.2 Xtend

Xtend<sup>4</sup> ist ein flexibler und ausdrucksstarker Dialekt von Java. Beim Compilieren wird Xtend-Quellcode in lesbaren Java-Quellcode übersetzt. Xtend ist dabei vollständig kompatibel zu Java.

Bei Xtend handelt es sich um eine streng getypte Programmiersprache die Java's Typsystem vollständig unterstützt. Ebenso können vorhandene Java Bibliotheken verwendet werden. Xtend erweitert Java und stellt hilfreiche Features, wie zum Beispiel Lambda-Ausdrücke, Operator-Überladung und Typen-Inferenz bereit.

Xtend kann in Eclipse integriert werden. Bei der Hardwaresynthese von SCCharts wird Xtend verwendet, um die benötigten Transformationen zu implementieren. Xtend eignet sich für Model zu Model (MtM) Transformation ebenso wie für die Erzeugung von textuellen Quellcode.

Die *Template Expressions* von Xtend stellen eine erweitertes String Konzept dar, die sogenannten *Rich Strings*. So bieten *Templates* die Möglichkeit Strings über mehrere Zeilen zu definieren, einen String in Abhängigkeit einer Bedingung oder mit Hilfe einer Schleife zu erstellen. Des Weiteren gibt es einen intelligenten Umgang mit Leerzeichen, welcher vorteilhaft für die Erzeugung textuell strukturierten, lesbaren Quellcodes ist.

Die *Templates* finden in dieser Arbeit Anwendung in der Generierung von VHDL-Quellcode. In Abbildung 3.3 werden beispielhaft die Funktion einiger *Templates* dargestellt. Die während der Programmierung eingefügten Leerzeichen werden auch im transformierten Quellcode abgebildet. Ein übersichtlicher und strukturierter Quellcode ist das Ergebnis.

<sup>&</sup>lt;sup>4</sup>http://www.eclipse.org/xtend/documentation.html

# 3.2 Das JUnit Framework

$JUnit^5$  ist ein Framework zum Testen von Java-Programmen. Er ist besonders für automatisierte Tests einzelner Klassen oder Methoden geeignet. Mittlerweile gibt es ähnliche Konzepte für viele andere Programmiersprachen. Bei einem JUnit-Test können nur zwei Ergebnisse entstehen, der Test ist bestanden oder fehlgeschlagen. Das wird mittels spezieller *Exceptions* signalisiert.

JUnit wurde verwendet, um die Transformationen automatisch zu testen. Für jedes zu testende SCChart muss eine Testdatei angefertigt werden, die Signale der Umgebung emittiert und erwartete Ausgabesignale das Modells überprüft. Model und Testdatei werden in einem JUnit-Test gegeneinander validiert. Dieser Test wurde mit mehreren Modellen und Testdateien unternommen, um die Richtigkeit der Transformationen während der Entwicklung zu gewährleisten.

# 3.3 Kiel Integrated Environment for Layout Eclipse Rich Client

Das Kiel Integrated Environment for Layout Eclipse Rich Client (KIELER) Projekt soll die Handhabung und den Umgang beim Designen komplexer grafischer modellbasierter Entwürfe vereinfachen. So steht zum Beispiel die ständige Entwicklung automatischer Layouts diverser grafischer Komponenten im Fokus. Ebenso ist die Entwicklung neuer Methoden und Konzepte für das Editieren und das Arbeiten an Modellen und die dynamische Visualisierung von Diagrammen ein Forschungsschwerpunkt. Die dynamische Visualisierung wird zum Beispiel für die Simulation von Diagrammen verwendet.

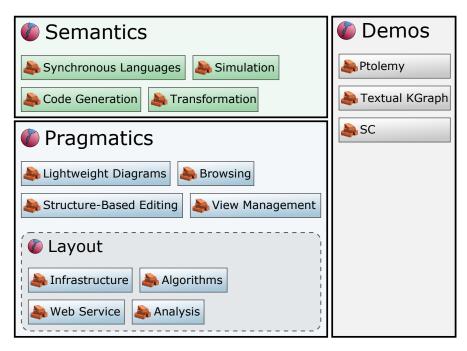

KIELER wird mit Hilfe von Eclipse entwickelt und basiert auf der Rich Client Platform. Dabei integriert KIELER einen Großteil an Modellierungsprojekten von Eclipse (EMF,GMF,Xtext, etc.). Bei KIELER handelt es sich um ein *Open-Source-Projekt*, welches unter der *Eclipse Public Licencse* entwickelt wird. Das KIELER-Projekt gliedert sich, wie in Abbildung 3.4 zu sehen, in die vier Teilgebiete *Semantics, Pragmatics, Layout* und *Demonstrators (Demos)* auf.

# Semantik

Das Teilgebiet der *Semantik* stellt eine Infrastruktur bereit, in der Ausführungssemantiken für Meta-Modelle definiert werden. Dabei kann es sich zum Beispiel um einen Simulator, basierend auf C oder Ptolemy<sup>6</sup>, handeln. Weitere textuelle oder grafische Simulatoren können über den KIELER Execution Manager (KIEM)<sup>7</sup> eingebun-

<sup>&</sup>lt;sup>5</sup>http://www.junit.org/

<sup>&</sup>lt;sup>6</sup>http://ptolemy.eecs.berkeley.edu/

$<sup>^7</sup> http://rtsys.informatik.uni-kiel.de/confluence/pages/viewpage.action?pageId = 328095$

# 3. Verwendete Technologien

Abbildung 3.4. Übersicht des KIELER Projektes [RK13]

den werden. Die Transformation von einer Quellsprache in eine andere Zielsprache gehört in den Bereich der Semantik. Die Transformationen von SCCharts zur Sequentially Constructive Language (SCL), welche in dieser Arbeit benötigt werden, gehören ebenfalls zur Semantik. Da es sich in dieser Arbeit ebenfalls um eine Transformation zwischen Sprachen handelt, ist diese Arbeit in das Teilgebiet der *Semantik* einzuordnen.

# **Pragmatik**

Die *Pragmatik* beschäftigt sich mit den praktischen Aspekten des Programmierens im Hinblick auf modellgetriebene Entwicklung (Model-Driven Engineering (MDE)) [Sch06]. Das beinhaltet das Erstellen und Modifizieren von Modellen sowie die Synthese verschiedener Sichten auf Modelle. Das ist zum Beispiel für Gruppen mit unterschiedlichen Interessen an einem Modell von Bedeutung. Strukturbasiertes Editieren von Modellen, die auf einer abstrakten Syntax beruhen, stellt zum Beispiel das Plugin KIELER Structure-based Editing (KSbasE) zur Verfügung. Damit ist es möglich, neue Elemente zu erstellen, sie zu bearbeiten, zu verbinden oder zu löschen.

KIELER Lightweight Diagrams (KLighD) stellt die Möglichkeit einer Synthese von Modellelementen zu einer grafischen Repräsentation zur Verfügung. Ziel von KLighD ist es, eine transiente grafische Repräsentation eines Modells zu generieren, welche den individuellen Ansprüchen des Modellierers entspricht.

Die *View-Management-*Komponente stellt eine dynamische Visualisierung für den Benutzer bereit. So erfährt ein Element eines Modells, welches ausgewählt wird, zum Beispiel eine optische Hervorhebung. Es werden diverse *Trigger* (z.B. Auswahl eines Elementes) in Effekte umgesetzt (z.B. Hervorhebung des Objektes).

# Layout

Die Forschungen im Bereich *Layout* sollen dem Benutzer das Erstellen und Editieren von Layouts erleichtern. Teilweise müssen verschiedene Änderungen an einem Layout gemacht werden, bevor ein neues Element einfügt werden kann. Zum Beispiel muss Raum für ein neues Element geschaffen werden. Das Weiteren müssen für ein übersichtliches und gut lesbares Layout einzelne Komponenten (Knoten und Kanten) manuell angeordnet werden. Diese Schritte benötigen Zeit und hindern den Entwickler an einem effektiven, schnellen Design.

Im Bereich *Layout* wird an Optimierungen für den Modellierer geforscht. So übernehmen automatische Layouts und Algorithmen diese Aufgaben. KIELER Infrastructure for Meta Layout (KIML) ist die Kernkomponente, sie stellt die Schnittstelle zwischen dem grafischen Editor und dem jeweiligen Layoutalgorithmus dar. Es werden sowohl Open-Source Layoutalgorithmen, als auch spezialisierte Algorithmen (KIELER Layouters (KLay)) bereitgestellt.

#### **Demonstrators**

Die *Demonstrators* beinhalten diverse Editoren. Die Editoren werden verwendet, um die entwickelten Technologien der anderen Teilbereiche zugänglich zu machen und zu validieren. Zu den Editoren zählen unter anderen der *Yakindu*-Editor [Har13], welcher den *ThinkCharts*-Editor ersetzt, zum Editieren von SyncCharts und der *KGraph*-Editor, zum textuellen Beschreiben von *KGraph*-Graphen.

# 3.4 Die Hardwarebeschreibungssprache VHDL

Eine Hardwarebeschreibungssprache ermöglicht es, digitale Systeme textuell zu beschreiben. Zwei bekannte Hardwarebeschreibungssprachen sind VHDL und Verilog. Verilog ist vergleichbar mit einer Programmiersprache wie C, und VHDL ist an Ada angelehnt. Die IEEE hat 1987 VHDL als einen IEEE-Standard festgelegt und Verilog im Jahr 1995.

VHDL entstand durch die US-amerikanische Regierung die 1980 die VHSIC-Initiative ins Leben gerufen hat. Sie sollte den technologischen Rückstand zwischen der Regierung und der Privatwirtschaft aufholen. Das US-Verteidigungsministerium forderte, dass alle entwickelten Schaltungen nach dem 30. September 1988 in VHDL dokumentiert sein mussten, damit war VHDL als Standard etabliert. Es wurde zum

# 3. Verwendete Technologien

Abbildung 3.5. Komponenten Sicht eines 2 Bit Addierers

ersten Mal 1987 durch die IEEE standardisiert. Die aktuelle Standardisierung, die weitere Sprachergänzungen enthält, ist von 1993.

# 3.4.1 Die Programmierung mit VHDL

VHDL dient zur textuellen Beschreibung von digitalen Systemen. Mit VHDL ist es möglich, Schaltkreise auf einer abstrakten Ebene zu beschreiben. So gibt es eine externe und eine interne Sicht auf die beschriebenen VHDL-Komponenten [Bha92]. Bei der externen Sicht handelt es sich um die Sicht, die die Schnittstellenbeschreibung widerspiegelt, über welche die Komponente mit anderen Komponenten kommunizieren kann. Die interne Sicht beschreibt das Verhalten bzw. die Struktur. Das Beispiel in Abbildung 3.5 soll die verschiedenen Sichten verdeutlichen.

Es handelt sich in dem Beispiel um einen Voll-Addierer (VA), der aus zwei Halb-Addierern (HA) besteht. Die interne Sicht eines Halb-Addierers beschreibt sein Verhalten, während die interne Sicht des Voll-Addierers die Struktur und das Verhalten des gesamten Addierers als Komponente beschreibt. Die externe Sicht des Voll-Addieres beschreibt hingegen die Schnittstellen, die die Komponente Voll-Addierer besitzt. Zur Schnittstellenbeschreibung gehören alle Ein- und Ausgabesignale (A, B, Cin, Cout und S) des Addierers. Mit VHDL ist es möglich, einzelne Komponenten untereinander zu verbinden, Komponenten mehrfach zu verwenden (siehe Halb-Addierer) und hierarchische Modelle zu entwickeln. Es werden durch VHDL somit Möglichkeiten zum verhaltens- und strukturbasierten Programmieren gegeben.

# 3.4.2 Simulation von Hardwarebeschreibungen